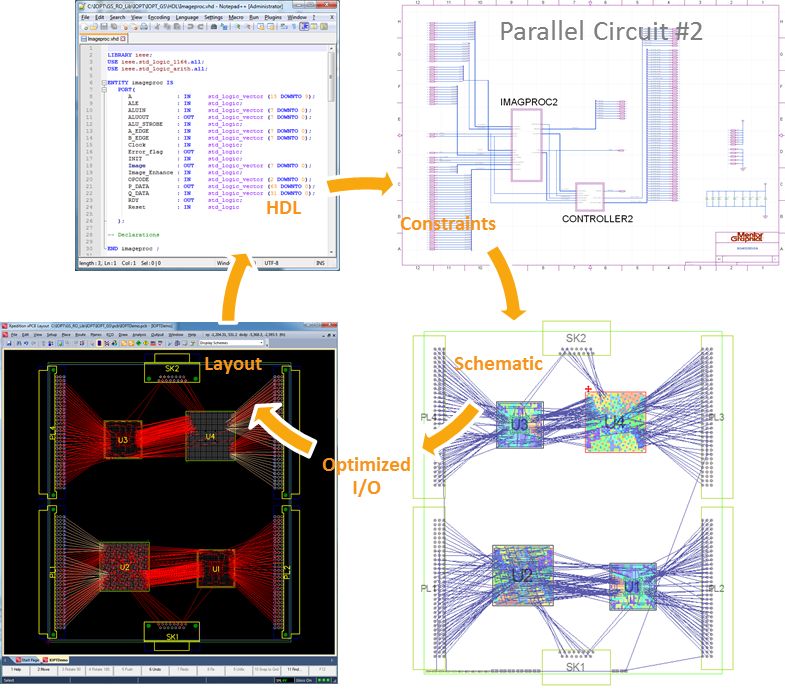

隨著電子產(chǎn)品的集成性及復(fù)雜度呈指數(shù)型增長,加上越來越苛刻的研發(fā)周期要求,給各種設(shè)計(jì)公司提出了難題。這其中FPGA的設(shè)計(jì)挑戰(zhàn)尤為突出。不斷增加的管腳數(shù)量,同一PCB上的多顆FPGA之間互連等等,面對(duì)這些挑戰(zhàn)如果還依照以往的手動(dòng)式設(shè)計(jì)流程,勢(shì)必會(huì)在激烈的市場(chǎng)競(jìng)爭(zhēng)中失去優(yōu)勢(shì)!Mentor公司針對(duì)這種實(shí)際應(yīng)用情況,提出了集成式管腳優(yōu)化方案,根據(jù)信號(hào)連接關(guān)系及器件位置擺放信息,自動(dòng)實(shí)現(xiàn)IO管腳優(yōu)化,在保證產(chǎn)品質(zhì)量的前提下,高效完成FPGA設(shè)計(jì)及優(yōu)化工作,在最短的時(shí)間內(nèi)使產(chǎn)品順利上市!

4大技術(shù)優(yōu)勢(shì):

1縮減設(shè)計(jì)成本:

減少過孔數(shù)量

節(jié)省PCB疊層數(shù)量

減少生產(chǎn)制造迭代次數(shù)

2縮短設(shè)計(jì)周期:

減少設(shè)計(jì)迭代次數(shù)

提升FPGA布線效率

快速優(yōu)化IO管腳,自動(dòng)生成器件symbol

3減少設(shè)計(jì)失誤:

杜絕器件symbol設(shè)計(jì)失誤

避免手動(dòng)更換IO管腳而造成的失誤

4提高產(chǎn)品質(zhì)量:

減少布線長度,提升信號(hào)質(zhì)量

-

FPGA

+關(guān)注

關(guān)注

1660文章

22412瀏覽量

636339 -

pcb

+關(guān)注

關(guān)注

4404文章

23878瀏覽量

424309

原文標(biāo)題:不容錯(cuò)過的研討會(huì) | 復(fù)雜FPGA高效設(shè)計(jì)及優(yōu)化方法

文章出處:【微信號(hào):gh_1a93bb3ab6f3,微信公眾號(hào):Mentor明導(dǎo)PADS】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

請(qǐng)問如何優(yōu)化芯片的功耗管理?

數(shù)字IC/FPGA設(shè)計(jì)中的時(shí)序優(yōu)化方法

程序運(yùn)行速度很慢如何優(yōu)化?

基于FPGA的高效內(nèi)存到串行數(shù)據(jù)傳輸模塊設(shè)計(jì)

復(fù)雜的軟件算法硬件IP核的實(shí)現(xiàn)

Altera Agilex 3 FPGA和SoC產(chǎn)品家族的性能分析

提高RISC-V在Drystone測(cè)試中得分的方法

蜂鳥E203內(nèi)核優(yōu)化方法

FPGA測(cè)試DDR帶寬跑不滿的常見原因及分析方法

吉時(shí)利數(shù)字源表2460:如何高效測(cè)量速度與性能優(yōu)化

【產(chǎn)品介紹】Altair HyperStudy拓?fù)?b class='flag-5'>優(yōu)化軟件

復(fù)雜FPGA高效設(shè)計(jì)及優(yōu)化方法

復(fù)雜FPGA高效設(shè)計(jì)及優(yōu)化方法

評(píng)論