據(jù)香港《南華早報》網(wǎng)站5月27日報道,現(xiàn)如今,市場上最先進的計算機芯片使用7納米晶體管。中國科學院微電子研究所微電子設備與集成技術領域的專家殷華湘說,他的團隊已經(jīng)研發(fā)出3納米晶體管——相當于一條人類DNA鏈的寬度,在一個指甲蓋大小的芯片上能安裝數(shù)百億個這種晶體管。

殷華湘說,晶體管變得越小,芯片上就能安裝越多的晶體管,這會讓處理器的性能顯著提升。晶體管是處理器的基本部件。殷華湘說,用3納米晶體管制造的處理器將會增加計算速度,并降低能耗。比如一位智能手機用戶可以整天玩需要大量計算能力的游戲,卻不需要為電池重新充電。

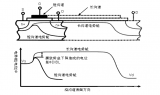

殷華湘說,他的團隊還必須克服一些重大障礙。他們的研究成果本月部分發(fā)表在同行評議雜志《電氣與電子工程師協(xié)會電子器件通訊》上。其中一個障礙是“波爾茲曼暴政”。路德維希·波爾茲曼是19世紀的奧地利物理學家。“波爾茲曼暴政”描述的是有關電子在一個空間中的分布問題。對芯片研發(fā)者來說,這意味著隨著更多較小的晶體管安裝到芯片上,晶體管所需電流產(chǎn)生的熱量將燒毀芯片。

報道稱,物理學家已經(jīng)為這個問題提供了解決辦法。殷華湘說,他的團隊使用一種稱為“負電容”的方法,這樣他們能用理論上所需最小電量的一半電量來為晶體管提供電力。這種晶體管實現(xiàn)商業(yè)應用可能要花幾年時間。該團隊正在進行材料和質量控制方面的工作。

殷華湘說:“這是我們工作中最激動人心的部分。這不僅是實驗室中的又一項新發(fā)現(xiàn)。它有著實際應用的巨大潛力。而我們擁有專利。”

報道稱,殷華湘說,這項突破將讓中國“在芯片研發(fā)的前沿同世界頭號角色進行正面競爭”。他說:“在過去,我們看著其他人競爭。現(xiàn)在,我們在同其他人競爭。”

據(jù)報道,中國還在研發(fā)一種原子大小(0.5納米)的晶體管,而其他國家已經(jīng)加入將3納米晶體管投入市場的競賽。

韓國三星公司說,它計劃到明年上半年完成3納米晶體管的研發(fā)。三星說,同7納米技術相比,用它的3納米晶體管制造的處理器只需用一半的電力,性能卻會提高35%。三星沒有說它預計這些芯片將于何時投產(chǎn)。

-

芯片

+關注

關注

463文章

54010瀏覽量

466138 -

晶體管

+關注

關注

78文章

10396瀏覽量

147770

原文標題:中國芯片領域研究又有新突破!

文章出處:【微信號:iawbs2016,微信公眾號:寬禁帶半導體技術創(chuàng)新聯(lián)盟】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

小米自研3nm旗艦SoC、4G基帶亮相!雷軍回顧11年造芯路

揭秘芯片測試:如何驗證數(shù)十億個晶體管

漏致勢壘降低效應如何影響晶體管性能

三星公布首批2納米芯片性能數(shù)據(jù)

芯海科技BMS芯片榮膺2025“中國芯”大獎

多值電場型電壓選擇晶體管結構

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產(chǎn)業(yè)的前沿技術

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+工藝創(chuàng)新將繼續(xù)維持著摩爾神話

東京大學開發(fā)氧化銦(InGaOx)新型晶體管,延續(xù)摩爾定律提供新思路

下一代高速芯片晶體管解制造問題解決了!

蘋果A20芯片的深度解讀

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規(guī)則

多值電場型電壓選擇晶體管結構

晶體管電路設計(下)

下一代3D晶體管技術突破,半導體行業(yè)迎新曙光!

3nm晶體管!中國芯片領域研究又有新突破

3nm晶體管!中國芯片領域研究又有新突破

評論