NVMe,可以說是是全閃存陣列的下一個進程,它可讓閃存釋放更高的性能。使用NVMe,全閃存陣列可以提供數十萬甚至數百萬的IOPS,實現微秒級的響應。

但NVMe及其“搭檔”——NVMe over Fabrics(NVMe-oF)都是較新的技術且相對不成熟,NVMe性能改進取決于所選的全閃存陣列架構。傳統的全閃存陣列通過提供NVMe只能帶來將近20%的性能提升,但新興的全閃存陣列提供商的一些NVMe產品預計可提供的性能可以達到當前技術所能提供的10倍或更多倍。

20%的性能提升雖不高,但風險低

在2018年底,支持NVMe的企業級全閃存陣列數量仍然只占整個存儲市場的一小部分。研究公司DCIG在2018年評估了超過100個全閃存陣列,其中不到20%支持采用NVMe接口的SSD。

NVMe支持在全閃存陣列市場中仍處于初期階段,因為使用NVMe存儲陣列的應用程序智能獲得相對較小的性能提升。傳統的全閃存陣列使用兩個或更多控制器連接到后端使用NVMe的SSD。然后,控制器將這些SSD聚合、管理并以存儲卷的形式呈現給網絡連接主機。

使用在后端支持NVMe SSD的全閃存陣列,與使用SATA或SAS SSD的全閃存陣列相比,可以將應用程序性能提高20%。主機仍然通過標準光纖通道(FC)或以太網連接到這些支持NVMe的全閃存陣列。這種方法使企業可以輕松獲得NVMe SSD帶來的性能優勢,同時將環境風險降至最低。

20%的性能提升效果確實不錯,但NVMe SSD全閃存陣列理論上可以提供更大的性能提升——比使用SAS和SATA SSD的全閃存陣列多10倍。

這種巨大的性能差異源于這樣一個事實,即現有的全閃存陣列控制器架構無法釋放NVMe SSD提供的全部性能優勢。陣列控制器的一個最初目標是加速HDD的性能,而在使用NVMe SSD時,這種控制器會成為一種阻礙。為了更好地釋放NVMe SSD的性能,陣列控制器以及存儲網絡協議必須不斷發展。

All In!——NVMe

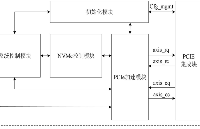

為了獲得NVMe SSD在全閃存陣列中提供的高性能提升,企業必須使用那些可提供端到端NVMe連接的產品。此類全閃存陣列提供前端NVMe-oF,通過FC和以太網網絡連接到主機,并為NVMe SSD提供后端連接。此設計使主機可以使用本機NVMe協議直接與NVMe SSD通信,并借助全閃存陣列控制器發送本機NVMe命令通過以太網和FC存儲網絡。

使用這種方法,有些全閃存陣列提供商報告說,理論上應用程序可以實現低于200微秒的延遲,超過100 GB的吞吐量和數千萬的IOPS。使用機器學習,預測分析和視頻處理的企業可能會需要這種級別的性能。

但要明白,這種方法可能存在風險和一定的局限。必要時,公司還必須限制其環境中NVMe部署的廣度。用于操作系統的NVMe-oF驅動程序,僅適用于最新版本的Linux,例如Red Hat Enterprise Linux 7.4或更高版本,也可能來自全閃存陣列提供商。更值得注意的是,主要的操作系統提供商(如Microsoft和VMware)尚未提供NVMe-oF驅動程序。

可組合基礎架構

通過使用NVMe SSD全閃存陣列或端到端NVMe的方法提高性能,企業可以獲得比較明顯的優勢。不過一兩年后,大多數企業會發現,他們能夠獲得相對更高的靈活性、性能和價值。很快供應商將提供一種新的全閃存陣列架構,將全閃存陣列控制器與后端NVMe SSD分離,以創建可組合的基礎架構。

使用此架構,應用程序可以在全閃存陣列的數據管理功能及其性能之間進行選擇。如果應用程序需要NVMe SSD帶來更高的性能提升,同時也需要陣列控制器中的數據管理功能,例如LUN管理、快照和復制等等,可以通過陣列控制器訪問NVMe SSD并獲得數據管理和性能方面的提升。

但是,如果應用程序需要更高的性能提升,可以繞過陣列控制器并通過NVMe-oF直接訪問陣列中的NVMe SSD。

-

全閃存陣列

+關注

關注

0文章

11瀏覽量

8078 -

nvme

+關注

關注

0文章

299瀏覽量

23842

原文標題:NVMe能否發揮更大價值,取決于全閃存陣列的架構

文章出處:【微信號:D1Net11,微信公眾號:存儲D1net】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

高性能網絡存儲設計:NVMe-oF IP的實現探討

NVMe over Fabrics 國產 IP:高性能網絡存儲解決方案

Neway微波產品:技術領航,創造卓越價值

NVMe高速傳輸之擺脫XDMA設計37:隊列管理功能驗證與分析1

如何看懂GPU架構?一分鐘帶你了解GPU參數指標

NVMe高速傳輸之擺脫XDMA設計30: NVMe 設備模型設計

NVMe高速傳輸之擺脫XDMA設計23:UVM驗證平臺

NVMe高速傳輸之擺脫XDMA設計18:UVM驗證平臺

NVMe高速傳輸之擺脫XDMA設計之十:NVMe初始化狀態機設計

NVMe IP高速傳輸卻不依賴XDMA設計之三:系統架構

NVMe能否發揮更大價值,全閃存陣列的架構是關鍵

NVMe能否發揮更大價值,全閃存陣列的架構是關鍵

評論