LVDS 基礎(chǔ)系列旨在提供低壓差分信號(hào)技術(shù)的基礎(chǔ)知識(shí)。 本視頻系列分為五個(gè)部分。 分別為 LVDS技術(shù)概述,LVDS 的優(yōu)點(diǎn), M-LVDS 和三種常用的通信架構(gòu),LVDS 數(shù)據(jù)速率, 以及 LVDS 接口的典型用例。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報(bào)投訴

-

ti

+關(guān)注

關(guān)注

114文章

8079瀏覽量

219875 -

通信

+關(guān)注

關(guān)注

18文章

6438瀏覽量

140225 -

lvds

+關(guān)注

關(guān)注

2文章

1239瀏覽量

70125

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

熱點(diǎn)推薦

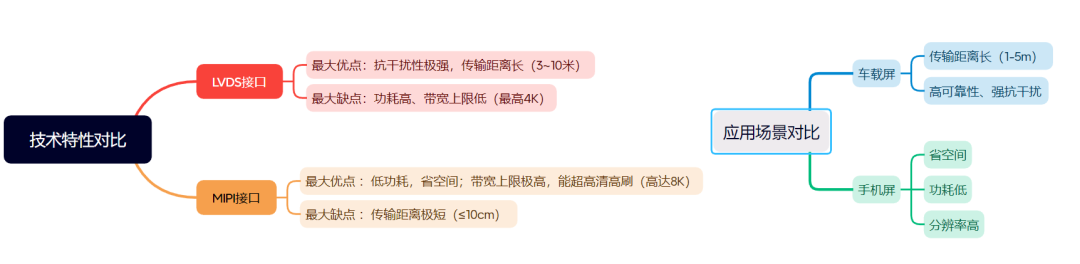

嵌入式分享#51:為什么手機(jī)屏常用MIPI,而車載屏用LVDS?

為什么? 原因無非就是 MIPI 與 LVDS 兩者技術(shù)特性與應(yīng)用場景結(jié)合的必然結(jié)果 。因此,要想知道為什么,直接對(duì)比兩者的技術(shù)特性以及兩種應(yīng)用場景的特點(diǎn)就能得到結(jié)論。 技術(shù)特性對(duì)比 (1)LVDS 接口 最大優(yōu)點(diǎn):抗干擾性極強(qiáng)

SN65LVDS311:可編程27位顯示串行接口發(fā)射器的設(shè)計(jì)與應(yīng)用

SN65LVDS311:可編程27位顯示串行接口發(fā)射器的設(shè)計(jì)與應(yīng)用 在電子設(shè)計(jì)領(lǐng)域,對(duì)于顯示接口的需求日益增長,尤其是在需要高效數(shù)據(jù)傳輸和低功耗的應(yīng)用場景中。TI的SN65LVDS31

深入剖析SN65LVDS95 LVDS 串行器:特性、應(yīng)用與設(shè)計(jì)要點(diǎn)

的 SN65LVDS95 作為一款典型的 LVDS 串行器,在數(shù)據(jù)傳輸系統(tǒng)中發(fā)揮著重要作用。今天,我們就來深入了解一下這款芯片。 文件下載: sn65lvds95.pdf 芯片概述

SN75LVDS32與SN75LVDS9637高速差分線接收器:設(shè)計(jì)與應(yīng)用指南

(TI)的SN75LVDS32和SN75LVDS9637高速差分線接收器,就是LVDS技術(shù)的典型代表。本文將深入探討這兩款接收器的特點(diǎn)、性能參數(shù)以及應(yīng)用場景,為電子工程師在實(shí)際設(shè)計(jì)中提

深入剖析SN75LVDS83A:LVDS顯示發(fā)射機(jī)的卓越之選

、SN75LVDS83A的特性亮點(diǎn) 2.1 接口與兼容性 直接連接LCD面板 :LVDS顯示串行解串器接口可直接連接集成LVDS的LCD顯示

【新品】ZYNALOG徴格半導(dǎo)體推出ZGN4XXX系列LVDS/M-LVDS高速接口芯片

ZYNALOG徴格半導(dǎo)體正式推出ZGN4XXX系列高速接口芯片。該系列涵蓋LVDS線路驅(qū)動(dòng)器、LVDS線路接收器以及M-LVDS收發(fā)器,為您的背板數(shù)據(jù)傳輸、有線數(shù)據(jù)傳輸、時(shí)鐘分配提供高

STMicroelectronics B-LVDS7-WSVGA 7英寸LCD模塊技術(shù)解析與應(yīng)用指南

STMicroelectronics B-LVDS7-WSVGA 7" TFT LCD模塊集成了一塊7” TFT LCD和電容式觸摸面板。超寬視角模塊具有LVDS接口模式。提供LVDS

LVDS接口的顯示屏,顯示偏暗問題的解決方法

問題:點(diǎn)亮屏幕后畫面顯示偏暗

可能原因:

主板輸出的LVDS 模式與屏幕的不一致;

PWM亮度并未調(diào)節(jié)到最亮;

解決方法

檢查主板的LVDS輸出模式是否和屏幕一致;

一般主板端的LVDS模式是可以配置的,配置成與屏幕相同的模式

發(fā)表于 10-09 15:55

Simulink模型測試典型問題分享-接口定義不完整

典型測試問題分享-接口定義不完整

問題描述:

?計(jì)算模塊未定義數(shù)值范圍,存在越界風(fēng)險(xiǎn)。

?信號(hào)未規(guī)定精度和誤差范圍,導(dǎo)致背靠背測試未通過。

液晶顯示屏LVDS接口JEIAD 、VESA、18bit LVDS關(guān)聯(lián)和區(qū)別

分享下液晶顯示發(fā)展史上一個(gè)重要且有趣的階段。LVDS接口不同格式的形成,根本上是成本、帶寬和市場需求之間博弈和演進(jìn)的結(jié)果。

下面我將詳細(xì)解釋它們的歷史成因、關(guān)聯(lián)與區(qū)別。

核心概念:什么是LVDS

發(fā)表于 08-30 09:13

嵌入式接口通識(shí)知識(shí)之LVDS接口

的特點(diǎn)是每對(duì)信號(hào)線(正負(fù)極性)之間的電壓差是信號(hào)的有效部分,而不是單獨(dú)的電平。這種差分傳輸方式使得LVDS接口在長距離傳輸時(shí)能夠保持較高的抗干擾能力和數(shù)據(jù)傳輸速率。它的主要工作原理就是將發(fā)送端將輸入信號(hào)

發(fā)表于 08-29 15:52

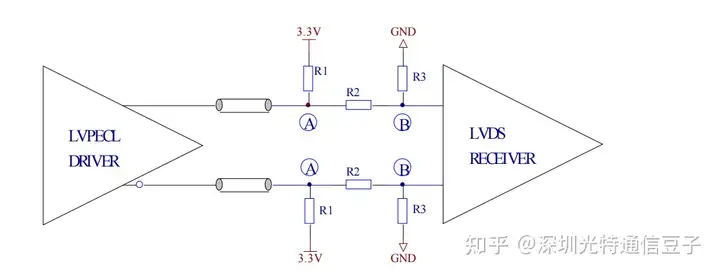

LVPECL 與 LVDS 及 PECL 與 LVDS 的互連技術(shù)解析

在高速光通信系統(tǒng)中,LVPECL(低壓正射極耦合邏輯)、PECL(正射極耦合邏輯)與 LVDS(低壓差分信號(hào))是常用的高速接口電平標(biāo)準(zhǔn)。LVPECL/PECL 以高速度、低噪聲特性廣泛應(yīng)用于光模塊

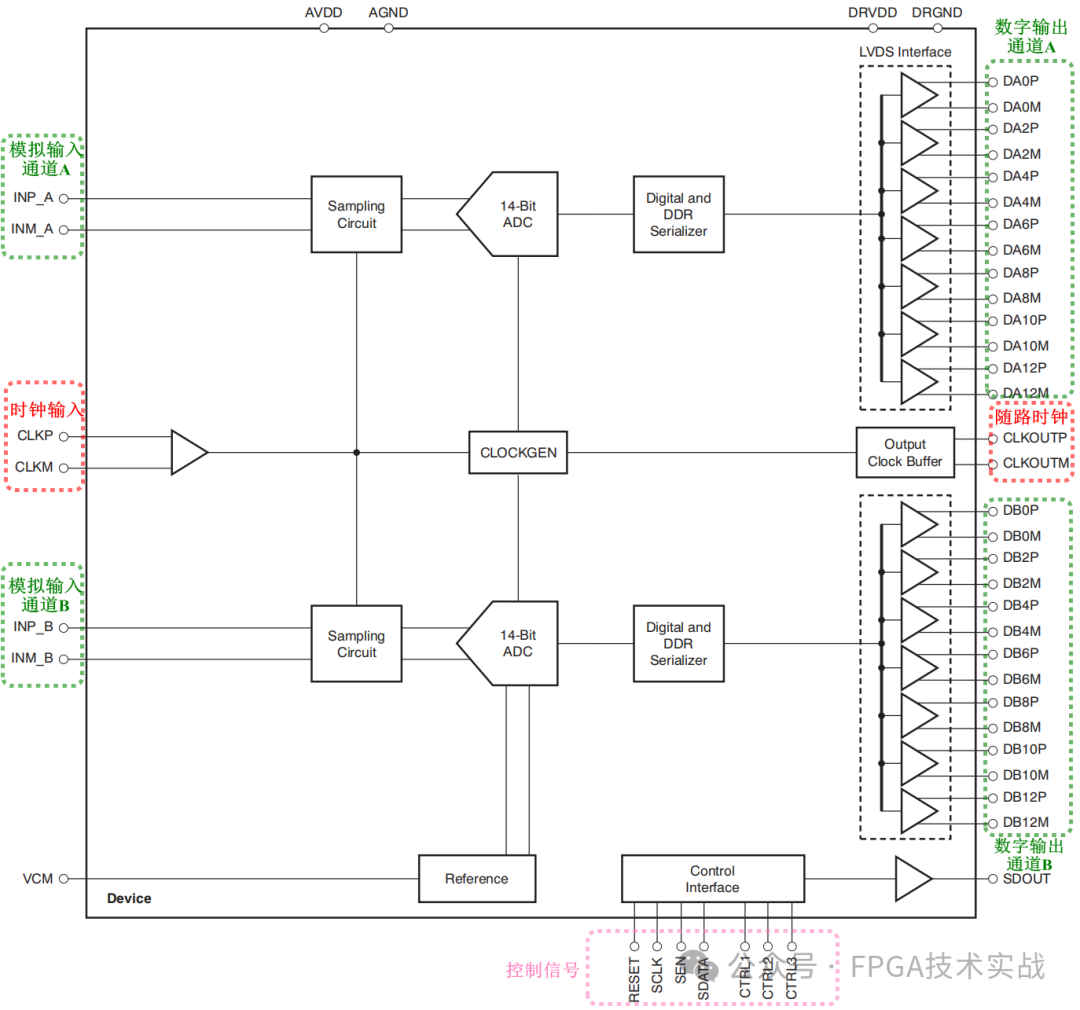

ADC和FPGA之間LVDS接口設(shè)計(jì)需要考慮的因素

本文描述了ADC和FPGA之間LVDS接口設(shè)計(jì)需要考慮的因素,包括LVDS數(shù)據(jù)標(biāo)準(zhǔn)、LVDS接口數(shù)據(jù)時(shí)序違例解決方法以及硬件設(shè)計(jì)要點(diǎn)。

Altera FPGA與高速ADS4249和DAC3482的LVDS接口設(shè)計(jì)

引言: 本文以TI的ADS4249(ADC)和DAC3482(DAC)之間的接口為例,介紹Altera FPGA與ADC/DAC之間的DDR LVDS接口設(shè)計(jì)以及時(shí)序約束詳細(xì)設(shè)計(jì)。本文

請問imx8mp的LVDS0和LVDS1接口是否可以同時(shí)在兩個(gè)屏幕上工作?

請問 imx8mp 的 LVDS0 和 LVDS1 接口是否可以同時(shí)在兩個(gè)屏幕上工作?

你有什么例子嗎?

發(fā)表于 04-14 06:11

LVDS接口的典型用例分析

LVDS接口的典型用例分析

評(píng)論