這里的Block是指Block RAM和DSP48。在有些設計中,這兩者有其一或者兩者均出現利用率比較高的情形,而且在某一版本中可以達到時序收斂。如果后續版本并不涉及到對Block的修改,特別是不會出現對Block RAM位寬的修改,為了達到時序收斂,一個可行的方案就是繼承收斂版本的Block的布局。本質上,就是復用這些Block的位置信息。在Vivado下完成這樣的操作非常簡單。

Step 1

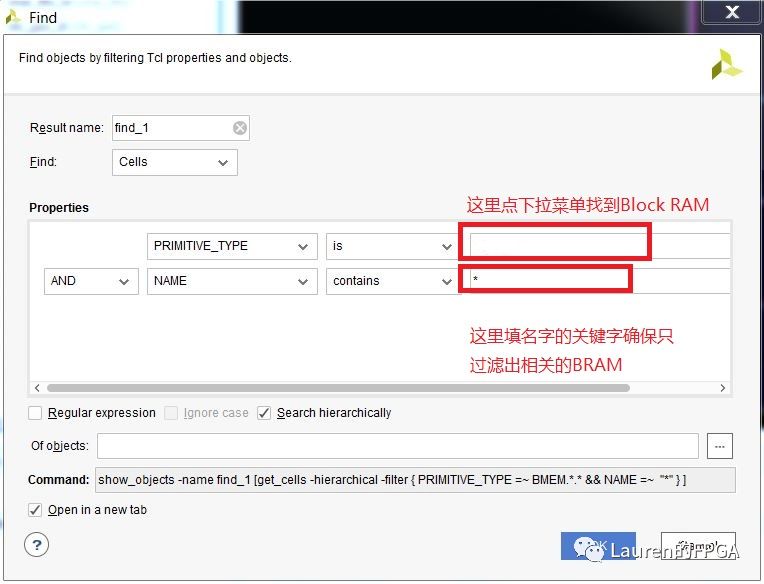

打開布線后的設計,并找到設計中的Block,這里以Block RAM為例,查找方法如下圖所示,依次選擇Edit -> Find,即可出現此界面。

Step 2

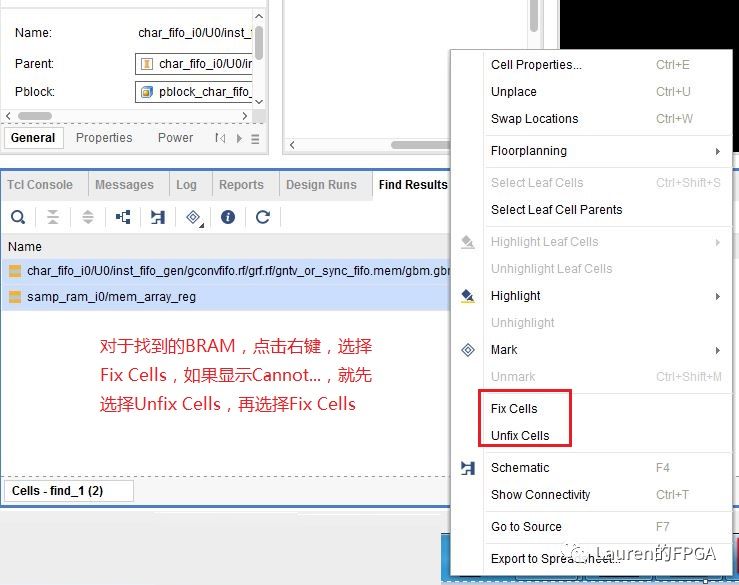

固定BRAM的位置。選中第一步中找到的BRAM,點擊右鍵,選擇Fix Cells即可,如下圖所示。

Step 3

保存Block的位置信息。一旦固定了BRAM的位置,即可點擊Vivado菜單欄內的保存按鈕,這樣就把BRAM的位置信息保存到了target約束文件中。一個小技巧是在保存之前創建一個新的約束文件,并把該文件設置為target約束文件,然后保存,這些信息就在該文件中,如下圖所示。

實際上,上述操作均可通過Tcl腳本完成,如下圖所示。

結論

對于Block RAM或DSP48利用率較高的情形,在時序收斂時,可繼承其位置信息。這樣,如果后續設計不牽涉到這些Block的改動,那么即可復用其位置信息,從而加速時序收斂的進程。

-

Block

+關注

關注

0文章

26瀏覽量

15154 -

BRAM

+關注

關注

0文章

43瀏覽量

11656

原文標題:如何復用原有設計中Block的位置

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何復用原有設計中Block的位置

如何復用原有設計中Block的位置

評論