時(shí)鐘和時(shí)鐘振蕩器(也稱為時(shí)鐘發(fā)生器)幾乎是每個(gè)電路的一部分,大多數(shù)系統(tǒng)的設(shè)計(jì)都不止一個(gè)。事實(shí)上,設(shè)計(jì)中有四個(gè),六個(gè)或更多,支持內(nèi)部電路以及外部I/O和接口并不罕見。它們建立最終載波設(shè)置或重新建立并與接收信號(hào)載波同步。此外,許多系統(tǒng)都需要能夠更改或轉(zhuǎn)換時(shí)鐘,以滿足超過單一終端應(yīng)用情況的調(diào)整要求。

時(shí)鐘在為各種應(yīng)用提供服務(wù)時(shí)提供了廣泛的功能和特性,但是還有相當(dāng)多的命名和功能混淆與重疊的術(shù)語,如時(shí)鐘,振蕩器,發(fā)生器和合成器等。

固定頻率時(shí)鐘用于處理器,存儲(chǔ)器和其他外圍設(shè)備的調(diào)步。同一系列中的一系列類似產(chǎn)品可能需要不同的時(shí)鐘頻率,以支持各種速度選項(xiàng)或功能。這些固定頻率時(shí)鐘也可以用作有線和無線鏈路中的基本定時(shí)參考。一些時(shí)鐘元件包括晶體或其他定時(shí)源,用于產(chǎn)生輸出;其他需要用戶提供外部晶體。

一些固定頻率設(shè)備是可編程的,因此可以在多個(gè)BOM(物料清單)上使用相同的設(shè)備來簡化庫存,但即使是“可編程”設(shè)備也可能存在誤解。它們可以是供應(yīng)商的一次性可編程,OEM生產(chǎn)線上的一次性可編程,電路板上可編程的引腳帶,或軟件可編程甚至可以“動(dòng)態(tài)”重新編程。此外,還有可編程時(shí)鐘,可以重新編程有限次數(shù),頻率甚至可以改變幾次,以適應(yīng)不同的生產(chǎn)和應(yīng)用需求。為了增加潛在的復(fù)雜性,一些時(shí)鐘振蕩器提供多個(gè)同時(shí)獨(dú)立的輸出,因此單個(gè)晶體和器件可以提供大多數(shù)系統(tǒng)所需的多個(gè)時(shí)鐘。

此外,還有合成器使用單晶或主時(shí)鐘在指定范圍內(nèi)產(chǎn)生任意頻率輸出。與基本時(shí)鐘振蕩器一樣,一些合成器一旦固定就固定,其他合成器可動(dòng)態(tài)設(shè)置,以根據(jù)需要提供指定頻譜中的任何頻率(通常是載波)。

在無線系統(tǒng)中,有兩組基本時(shí)鐘:用于設(shè)置通道基本時(shí)序的固定頻率,例如點(diǎn)對(duì)點(diǎn)專用鏈路,以及可根據(jù)需要移動(dòng)頻率的時(shí)鐘支持不同的頻道,例如Wi-Fi鏈路上的跳頻。

選擇注意事項(xiàng)

考慮到所有時(shí)鐘選項(xiàng),確定哪種基本時(shí)鐘方法是合適的可能是一個(gè)挑戰(zhàn)。但是,通過專注于主要規(guī)范可以簡化該過程,因?yàn)椴⒎撬袝r(shí)鐘配置選項(xiàng)都具有可比較的規(guī)范。只有滿足這些頂級(jí)要求的設(shè)備才能在各種配置中考慮。與往常一樣,性能的權(quán)衡需要根據(jù)性能屬性的權(quán)重進(jìn)行評(píng)估。

最關(guān)鍵的形式是時(shí)鐘的最大標(biāo)稱頻率能力,對(duì)于大多數(shù)無線應(yīng)用來說,它將跨越幾百個(gè)MHz到GHz范圍。對(duì)于可編程器件,最大值和最小值都很關(guān)鍵;時(shí)鐘IC通常具有10:1或5:1最大/最小跨度。

另一個(gè)重要規(guī)格是給定設(shè)置下的初始頻率誤差(容差),以百分比,Hz或百萬分率表示。如果時(shí)鐘不是固定頻率設(shè)備,則該數(shù)量可以根據(jù)標(biāo)稱頻率而變化。

所有振蕩器都會(huì)漂移。如果器件包含內(nèi)部晶體,或者它使用模擬電路調(diào)節(jié)和縮放外部晶體,它將隨溫度發(fā)生一些漂移;如果它是一個(gè)全數(shù)字設(shè)備,漂移將會(huì)更少,盡管仍然會(huì)有一些閾值,邏輯門的時(shí)序會(huì)略有變化。高性能振蕩器的溫度系數(shù)通常以ppm/?C表示,其值范圍從大約十到幾百。當(dāng)然,最大可接受值取決于應(yīng)用。

對(duì)于頻率在使用期間動(dòng)態(tài)切換的振蕩器,而不是僅在初始上電時(shí)通過用戶啟動(dòng)的調(diào)諧或模式切換進(jìn)行更改,關(guān)鍵參數(shù)是確定新頻率的時(shí)間。根據(jù)振蕩器的架構(gòu),對(duì)于合成器或基于PLL的設(shè)計(jì),或者相對(duì)較長的時(shí)間,這幾乎是瞬時(shí)的。即使核心電路沒有不連續(xù)性(如某些架構(gòu)那樣),如果相關(guān)的輸出緩沖放大器或驅(qū)動(dòng)器必須在很大范圍內(nèi)擺動(dòng),可能會(huì)出現(xiàn)建立時(shí)間問題。通常,小的頻率變化并不具有挑戰(zhàn)性,但是廣泛的變化可能會(huì)有更長的穩(wěn)定時(shí)間;實(shí)際上,振蕩器必須在整個(gè)范圍內(nèi)快速轉(zhuǎn)換的應(yīng)用很少。

在許多情況下,漂移也是一個(gè)考慮因素。具有內(nèi)部晶體的時(shí)鐘由于晶體老化而表現(xiàn)出短期和長期漂移,盡管這些術(shù)語可能與每個(gè)供應(yīng)商具有不同的定義。有些人將“短期”定義為一年,將“長期”定義為五年,十年甚至二十年。最后,將功耗和封裝尺寸因素問題納入決策,但與基本性能規(guī)范相比,這些通常是次要的。一般來說,低功耗器件的規(guī)格要低于消耗更多功率的器件,但這是一個(gè)工藝,設(shè)計(jì)和測試的進(jìn)步意味著權(quán)衡利弊的領(lǐng)域。

抖動(dòng):最具挑戰(zhàn)性的問題有很多原因

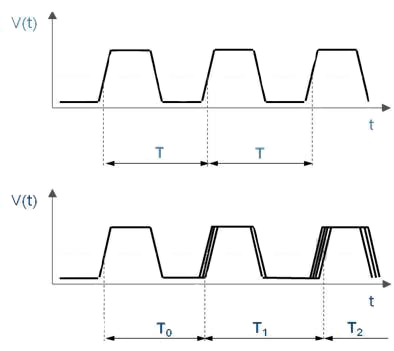

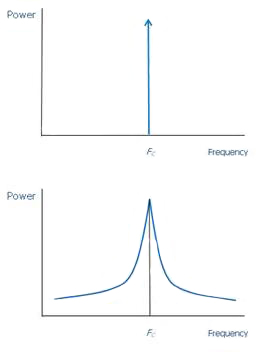

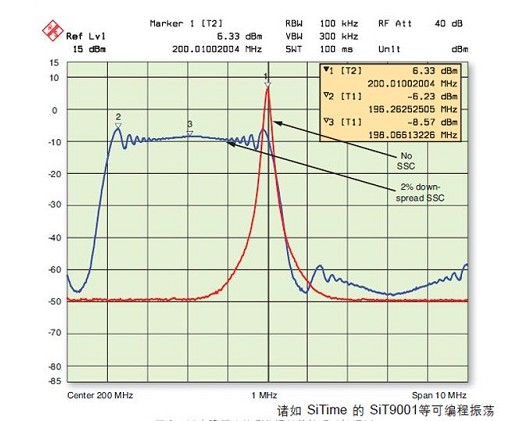

在決定振蕩器選項(xiàng)時(shí)工程師必須評(píng)估的最關(guān)鍵參數(shù)中,抖動(dòng)是最難以表征和匹配的應(yīng)用。在時(shí)域中,抖動(dòng)表現(xiàn)為“完美”輸出的微小變化(圖1);在頻域中,它表現(xiàn)為相位/頻率變化(噪聲)和單頻信號(hào)頻譜的擴(kuò)展(圖2)。兩種觀點(diǎn)都是同樣有效的方式來觀察相同的物理現(xiàn)象,哪種觀點(diǎn)取決于具體情況,適用的標(biāo)準(zhǔn)和系統(tǒng)性能要求。

圖1:在時(shí)域中,理論上“完美”的時(shí)鐘信號(hào)(頂部)顯示了微小的來回變化(底部)被定義為抖動(dòng)。 (由IDT提供)

圖2:在同等合法的頻域替代視圖中,完美的單頻尖峰(頂部)變?yōu)轭l率分量和相關(guān)能量的傳播(下圖)。 [由IDT提供]

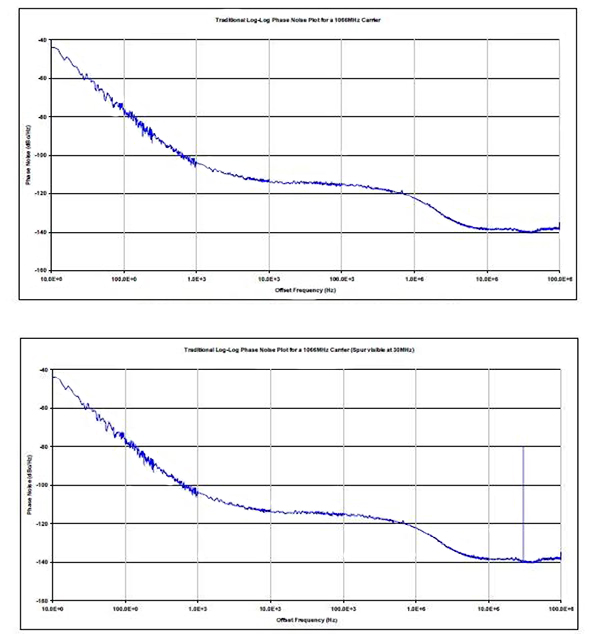

抖動(dòng)是一個(gè)復(fù)雜的主題,并且由于幾個(gè)原因通常難以量化。它通常相對(duì)較小,但仍然是系統(tǒng)性能的重要因素;它有許多貢獻(xiàn)源,包括內(nèi)部電路噪聲,外部源噪聲,元件熱噪聲,元件缺陷和熱致機(jī)械變化。作為概率特征,沒有單一的正確或簡單的方法來定義它;在使用的許多定義中,有許多定義是峰值,均方根,平均值,短期變化和長期平均值等等。抖動(dòng)也可能在輸出上顯示為非諧波相關(guān)的頻率雜散,與基頻相距一定距離(圖3a和3b)。

圖3a和3b:與抖動(dòng)相關(guān)的雜散是不需要的頻率分量,與基波無諧波相關(guān);上部跡線是對(duì)數(shù) - 對(duì)數(shù)相位噪聲圖,顯示1066 MHz時(shí)鐘頻域的無雜散抖動(dòng);較低的走線是相同的時(shí)鐘,但與基頻相比具有30 dB的30 MHz偏移。

抖動(dòng)的影響范圍可以是A/D采樣誤差和D/A轉(zhuǎn)換時(shí)間,“噪聲“在信號(hào)上,增加了BER(誤碼率),增加了符號(hào)間干擾,以及許多其他表現(xiàn)形式。通常,時(shí)鐘抖動(dòng)的可見影響在系統(tǒng)的其他地方,例如對(duì)不可避免的信道噪聲的容忍度降低,這會(huì)在采樣窗口收縮并且ISI眼圖關(guān)閉時(shí)發(fā)生。抖動(dòng)與整體系統(tǒng)性能之間的聯(lián)系有時(shí)難以判斷,并且通常由于額外的抖動(dòng)而使電路的非時(shí)鐘部分增加到時(shí)鐘信號(hào)本身。振蕩器抖動(dòng)還可以建立相位本底噪聲,以dBc/Hz為單位,是一個(gè)品質(zhì)因數(shù)(FOM),對(duì)于高性能接收器通道或雷達(dá)系統(tǒng)等應(yīng)用非常重要。

匹配時(shí)鐘發(fā)生器時(shí)針對(duì)應(yīng)用的抖動(dòng)規(guī)范,最好查看業(yè)界為該應(yīng)用設(shè)置的標(biāo)準(zhǔn)(如果有)(例如IEEE 802.11x),閱讀與應(yīng)用相關(guān)的應(yīng)用筆記,并仔細(xì)研究數(shù)據(jù)表及其應(yīng)用測試條件和腳注。

示例顯示了不同的產(chǎn)品

兩個(gè)時(shí)鐘振蕩器/發(fā)生器IC系列展示了這個(gè)基本功能如何演變成非常不同的組件。 Silicon Labs Si5xx產(chǎn)品組合非常適合從網(wǎng)絡(luò)設(shè)備,基站,存儲(chǔ)區(qū)域網(wǎng)絡(luò)和廣播視頻系統(tǒng)到數(shù)據(jù)通信和電信的單板計(jì)算機(jī)等應(yīng)用。這些單,雙和四I 2 C可編程頻率器件的工作頻率范圍為100 KHz至1.4 GHz,具有低抖動(dòng)操作特性。例如,Si535提供0.19 ps RMS類型的相位抖動(dòng),從而提高了設(shè)計(jì)余量和系統(tǒng)級(jí)性能。與傳統(tǒng)的XO不同,Si535使用一個(gè)固定晶體來提供寬范圍的輸出頻率,而每個(gè)輸出頻率都需要不同的晶體。這種基于IC的方法允許晶體諧振器提供出色的頻率穩(wěn)定性和可靠性。此外,DSPLL時(shí)鐘合成可提供卓越的電源噪聲抑制,簡化了在通信系統(tǒng)中常見的嘈雜環(huán)境中生成低抖動(dòng)時(shí)鐘的任務(wù)。

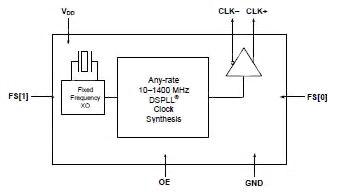

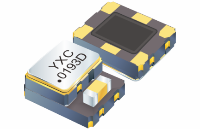

同樣,供應(yīng)商的Si534是一款四頻晶體振蕩器,可以在10至945 MHz的任何頻率和1400 MHz的選定頻率下提供單一輸出(圖4)。它針對(duì)通用無線和有線鏈路,由供應(yīng)商根據(jù)各種用戶規(guī)范進(jìn)行配置,包括頻率,電源電壓(3.3,2.5和1.8 V),輸出格式(CMOS,LVPECL,LVDS和CML),以及溫度穩(wěn)定性;請(qǐng)注意,包括抖動(dòng)在內(nèi)的規(guī)格會(huì)因這些設(shè)置而異。在這種情況下,用戶可以通過小型(5×7 mm)8引線器件封裝上的兩個(gè)控制引腳選擇四個(gè)可用頻率中的哪一個(gè)(工廠設(shè)置為用戶訂單)應(yīng)出現(xiàn)在該器件的輸出端,包括內(nèi)部晶體。

圖4:Silicon Labs XO包含一體化晶體;它由供應(yīng)商按照客戶選擇的四個(gè)輸出頻率進(jìn)行編程,然后可以通過兩條控制線隨時(shí)調(diào)用四個(gè)中的任何一個(gè)。

典型的初始精度在25°C時(shí)為±1.5 ppm,而第一年漂移為±3 ppm,超過20年的漂移據(jù)說最大為±10 ppm。該供應(yīng)商提供了許多抖動(dòng)規(guī)范,其中包括500 MHz以上輸出頻率的相位抖動(dòng)(rms),0.25 psec(典型值)和0.40 psec(最大值),以及622.08 MHz的典型輸出相位噪聲-146 dBc/Hz(用LVPECL輸出)。在四個(gè)可能的時(shí)鐘輸出之間切換時(shí)的建立時(shí)間最長為20毫秒。

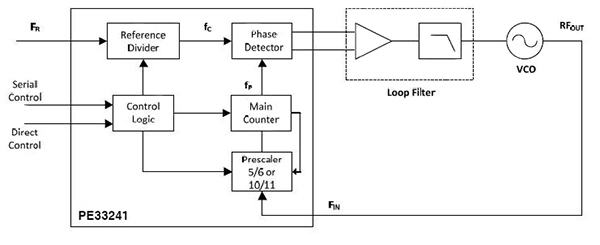

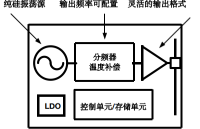

同樣值得注意的是Peregrine Semiconductor PE33241針對(duì)無線本地環(huán)路(WLL);射頻產(chǎn)生; L,S和C波段合成器;和通信系統(tǒng),移動(dòng)終端,遙測,雷達(dá)和便攜式無線電中的時(shí)鐘恢復(fù)(圖5)。這種用于低相位噪聲應(yīng)用的整數(shù)N鎖相環(huán)(PLL)頻率合成器可以使用10/11預(yù)分頻模數(shù)達(dá)到5 GHz,使用5/6預(yù)分頻模數(shù)可達(dá)到4 GHz(后一模數(shù)選擇可提供更好的規(guī)格) )。建立輸出頻率的計(jì)數(shù)器值可由用戶通過其串行接口或直接硬連線配置進(jìn)行編程。這款48引腳7×7 mm QFN器件的相位噪聲基底FOM為-230 dBc/Hz。

圖5:Peregrine的PE33241半導(dǎo)體根據(jù)所選的模數(shù)對(duì)提供4或5 GHz的用戶可選輸出;極低相位噪聲基底FOM為-230 dBc/Hz,非常適合雷達(dá),遙測和高級(jí)移動(dòng)無線電系統(tǒng)。

該IC的頻率范圍和高性能意味著在給定的應(yīng)用程序中評(píng)估和正確編程它可能很困難。因此,供應(yīng)商提供帶有USB接口的評(píng)估板(指定為EK33241-13),以便在使用外部穩(wěn)定的低噪聲參考源時(shí)展示出最佳的相位噪聲性能(圖6)。在這些GHz頻率下,無處不在的FR-4 PC板材料不適合,因此評(píng)估板由四層堆疊組成,兩層外層為Rogers 4350B(εr= 3.48),兩層內(nèi)層為FR406(ε) r = 4.80)材料。 12密耳(0.30 mm)厚的內(nèi)層為RF傳輸線提供接地層,總板厚為62密耳(1.57 mm)。

圖6:在GHz頻譜中提供低噪聲,高性能規(guī)格的器件很難評(píng)估并集成到整個(gè)系統(tǒng)設(shè)計(jì)中,因此Peregrine提供了一個(gè)USB兼容的評(píng)估板來完成任務(wù)。

-

處理器

+關(guān)注

關(guān)注

68文章

20255瀏覽量

252412 -

半導(dǎo)體

+關(guān)注

關(guān)注

339文章

30746瀏覽量

264325 -

振蕩器

+關(guān)注

關(guān)注

28文章

4172瀏覽量

142912

發(fā)布評(píng)論請(qǐng)先 登錄

可編程時(shí)鐘振蕩器用作FPGA系統(tǒng)的時(shí)序參考有何優(yōu)勢?

利用可編程振蕩器增強(qiáng)FPGA應(yīng)用

愛普生可編程石英振蕩器都有哪些系列?具有什么使用特點(diǎn)?

可編程時(shí)鐘振蕩器的電路原理圖免費(fèi)下載

YXC高精度的石英可編程壓控溫補(bǔ)振蕩器:YSV531PT系列

可編程時(shí)鐘振蕩器系統(tǒng)的應(yīng)用設(shè)計(jì)

可編程時(shí)鐘振蕩器系統(tǒng)的應(yīng)用設(shè)計(jì)

評(píng)論