無線工程師經常希望使用無線信號實現從概念到原型。諸如USRP(通用軟件無線電外設)設備的軟件無線電(SDR)提供了滿足該需求的靈活解決方案。由于當今的應用需要更高的帶寬和更短的延遲,因此需要在SDR的FPGA上實現更多的信號處理。但編程FPGA的無線工程師經常面臨下列挑戰:

1. FPGA與輸入/輸出(如RF信號或主機CPU)之間的接口困難2. 不熟悉用于算法實現的編程樣式,及3. 編譯時間長

在本系列適用于無線工程師的FPGA原型設計中,了解LabVIEW Communications System Design Suite (LabVIEW Communications)和NI SDR硬件如何幫助您克服關鍵性挑戰,并快速創建無需FPGA知識的實時、無線測試平臺。

第1部分. 立即連接FPGA算法至I/O

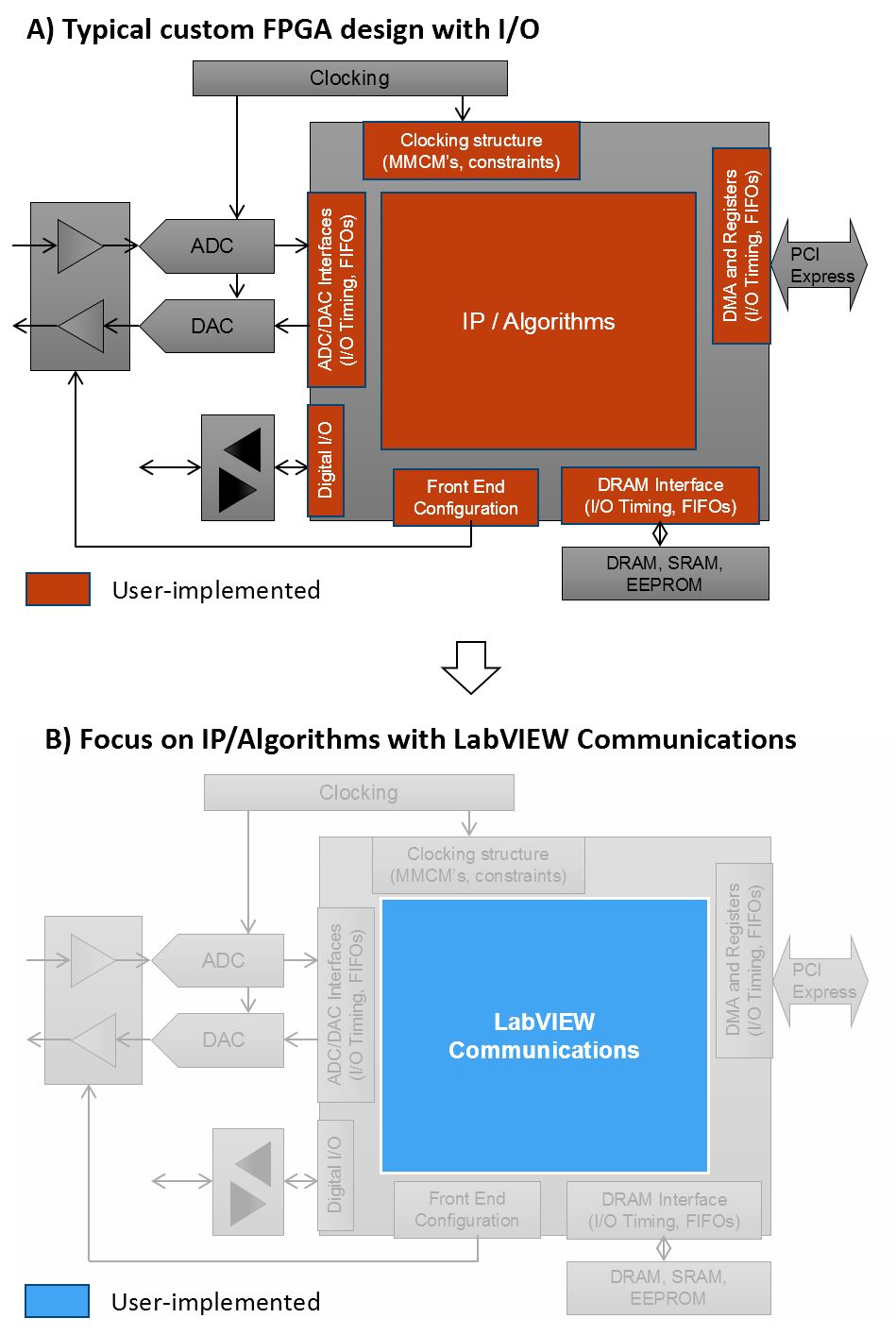

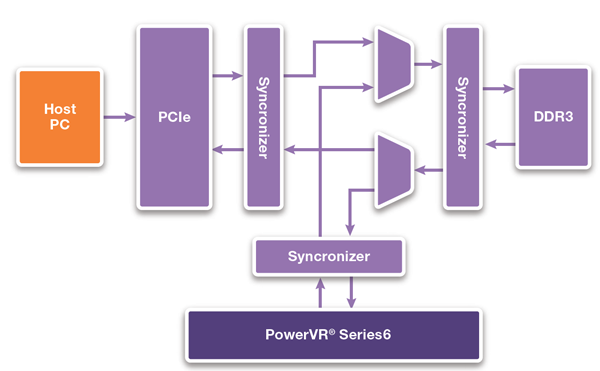

FPGA設計通常需要多個VHDL代碼組件以用于模數轉換器(ADC)、數模轉換器(DAC)、PCI Express總線、存儲器、時鐘等接口(圖1A)。其中的每一部分通常來自于:從零開發、重用現有的設計或從Xilinx或其他IP供應商處獲得的IP。這意味著必須完成重要的集成工作以連接上述各部分,該集成工作通常比算法實現本身工作量更大。

盡管這些硬件接口實現起來很難,但定制它們的意義不大。例如,通過ADC接口關閉靜態定時和計算同步可能較難實現,但它在不同項目中的模數轉換功能基本相同。為了消除此瓶頸,LabVIEW Communications提供了SDR印刷電路板上所有硬件的接口。例如,ADC數據作為已被正確采樣且已轉換為正確的數據類型的采樣提供給FPGA程序框圖,用戶僅需在程序框圖上放置讀取I/O節點即可訪問這些數據。同樣,如要將數據以數據流方式從FPGA傳輸至CPU,僅需使用寫入FIFO節點而無需考慮實際的數據流實現方式。

在無線工程師適用的FPGA原型的第一部分,我們將介紹如何利用LabVIEW Communications快速在FPGA上傳輸數據,即讓用戶專注于算法的實現。

圖1.(A)在帶有I/O的典型自定義FPGA設計中,設計團隊通常在集成I/O接口上花費的時間要高于實現算法或IP。(B)在LabVIEW Communications中已經實現了這些接口,因此設計團隊可以專注于實現信號處理而不是系統集成。

第1步. 放置I/O節點

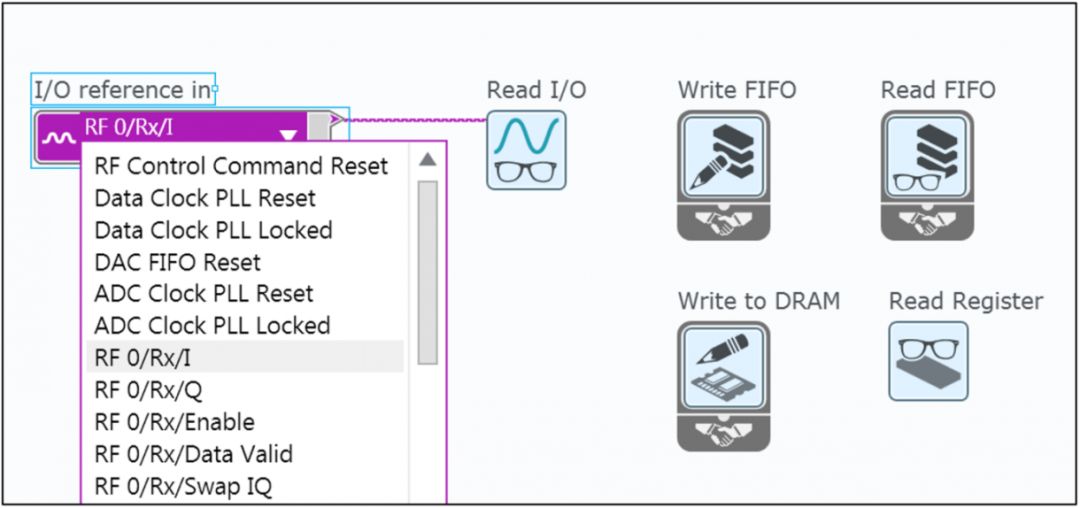

如要將FPGA算法與連接到RF前端的ADC和DAC、主機CPU或內存等資源建立連接,僅需為該資源放置一個讀取或寫入節點。關于節點的范例見圖2。

圖2.使用這些塊與實際I/O及與主機CPU、USRP RIO設備上的DRAM或寄存器交互數據的FIFO通信。

第2步. 配置I/O節點

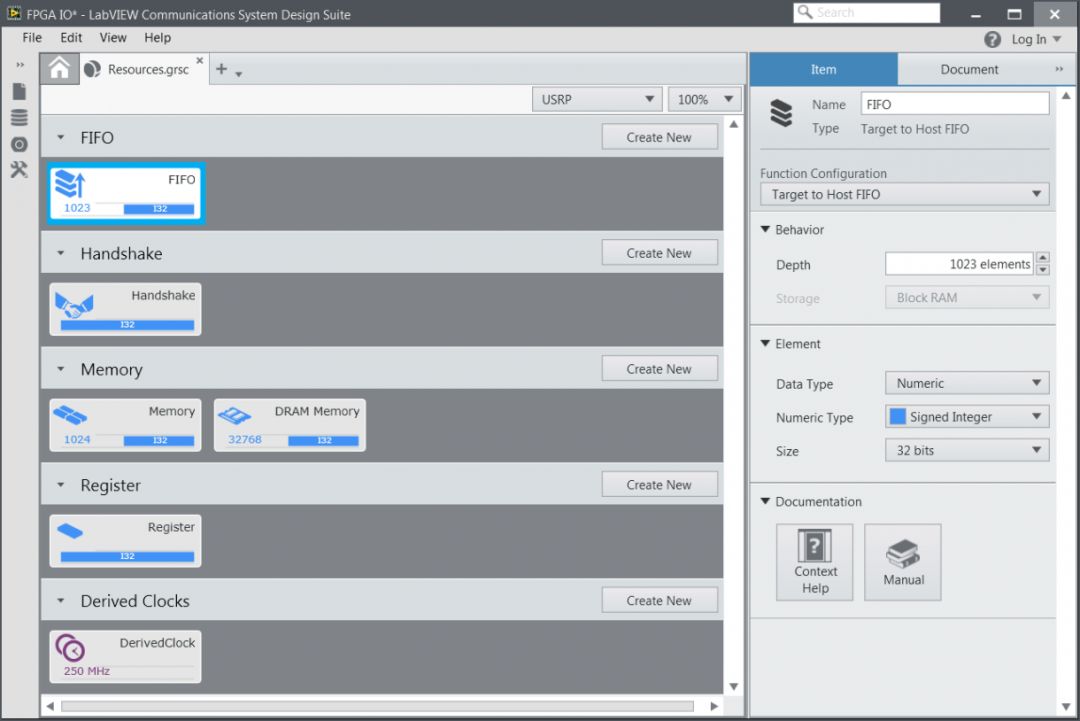

可使用資源文件配置FPGA I/O資源,如圖3所示。配置資源別名、數據類型、方向(FPGA到主機、主機到FPGA、FPGA到FPGA、本地)或緩沖深度等屬性。

圖3.使用資源文件來創建和配置FIFO、內存、時鐘和其他資源。

第3步. 連接算法至I/O節點

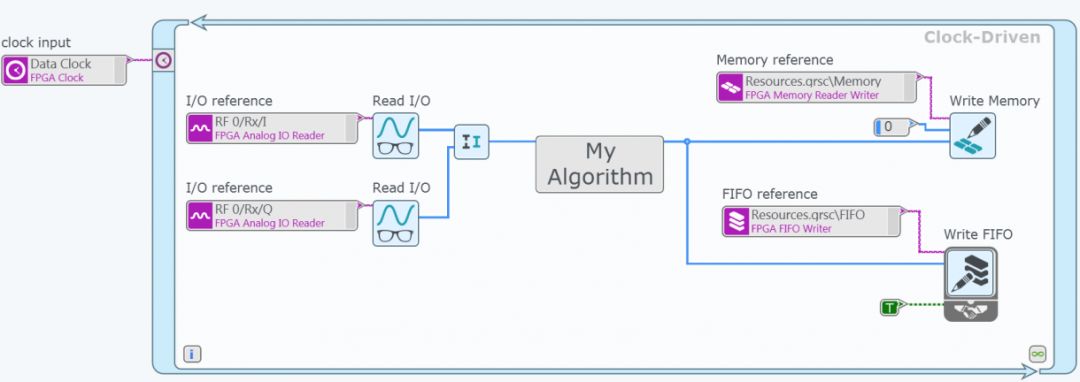

創建并配置了所需的資源后,就可以將它們連接至在FPGA上實現的算法。例如,圖4框圖是在LabVIEW Communications中的FPGA上實現的(見圖5)。在該設計中,來自USRP RIO設備接收端口的數據以數據流方式傳遞至FPGA上的“My Algorithm”,這與同步、解調或濾波塊類似。然后,該輸出以數據流方式傳輸至內存和FPGA至CPU FIFO。

圖4.該范例設計的框圖顯示了如何從RF前端接收數據,然后經由名為“My Algorithm”的用戶創建塊處理,最后以數據流方式傳輸至內存和主機CPU。“My Algorithm”可以是任意算法(如解調、濾波或快速傅里葉變換)。

圖5.在LabVIEW Communications中FPGA代碼的理論程序框圖的實現中,從RF前端讀取原始I和Q數據,然后經由“My Algorithm”處理,最后以數據流方式傳輸至內存和主機CPU。

第4步. 下一步

如要在FPGA上編寫類似“My Algorithm”這樣的自定義實時塊,使用LabVIEW Communications免除了具備VHDL經驗的要求。如要了解如何創建類似20 MHz正交頻分復用(OFDM)調制器的算法,請繼續閱讀本技巧和竅門系列的下一部分:在不具備HDL專門知識的情況下從概念到FPGA代碼。

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636300 -

cpu

+關注

關注

68文章

11279瀏覽量

224978 -

接口

+關注

關注

33文章

9520瀏覽量

157027

原文標題:無線工程師適用的FPGA系列:立即連接FPGA算法至I/O

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

工程師分享:基于FPGA的GPU原型優化設計

FPGA算法工程師、邏輯工程師、原型驗證工程師有什么區別?

設計教訓如何成就稱職的FPGA資深工程師?

電子工程師創新設計必備寶典之FPGA開發全攻略

招聘:軟件工程師(數字信號處理方向-FPGA)、硬件工程師

【成都】【招聘】誠聘FPGA工程師、 windows設備驅動開發工程師、嵌入式軟件開發工程師、硬件工程師等

為什么說nano FPGA技術適用于消費性市場?

FPGA工程師需要具備哪些技能?

fpga就業怎么樣_fpga工程師是青春飯嗎_fpga工程師發展前景

無線工程師適用的FPGA原型設計克服編程關鍵性挑戰

無線工程師適用的FPGA原型設計克服編程關鍵性挑戰

評論