Anaflash(加利福尼亞州圣何塞)是一家初創(chuàng)公司,它開發(fā)了一種測試芯片,用于演示在邏輯兼容的嵌入式閃存中進行的模擬神經(jīng)網(wǎng)絡(luò)計算。

該公司由Suvolta的前模擬設(shè)計副總裁Sang-Soo Lee于2017年成立。明尼蘇達大學(xué)的研究人員在舊金山舉行的國際電子器件會議上發(fā)表了一篇關(guān)于其方法的論文。該論文的標題為:“A 68 parallel row access neuromorphic core with 22K multi-level aynapses based on logic-compatible embedded flash memory technology”

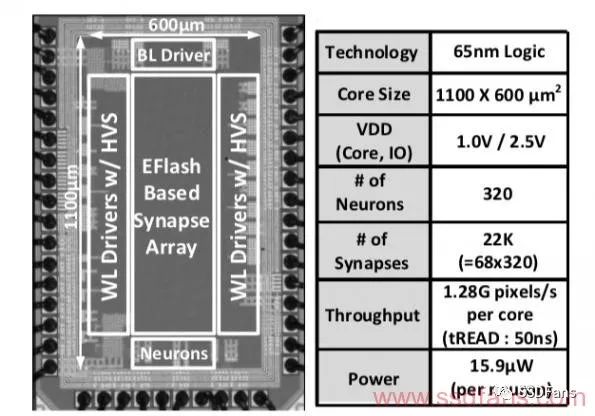

該論文討論了一種利用邏輯兼容的嵌入式閃存技術(shù)的尖峰神經(jīng)形態(tài)核心,用于存儲多級突觸權(quán)重,用65nm的標準CMOS工藝流片。這種存儲器支持5級的讀操作,相當(dāng)于2.3位(5=2^2.3)。

該芯片具有多級非易失性權(quán)重存儲,單周期因子聚合和尖峰生成,可包含320個神經(jīng)元。使用程序驗證序列調(diào)整權(quán)重,允許同時對68個單獨的單元因子求和。作者說,據(jù)他們所知,這是迄今為止報道的最高之一。

68個并排設(shè)計支持22,000個多級突觸,這些基于電子閃存的突觸是非易失性的,因此待機功率為0且支持即時的開/關(guān)操作。

該測試芯片用于手寫數(shù)字識別時,其準確度達到了91.8%。該論文指出,最大吞吐量為1.28G像素/秒,單個神經(jīng)元電路的平均功耗為15.9微瓦。

該公司宣布已在美國和其他國家提交專利申請。

-

嵌入式

+關(guān)注

關(guān)注

5198文章

20449瀏覽量

334058 -

機器學(xué)習(xí)

+關(guān)注

關(guān)注

66文章

8553瀏覽量

136949

原文標題:支持機器學(xué)習(xí)的嵌入式閃存研發(fā)成功

文章出處:【微信號:SSDFans,微信公眾號:SSDFans】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

鎧俠UFS 5.0嵌入式閃存出樣

什么是嵌入式應(yīng)用開發(fā)?

系統(tǒng)嵌入式的學(xué)習(xí)路線

ARM嵌入式這樣學(xué)

嵌入式和FPGA的區(qū)別

嵌入式與單片機定義及區(qū)別

嵌入式系統(tǒng)的定義和應(yīng)用領(lǐng)域

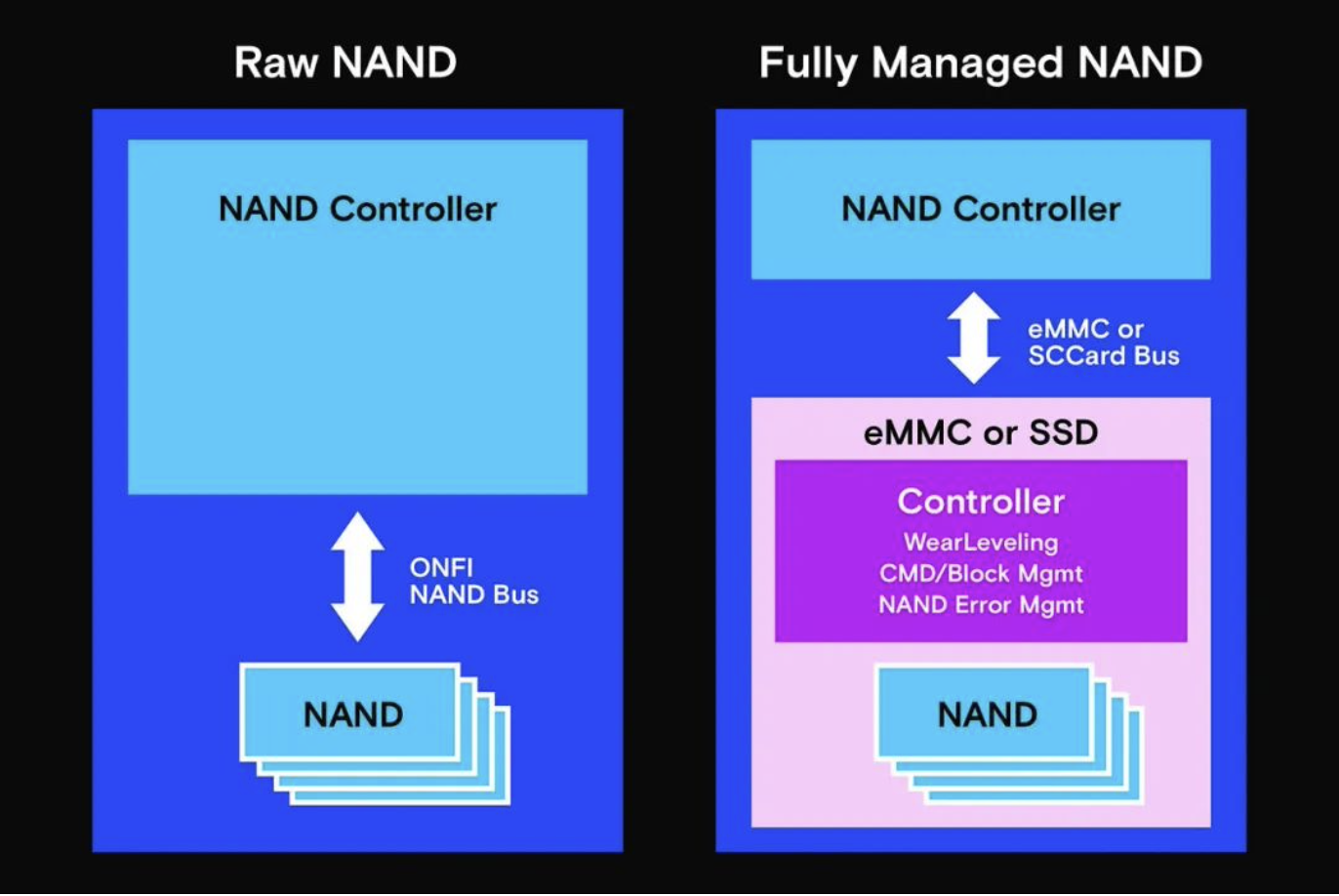

SD NAND vs SPI NAND:嵌入式存儲的精裝房和毛坯房之爭

入行嵌入式應(yīng)該怎么準備?

華芯星重新定義嵌入式存儲品質(zhì)標準

Linux嵌入式和單片機嵌入式的區(qū)別?

Flash閃存技術(shù)是什么?創(chuàng)世SD NAND Flash又有何獨特之處?#嵌入式開發(fā) #存儲芯片 #閃存

飛凌嵌入式2025嵌入式及邊緣AI技術(shù)論壇圓滿結(jié)束

飛凌嵌入式「2025嵌入式及邊緣AI技術(shù)論壇」議程公布

從eMMC到NAND,嵌入式系統(tǒng)存儲的軟件優(yōu)化策略

利用邏輯兼容的嵌入式閃存技術(shù)存儲多級突觸權(quán)重

利用邏輯兼容的嵌入式閃存技術(shù)存儲多級突觸權(quán)重

評論