1、畫定布線區域距PCB板邊≤1mm的區域內,以及安裝孔周圍1mm內,禁止布線;

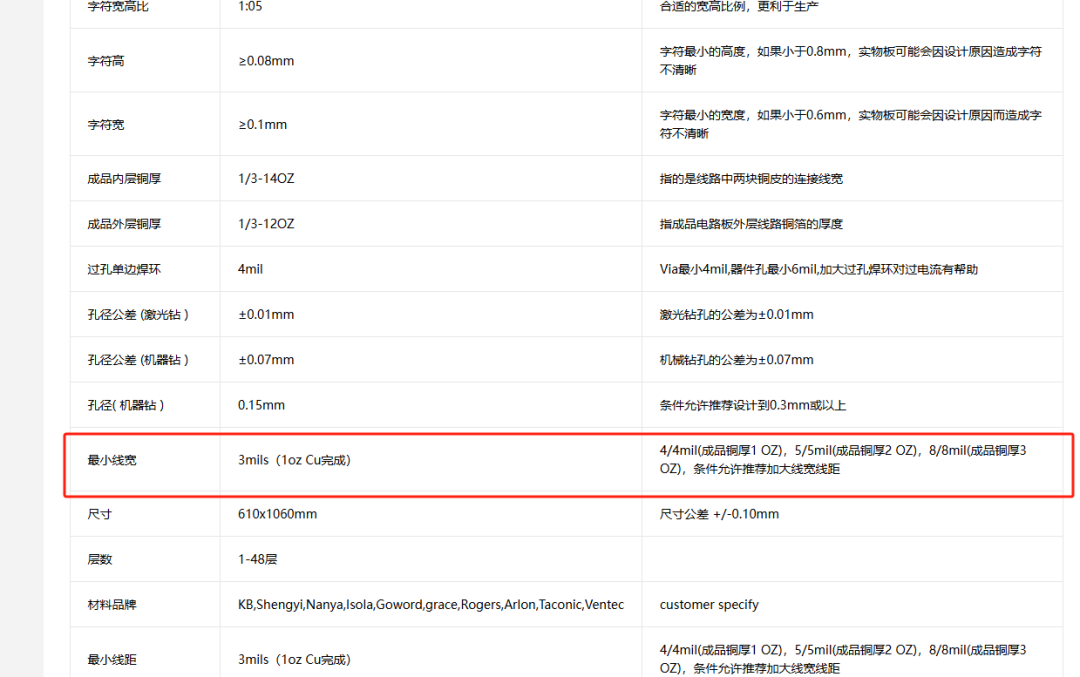

2、電源線盡可能的寬,不應低于18mil;信號線寬不應低于12mil;cpu入出線不應低于10mil(或8mil);線間距不低于10mil;

3、正常過孔不低于30mil;

4、 雙列直插:焊盤60mil,孔徑40mil;

1/4W電阻: 51*55mil(0805表貼);直插時焊盤62mil,孔徑42mil;

無極電容: 51*55mil(0805表貼);直插時焊盤50mil,孔徑28mil;

5、 注意電源線與地線應盡可能呈放射狀,以及信號線不能出現回環走線。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

pcb

+關注

關注

4405文章

23878瀏覽量

424368 -

元器件

+關注

關注

113文章

5004瀏覽量

99680

發布評論請先 登錄

相關推薦

熱點推薦

【「Altium Designer 25 電路設計精進實踐」閱讀體驗】+第六章節 PCB設計

一放,在布局好了之后,布線的時候再設置也不遲

放置器件,可以放在配置規則前面

三、布線

這前面可以先把快捷鍵設置下,方便自己快速有限的布線

發表于 02-26 11:05

PCB中常用的快捷鍵

● M + M 移動元器件

● S + L 兩次左鍵,選中多條線同時走線

● 拖動器件 + L 元器件頂層、底層快速切換

● T + U 刪除全部布線(all)

● J + C在

發表于 01-30 06:01

PCB外觀品質標準判定規則

PCB對PCB長、寬均按照±0.15mm管控。

V-CUT余厚公差:

若無特殊要求,華秋PCB按照板厚的1/3、公差±0.1mm管控,上下刀對位精度±0.1mm。

2、板翹

對于用于表面貼裝

發表于 01-29 14:39

PCB布局布線的相關基本原理和設計技巧

較高,完整的地平面是一定要保證的,此外信號線要保持等長。

18、[問] PCB布線對模擬信號傳輸的影響如何分析,如何區分信號傳輸過程中引入的噪聲是布線導致還是運放器件導致。

[

發表于 11-14 06:11

為了減少電磁干擾,裝置在硬件設計時應該遵循哪些原則?

在硬件設計階段減少電磁干擾(EMI)對電能質量在線監測裝置的影響,需遵循 “ 源頭抑制、路徑阻斷、敏感防護 ” 三大核心邏輯,覆蓋元器件選型、電路拓撲、信號隔離、濾波設計、接地布局、PCB 設計等全

怎么找出PCB光電元器件失效問題

在電子信息產品中,PCB作為元器件的載體與電路信號傳輸的關鍵樞紐,其質量與可靠性對整機設備起著決定性作用。隨著產品小型化及環保要求的提升,PCB正向高密度、高Tg和環保方向發展。然而,受成本和技術

PCB特殊元器件布局策略

在高速PCB設計中,特殊元器件的布局直接影響信號完整性、散熱性能及制造可行性。本文結合行業實踐與工程案例,系統闡述高頻、高壓、重型、熱敏及可調元器件的布局規范與優化方法。 ? 一、高頻元器件

時源芯微 PCB 布線規則詳解

PCB 布線規則詳解 走線方向控制規則 相鄰布線層的走線方向應采用正交結構,避免不同信號線在相鄰層沿同一方向走線,以此降低不必要的層間串擾。若因 P

高層數層疊結構PCB的布線策略

高層數 PCB 的布線策略豐富多樣,具體取決于 PCB 的功能。這類電路板可能涉及多種不同類型的信號,從低速數字接口到具有不同信號完整性要求的多個高速數字接口。從布線規劃和為各接口分配

如何布線才能降低MDDESD風險?PCB布局的抗干擾設計技巧

在現代電子產品日益集成化、小型化的趨勢下,MDDESD(靜電二極管)防護設計變得至關重要。除了元器件選型,PCB的布線與布局也是影響ESD抗擾性能的關鍵因素。作為FAE,本文將結合實戰經驗,分享一些

Altium Designer中PCB設計規則設置

在使用 Altium Designer 進行PCB設計時,除了電氣間距(Clearance)等基礎規則外, 導線寬度、阻焊層、內電層連接、銅皮敷設等規則也同樣重要 。這些設置不僅影響布線

【PCB】四層電路板的PCB設計

摘要 詳細介紹有關電路板的PCB設計過程以及應注意的問題。在設計過程中針對普通元器件及一些特殊元器件采用不同的布局原則;比較手工布線、自動布線

發表于 03-12 13:31

PCB元器件應該遵循哪些布線規則

PCB元器件應該遵循哪些布線規則

評論