SN74TVC3010 10位電壓鉗位器:設計與應用全解析

在當今的電子設計領域,對于高性能、小尺寸且具備可靠保護功能的器件需求日益增長。SN74TVC3010 10位電壓鉗位器便是這樣一款滿足市場需求的優秀產品。本文將深入探討SN74TVC3010的各項特性、應用場景以及設計要點,希望能為電子工程師們在實際設計中提供有價值的參考。

文件下載:SN74TVC3010DW.pdf

產品概述

SN74TVC3010專為電壓限制應用而設計,具有諸多出色特性。它提供了11個帶有公共柵極的并行NMOS傳輸晶體管,低導通電阻使得連接時的傳播延遲極小。其直通式引腳排列方便了印刷電路板的走線布局,還能直接與GTL + 電平接口,并且ESD保護性能超過了JESD 22標準,包括2000 - V人體模型(A114 - A)和1000 - V充電設備模型(C101)。

產品特性與優勢

特性

- 低導通電阻:開關的低導通電阻允許以最小的傳播延遲進行連接,確保信號傳輸的高效性。

- 靈活的參考晶體管選擇:TVC陣列中的所有晶體管具有相同的電氣特性,因此任何一個都可以用作參考晶體管。

- 雙向I/O信號:由于晶體管制造的對稱性,每個位的任一端口連接都可以用作低電壓側,并且I/O信號通過每個FET是雙向的。

- 多種封裝選擇:提供SOIC、SSOP(QSOP)、TSSOP、TVSOP等多種封裝形式,滿足不同設計需求。

優勢

- 易于布局:任何FET都可作為參考晶體管,簡化了布局設計。

- 低電壓偏差:所有FET在一個管芯上,通過嚴格的工藝控制,相對于參考電壓VREF,輸出電壓VO的偏差非常小。

- 無需有源控制邏輯:作為無源器件,不需要邏輯電源(VCC),降低了設計復雜度和功耗。

- 便于走線:直通式引腳排列方便了印刷電路板的走線布局。

- 設計優化:提供不同位寬和封裝的器件,優化了設計和成本效益。

- 設計靈活性:VREF輸入的靈活性允許在不重新設計電路板的情況下遷移到更低電壓的I/O。

技術參數

絕對最大額定值

- 輸入電壓范圍: - 0.5 V至7 V

- 輸入/輸出電壓范圍: - 0.5 V至7 V

- 連續通道電流:128 mA

- 輸入鉗位電流: - 50 mA

- 存儲溫度范圍: - 65°C至150°C

推薦工作條件

| 參數 | 最小值 | 典型值 | 最大值 | 單位 |

|---|---|---|---|---|

| 輸入/輸出電壓(VI/O) | 0 | - | 5 | V |

| 柵極電壓(VGATE) | 0 | - | 5 | V |

| 傳輸晶體管電流(IPASS) | 20 | - | 64 | mA |

| 工作環境溫度(TA) | - 40 | - | 85 | °C |

電氣特性

- 輸入鉗位電壓(VIK):VBIAS = 0,II = - 18 mA時,為 - 1.2 V

- 輸出低電平電壓(VOL):在特定測試條件下為350 mV

- 柵極電容(Ci(GATE)):VI = 3 V或0時為24 pF

- 關態輸入/輸出電容(Cio(off)):VO = 3 V或0時為4 - 12 pF

- 開態輸入/輸出電容(Cio(on)):VO = 3 V或0時為12 - 30 pF

- 導通電阻(ron):在特定測試條件下為12.5 Ω

開關特性

在推薦的工作環境溫度范圍內,VDPU = 2.36 V至2.64 V時,傳播延遲時間tPLH和tPHL的最小值為0 ns,最大值為4 ns。

應用場景與電路設計

應用背景

在個人計算機(PC)架構中,存在行業公認的總線標準,如GTL + 主機總線、AGP圖形端口和PCI本地總線等。然而,許多新的高性能數字集成電路采用先進的亞微米半導體工藝技術制造,其輸入/輸出(I/O)對高電壓狀態的耐受性較低。為了保護這些器件的I/O,需要限制I/O電壓,SN74TVC3010所屬的TI TVC系列便是為此設計的。

電壓限制應用電路

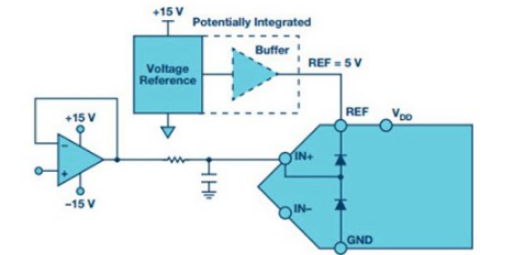

對于電壓限制配置,公共GATE輸入必須連接到任何一個晶體管的一側(A或B),這決定了參考晶體管的VBIAS輸入。VBIAS通過上拉電阻(通常為200 kΩ)連接到VDD電源,建議在VBIAS上使用濾波電容。參考晶體管的另一側用作參考電壓(VREF)連接,VREF輸入必須小于VDDREF - 1 V,以偏置參考晶體管導通。參考晶體管調節所有傳輸晶體管的柵極電壓(VGATE),VGATE由特征柵源電壓差(VGS)決定,因為VGATE = VREF + VGS。傳輸晶體管的低電壓側的高電平電壓限制為最大VGATE - VGS,即VREF。

常見問題解答

Q1:陣列中的任何晶體管都可以用作參考晶體管嗎?

A:是的,只要其VBIAS引腳連接到GATE引腳,任何晶體管都可以用作參考晶體管。

Q2:在數據手冊的推薦工作條件表中,典型VBIAS為3.3 V。VBIAS應該等于或大于參考晶體管上的VREF嗎?

A:VBIAS是由VREF決定的變量。VBIAS通過電阻連接到VDD,以便偏置電壓可以由VREF控制。VDD可以高達5.5 V。參考晶體管上的VREF需要比VDDREF至少低1 V。

Q3:A和B端口都具有5 - V I/O耐受性,還是只有低電壓側具有5 - V I/O耐受性?

A:兩個端口都具有5 - V耐受性。

總結

SN74TVC3010 10位電壓鉗位器為保護對高電壓狀態過沖敏感的I/O電路提供了有效的解決方案。其靈活性使得先進設計能夠在符合行業標準的同時實現低電壓遷移路徑。電子工程師們在設計過程中,可以根據具體需求選擇合適的封裝和參數,充分發揮SN74TVC3010的優勢,提高電路的性能和可靠性。你在使用SN74TVC3010過程中遇到過哪些問題呢?歡迎在評論區分享你的經驗和見解。

-

電子設計

+關注

關注

42文章

2633瀏覽量

49908

發布評論請先 登錄

SN74TVC3010 10 位鉗位電壓

SN74TVC16222A 22 位鉗位電壓

SN74TVC3306 雙路鉗位電壓

SN74TVC3010 10位電壓鉗位器:設計與應用全解析

SN74TVC3010 10位電壓鉗位器:設計與應用全解析

評論