文章來源:十二芯座

原文作者:MicroX

本文介紹了集成電路制造工藝中的COAG技術。

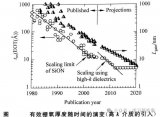

在半導體先進制程的跨代演進中,我們往往將目光聚焦于光刻機(EUV)的波長抑或是晶體管架構(從Planer到FinFET到GAA到CFET)的變革。

然而,在芯片微縮的路上,也有很多其他新技術的出現,例如COAG (Contact Over Active Gate,有源柵極上方接觸) 。COAG技術的出現,正是為了解決先進制程中邏輯單元(Standard Cell)面積縮減遭遇的“拓撲學瓶頸”。

先進制程的布局

在傳統的半導體制造中,晶體管的三個基本電極——源極(Source)、漏極(Drain)和柵極(Gate)——都需要通過金屬接觸孔(Contact)引出,以便與上層的金屬互連線(Interconnects)相連。

傳統非COAG布局的缺陷

在14nm及更早的工藝節點中,柵極接觸孔(Gate Contact)的設計遵循“避讓原則”。由于制造過程中的套刻誤差(Overlay Error)和等離子體刻蝕的局限性,柵極接觸孔必須放置在有源區(Active Area)之外,即位于淺溝槽隔離(STI)區域的上方。

這種布局導致了嚴重的面積浪費:

橫向間距限制:為了防止接觸孔在刻蝕時誤傷柵極邊緣或引起源漏極短路,必須在柵極和接觸孔之間留出足夠的安全間距(Registration Margin)。

單元高度(Cell Height)膨脹:由于接觸點在側方,邏輯單元的高度必須增加,以容納這些額外的接觸區。可以稱之為“空間稅”,直接限制了晶體管密度(MTr/mm2)的提升。

COAG技術

COAG技術的本質是將原本“橫向并列”的布局改為“縱向堆疊”。它允許接觸孔直接落在有源柵極(Active Gate)的正上方。

物理架構的拓撲演進

在COAG架構下,晶體管的平面布局發生了根本性變化。通過取消側方的接觸區,邏輯單元的高度得到壓縮。

Track Height(繞線軌道高度)的突破:從傳統的9T(9條金屬線軌道)降低到6T甚至5T。這意味著在同樣的芯片面積下,可以容納多出30%以上的邏輯門。

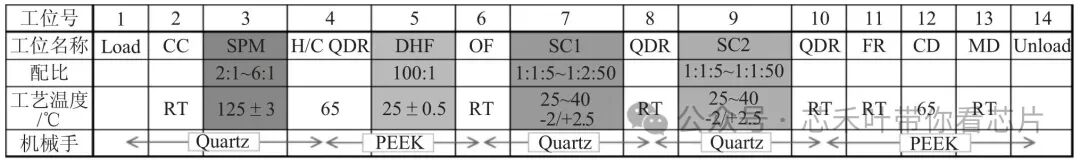

自對準策略(Self-Aligned Strategy)

COAG的實現依賴于自對準工藝(Self-Aligned Contact, SAC)。在制造過程中,工程師首先在柵極金屬上方沉積一層非常薄但極其堅硬的絕緣保護層(通常是氮化硅或特殊的低k材料掩模)。

選擇性刻蝕:當進行接觸孔刻蝕時,化學試劑和等離子體能夠區分“層間介質”和“柵極保護層”。刻蝕過程會自動在碰到柵極保護層時“減速”或“停止”,從而確保孔洞精準地落在柵極頂部而不向四周偏移,避免了災難性的短路。

鈷(Cobalt)互連:解決寄生電阻

隨著接觸孔(Contact Via)的直徑縮小到10nm以下,傳統的金屬插塞材料——鎢(Tungsten)遇到了巨大的瓶頸。

鈷的優勢:Intel在10nm節點率先在大規模量產中引入鈷替代鎢作為M0層和接觸孔材料。鈷具有更長的平均電子自由程和流動性,能夠完美填充高深寬比的COAG孔洞,且電阻率遠低于同尺寸下的鎢。這解決了COAG結構因接觸面積減小可能導致的信號延遲(RC Delay)問題。

未來挑戰

盡管COAG成功將摩爾定律延續到了3nm節點,但隨著制程向2nm(18A)演進,物理極限再次降臨。

1. 散熱與可靠性的博弈

由于接觸點直接位于晶體管最熱的部分(柵極)上方,熱量散發的路徑變得更加擁擠。在高頻運行下,COAG結構可能產生微小的熱應力,導致介質層開裂。未來的研究重點在于尋找具有更高導熱率的絕緣掩模材料。

2. 與背面供電(BSPDN)的結合

在2nm節點,Intel的PowerVia和臺積電的背面供電技術將徹底改變互連架構。屆時,電源線將移至晶圓背面,而正面的空間將完全留給信號線和COAG結構。

3. CFET

在1nm節點,n型和p型晶體管將垂直堆疊(CFET)。在這種情況下,COAG將演變為一種復雜的“3D垂直通孔”技術,不僅要在柵極上方接觸,還要在多層堆疊的柵極之間進行選擇性接觸。

參考文獻

1.Intel

2.VLSI 2024

3. Razavieh, A., et al, “FinFET with Contact over Active-Gate for 5G Ultra-Wideband Applications”, VLSI 2020 Symposium, paper JFS2.5.

-

集成電路

+關注

關注

5462文章

12659瀏覽量

375520 -

半導體

+關注

關注

339文章

31155瀏覽量

266076 -

制造工藝

+關注

關注

2文章

215瀏覽量

21315

原文標題:COAG(Contact Over Active Gate)技術原理與工藝演進

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

集成電路制造工藝中的COAG技術介紹

集成電路制造工藝中的COAG技術介紹

評論