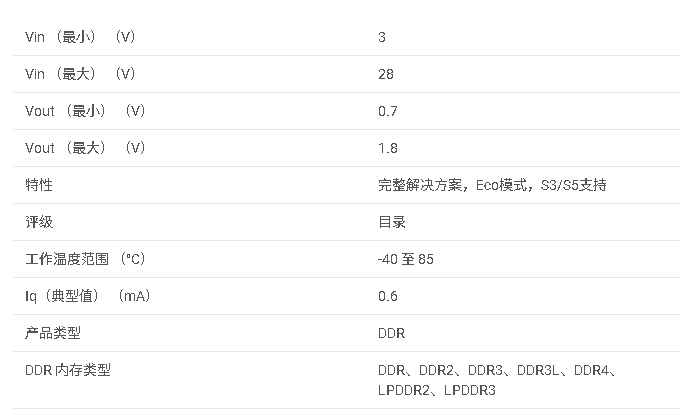

探秘ICSSSTUF32864A:DDR2內(nèi)存模塊的理想選擇

一、引言

在DDR2內(nèi)存模塊的設(shè)計領(lǐng)域,尋找一款性能卓越、功能豐富且能提供完整解決方案的緩沖器至關(guān)重要。ICSSSTUF32864A作為Circuit Systems, Inc.推出的一款25位可配置寄存器緩沖器,無疑是DDR2 400、533和667內(nèi)存模塊的理想之選。今天,我們就來深入了解這款產(chǎn)品的特性、功能及應(yīng)用。

文件下載:SSTUF32864AHLF.pdf

二、產(chǎn)品特性剖析

1. 靈活的配置模式

ICSSSTUF32864A支持25位1:1或14位1:2的可配置寄存器緩沖器模式。這種靈活的配置方式,能夠根據(jù)不同的應(yīng)用需求進(jìn)行調(diào)整,為DDR2內(nèi)存模塊的設(shè)計提供了更多的可能性。

2. 電氣兼容性

- 數(shù)據(jù)輸入輸出:支持SSTL_18 JEDEC規(guī)范,確保了數(shù)據(jù)傳輸?shù)姆€(wěn)定性和兼容性。

- 控制輸入:C0、C1和RESET#輸入采用LVCMOS開關(guān)電平,這種設(shè)計使得控制信號的處理更加高效和準(zhǔn)確。

3. 低電壓操作

該產(chǎn)品的工作電壓范圍為(V_{DD}=1.7V)至1.9V,低電壓操作不僅降低了功耗,還提高了產(chǎn)品的穩(wěn)定性和可靠性。

4. 封裝形式

采用96 BGA封裝,這種封裝形式具有良好的散熱性能和電氣性能,同時還能實現(xiàn)與ICSSSTUF32866的直接替換,方便工程師進(jìn)行設(shè)計和升級。此外,還有綠色環(huán)保封裝可供選擇,符合環(huán)保要求。

三、真值表與引腳配置

1. 真值表

真值表詳細(xì)列出了不同輸入組合下的輸出狀態(tài),為工程師提供了清晰的邏輯控制依據(jù)。例如,當(dāng)RST#為高電平,DCS#和CSR#為低電平時,根據(jù)輸入數(shù)據(jù)Dn、DODT、DCKE的不同,輸出Qn、QCS#、QODT、QCKE會有相應(yīng)的狀態(tài)變化。這有助于工程師在設(shè)計過程中準(zhǔn)確控制輸出信號。

2. 引腳配置

- 96球BGA封裝:提供了詳細(xì)的引腳分配信息,包括電源引腳(VDD、GND)、時鐘引腳(CK、CK#)、控制引腳(C0、C1、RST#等)和數(shù)據(jù)引腳(Dn、Qn等)。不同的配置模式(1:1、1:2 Register A、1:2 Register B)下,引腳的功能和分配會有所不同,工程師需要根據(jù)具體的設(shè)計需求進(jìn)行選擇。

四、工作原理與特性

1. 時鐘與數(shù)據(jù)處理

ICSSSTUF32864A采用差分時鐘(CK和CK#)進(jìn)行操作,數(shù)據(jù)在CK上升沿和CK#下降沿進(jìn)行注冊。這種設(shè)計方式能夠有效提高數(shù)據(jù)傳輸?shù)臏?zhǔn)確性和穩(wěn)定性。

2. 配置控制

- C0輸入:控制1:2引腳配置從A配置(低電平)到B配置(高電平)的切換。

- C1輸入:控制引腳配置從25位1:1(低電平)到14位1:2(高電平)的切換。

3. 低功耗待機(jī)操作

當(dāng)復(fù)位輸入(RST#)為低電平時,差分輸入接收器被禁用,允許未驅(qū)動(浮動)的數(shù)據(jù)、時鐘和參考電壓(VREF)輸入。同時,所有寄存器被復(fù)位,所有輸出被強(qiáng)制為低電平。在DDR-II RDIMM應(yīng)用中,RST#與CK和CK#完全異步,在復(fù)位和退出復(fù)位時,能夠確保輸出的穩(wěn)定性,避免出現(xiàn)毛刺。

4. 輸出控制

該產(chǎn)品會監(jiān)測DCS#和CSR#輸入,當(dāng)兩者都為高電平時,會禁止Qn輸出狀態(tài)的改變;只要其中一個為低電平,Qn輸出將正常工作。RST輸入具有最高優(yōu)先級,會強(qiáng)制輸出為低電平。如果不需要DCS#控制功能,可以將CSR#輸入硬接地,此時DCS#的建立時間要求與其他D數(shù)據(jù)輸入相同。

五、電氣特性與參數(shù)

1. 絕對最大額定值

包括存儲溫度(–65°C至 +150°C)、電源電壓(-0.5V至2.5V)、輸入電壓(-0.5V至 +2.5V)等參數(shù)。這些參數(shù)規(guī)定了產(chǎn)品能夠承受的最大應(yīng)力范圍,超過這些范圍可能會導(dǎo)致設(shè)備永久性損壞。

2. 推薦工作條件

- 電源電壓:(V_{DD})為1.7V至1.9V,典型值為1.8V。

- 參考電壓:(V{REF})為0.49 x (V{DD})至0.51 x (V{DD}),典型值為0.5 x (V{DD})。

- 輸入電壓:(V{I})范圍為0至(V{DD}),不同類型的輸入(如DC、AC)有不同的高低電平要求。

3. 直流電氣特性

包括輸入鉗位電壓((V{IK}))、輸出高電平電壓((V{OH}))、輸出低電平電壓((V{OL}))、輸入電流((I{I}))、電源電流((I_{DD}))等參數(shù)。這些參數(shù)反映了產(chǎn)品在直流狀態(tài)下的電氣性能。

4. 時序要求

- 時鐘頻率:最大為335 MHz。

- 脈沖持續(xù)時間:CK、CK高或低的脈沖持續(xù)時間最小為1 ns。

- 差分輸入激活時間:最大為10 ns。

- 差分輸入非激活時間:最大為15 ns。

- 建立時間和保持時間:不同輸入信號相對于時鐘的建立時間和保持時間有具體要求,如DCS在CK下降沿前的建立時間等。

5. 開關(guān)特性

包括最大頻率((f{max}))、傳播延遲時間((t{PDM})、(t_{PDMSS}))等參數(shù),這些參數(shù)反映了產(chǎn)品在開關(guān)狀態(tài)下的性能。

6. 輸出緩沖特性

輸出邊沿速率((dV/dt_r)、(dV/dtf))最小為4 V/ns,上升沿和下降沿速率之差((dV/dt?))為1 V/ns。

六、應(yīng)用與總結(jié)

ICSSSTUF32864A憑借其靈活的配置模式、良好的電氣兼容性、低電壓操作和豐富的功能特性,為DDR2內(nèi)存模塊的設(shè)計提供了完整的解決方案。在實際應(yīng)用中,工程師可以根據(jù)具體的設(shè)計需求,合理選擇配置模式和引腳連接方式,確保產(chǎn)品的性能和穩(wěn)定性。同時,需要嚴(yán)格遵守產(chǎn)品的電氣參數(shù)和時序要求,以避免出現(xiàn)電氣故障和信號干擾。大家在使用這款產(chǎn)品的過程中,有沒有遇到過什么有趣的問題或者獨特的應(yīng)用場景呢?歡迎在評論區(qū)分享交流。

-

緩沖器

+關(guān)注

關(guān)注

6文章

2236瀏覽量

49022

發(fā)布評論請先 登錄

ICSSSTUF32866E:DDR2內(nèi)存模塊的理想配置緩沖器

ICSSSTUB32S868D:DDR2的28位可配置寄存器緩沖器

探索ICSSSTUB32872A:28位DDR2寄存器緩沖器的技術(shù)剖析

ICSSSTUB32866B:DDR2可配置寄存器緩沖器的技術(shù)解析

探索ICSSSTUB32864A:DDR2的理想可配置緩沖器

Renesas ICSSSTUAF32869A:DDR2的14位可配置寄存器緩沖器

ICSSSTUA32866B:DDR2可配置寄存器緩沖器的全面解析

探索ICSSSTUA32864B:DDR2內(nèi)存模塊的理想配置寄存器緩沖器

解讀 IDT74SSTUBF32868A:DDR2 應(yīng)用的 28 位可配置寄存器緩沖器

IDT74SSTU32864/A/C/D/G:1.8V SSTL I/O的1:1與1:2寄存器緩沖器

GK7202V300 DDR2內(nèi)存替代方案(CSS6404LS-LI QSPI pSRAM)

MAX17000:DDR2和DDR3內(nèi)存電源管理解決方案的卓越之選

MAX17000A:DDR2和DDR3內(nèi)存電源管理的理想之選

74SSTUB32868:DDR2注冊DIMM的理想緩沖器

TPS51916 DDR2/3/3L/4 內(nèi)存電源解決方案同步降壓控制器數(shù)據(jù)手冊

探秘ICSSSTUF32864A:DDR2內(nèi)存模塊的理想選擇

探秘ICSSSTUF32864A:DDR2內(nèi)存模塊的理想選擇

評論