文章來源:十二芯座

原文作者:MicroX

本文圖解介紹了GAAFET(Gate-All-Around FET)的制造流程。

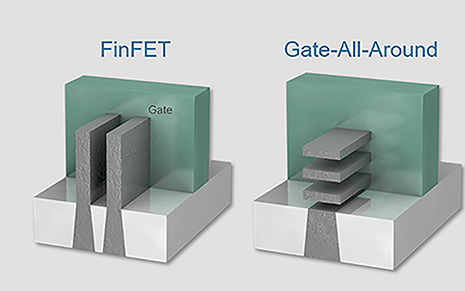

隨著集成電路制程邁向3nm及以下節(jié)點,F(xiàn)inFET(鰭式場效應(yīng)晶體管)由于三面柵控能力的局限,難以抑制嚴重的短溝道效應(yīng)。

GAAFET(Gate-All-Around FET)通過將柵極完全包裹在納米片(Nanosheet)通道四周,實現(xiàn)了近乎完美的電子控制。

超晶格生長(Superlattice Epitaxy)

制造始于在硅襯底上交替生長Si(硅)和SiGe(硅鍺)的多層外延結(jié)構(gòu)。

工藝細節(jié):使用化學(xué)氣相沉積(CVD)精確控制每層厚度。

邏輯:SiGe層僅作為“犧牲層”,為后續(xù)騰出空間;Si層則是最終的電子通道。

鰭片刻蝕與淺溝槽隔離(Fin Etch & STI)

與FinFET類似,通過光刻和干法刻蝕將超晶格結(jié)構(gòu)切割成條狀。

挑戰(zhàn):刻蝕必須保持極高的垂直度,確保多層Si/SiGe堆疊結(jié)構(gòu)的側(cè)壁平整。

Dummy Gate 形成

內(nèi)側(cè)墻形成(Inner Spacer Formation)

這是GAA工藝中最獨特的一步。在沉積 Dummy Gate 后,需要側(cè)向刻蝕掉一部分SiGe層,并填充介電材料形成內(nèi)側(cè)墻。

作用:內(nèi)側(cè)墻將源/漏極(Source/Drain)與金屬柵極隔離開,極大降低了寄生電容(Cgs/Cgd)。

技術(shù)難點:必須使用極高選擇比的各向同性刻蝕,確保只移除預(yù)定深度的SiGe,而不損傷Si層。

源漏區(qū)外延

SiGe/ SiP EPI

納米片釋放(Channel Release)

在替換金屬柵(RMG)工藝中,通過高選擇比的濕法或干法刻蝕徹底清除所有的SiGe層,使Si納米片如同“懸空的橋”一般懸掛在源漏之間。

物理瓶頸:此時納米片極其脆弱,表面張力可能導(dǎo)致納米片塌陷粘連(Stiction)。

高K金屬柵(HKMG)沉積

最后,利用原子層沉積(ALD)技術(shù),將高K電介質(zhì)和金屬柵極材料“塞進”納米片之間的極小縫隙(通常小于10nm)。

均勻性要求:ALD必須保證在納米片的頂面、底面和側(cè)面均勻成膜,實現(xiàn)全環(huán)繞包裹。

Contact 形成

-

集成電路

+關(guān)注

關(guān)注

5462文章

12659瀏覽量

375512 -

晶體管

+關(guān)注

關(guān)注

78文章

10431瀏覽量

148435 -

FinFET

+關(guān)注

關(guān)注

12文章

262瀏覽量

92346

原文標(biāo)題:GAAFET(全環(huán)繞柵極晶體管)制造流程圖解

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

應(yīng)用材料公司以技術(shù)助力極紫外光和三維環(huán)繞柵極晶體管實現(xiàn)二維微縮

互補場效應(yīng)晶體管的結(jié)構(gòu)和作用

下一代高速芯片晶體管解制造問題解決了!

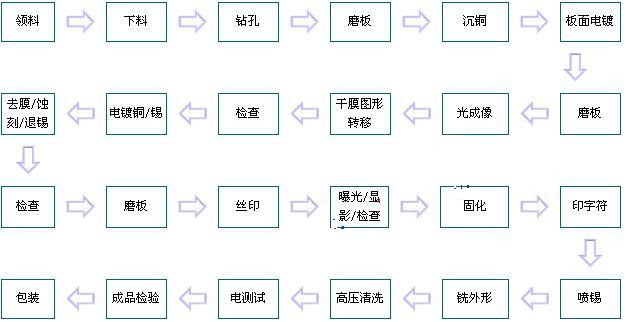

雙面板制作流程及鍍金、噴錫和FPC板流程圖解

鍍金、噴錫和FPC板流程圖解

三星推GAAFET技術(shù) 將基于它打造3nm芯片

如何生產(chǎn)3納米以下全環(huán)繞柵極晶體管?

臺積電2nm芯片計劃于2025年實現(xiàn)量產(chǎn)

臺積電2nm芯片將采用GAAFET技術(shù)

全環(huán)繞柵極晶體管將如何改變半導(dǎo)體行業(yè)

鰭式場效應(yīng)晶體管制造工藝流程

GAAFET全環(huán)繞柵極晶體管制造流程圖解

GAAFET全環(huán)繞柵極晶體管制造流程圖解

評論