ISL6551:零電壓開關全橋PWM控制器的設計與應用剖析

在電子工程師的日常工作中,電源管理芯片的選擇和使用是至關重要的環節。今天就來深入探討一下Intersil公司的ISL6551零電壓開關(ZVS)全橋PWM控制器,它在隔離電源系統的設計中能發揮怎樣的作用呢?

文件下載:ISL6551EVAL1.pdf

一、ISL6551概述

ISL6551 是專門為隔離電源系統設計的ZVS全橋PWM控制器。它采用了獨特的固定頻率ZVS電流模式控制算法,不僅能實現高效率的轉換,還能有效降低電磁干擾(EMI)。其兩個下驅動采用后沿PWM控制并帶有諧振延遲,而上驅動則以固定50%的占空比驅動。

這個芯片集成了眾多實用的功能,并封裝在28引腳的SOIC封裝中,為電源設計提供了一個完整而復雜的解決方案。它可以用于全橋和推挽轉換器,適用于離線電源、電信/數據通信電源以及高端微處理器和服務器電源等多種應用場景。

二、關鍵特性解析

(一)控制特性

- 可編程軟啟動:通過CSS引腳外接電容,利用內部電流源對電容充電,將充電電壓輸入誤差放大器的控制引腳,從而控制電源的輸出電壓和電流,實現受控啟動。軟啟動時間和輸出上升時間可以通過相關公式計算,如 (t{ss}=frac{V{clamp} × C{ss}}{I{ss}}) ( (t{ss}) 為軟啟動時間, (V{clamp}) 為鉗位電壓, (C{ss}) 為外接電容, (I{ss}) 為充電電流)。

- 可編程諧振延遲:通過RRESDLY引腳外接電阻來設置諧振延遲,范圍為50ns - 500ns。諧振延遲可以確保在相應的上FET關斷后,下FET有合適的開通時間,避免上下FET同時導通產生直通電流,計算公式為 (RESDLY = 4.01 × R{-}RESDLY / kΩ + 13 (ns)) 。

- 可編程前沿消隱:在電流模式控制中,橋路中的寄生元件會產生尖峰信號,可能導致PWM比較器誤觸發。通過RLEB引腳外接電阻可以設置前沿消隱時間,范圍為50ns - 300ns,有效避免誤觸發,計算公式為 (t{LEB}=2 × R _LEB / kΩ + 15( ns)) 。

- 可調斜坡補償:通過RRA引腳調整斜坡電壓,為PWM邏輯提供合適的信號,確保斜坡電壓始終高于OAGS(地感應運算放大器)的最小電壓,實現穩定的控制。斜坡電壓的計算公式為 (V{ramp}= BGREF × dt / (R _RA × 500E - 12)(V)) ,其中 (dt = Duty Cycle / f{SW}-t{LEB}) 。

- 同步整流驅動信號:SYNC1和SYNC2引腳提供用于實現同步整流的驅動信號,能在高輸出電流、超高效率應用中發揮作用。它們可驅動最大20pF的容性負載,在1MHz時鐘頻率(500kHz開關頻率)下工作。

- 電流共享支持:通過SHARE引腳和CS_COMP引腳實現電流共享,可支持多達10個單元并聯。主單元以最高參考電壓工作,從單元通過源電阻調整參考電壓以匹配主單元,實現負載電流的共享。

(二)保護特性

- 可調逐周期峰值電流限制:通過PKILIM引腳設置過流限制,當該引腳電壓超過BGREF電壓時,門脈沖終止并保持低電平,直到下一個時鐘周期。通常將峰值電流關斷閾值設置得略高于正常的逐周期PWM峰值電流限制(Vclamp),一般在短路情況下才會觸發。

- 快速短路保護(打嗝模式):當轉換器輸出過載時,PKILIM引腳電壓高于BGREF電壓,軟啟動電容快速放電,所有驅動器關閉。之后軟啟動電容緩慢充電,如果再次過載則又快速放電,只要過載條件持續,就會一直處于打嗝模式,直到過載消除,轉換器恢復正常工作。

- 鎖存關斷輸入:LATSD引腳為鎖存關斷輸入,當該引腳電壓大于3V時,IC被鎖存關閉,進入低功耗模式,只有在完全移除VDD引腳的電源后才能復位,ON/OFF引腳無法復位該鎖存。此功能可用于在輸出過壓或其他不良條件下鎖斷電源。

- 非鎖存使能輸入:ON/OFF引腳為非鎖存使能輸入,高電平標準TTL輸入(對VDD電平也安全)信號可使控制器開啟,低電平則關閉控制器并終止所有驅動信號,包括SYNC輸出,同時軟啟動復位。該引腳可在監測轉換器輸入電壓和熱狀態時接收使能命令。

- VDD欠壓鎖定(UVLO):UVLO確保VDD電壓高于開啟閾值 (VDD{ON}) 時IC有序啟動,在鎖定期間所有驅動器保持低電平,并且帶有滯后電壓 (VDD{HYS}) ,防止上電時多次啟動/關斷。該功能不適用于VDD1和VDD2。

三、技術參數分析

(一)絕對最大額定值

ISL6551的電源電壓VDD、VDDP1、VDDP2范圍為 - 0.3V至16V;使能輸入(ON/OFF、LATSD)的電壓不能超過VDD;電源良好灌電流(IDCOK)最大為5mA;ESD人體模型評級為3kV,機器模型評級為250V。在實際使用中,一定要注意不要讓芯片工作在或接近這些最大額定值,否則可能會影響產品的可靠性并導致不在保修范圍內的故障。

(二)推薦工作條件

環境溫度范圍根據不同型號有所不同,如ISL6551IB為0°C至 + 85°C,ISL6551AB為 - 40°C至 + 105°C;VDD電源電壓范圍為10.8V至13.2V,VDDP1和VDDP2電源電壓小于13.2V;最大工作結溫為 + 125°C。

(三)電氣規格

不同參數在特定條件下有相應的電氣性能要求,例如:

- 電源參數:VDD電源電壓典型值為12V,ISL6551IB和ISL6551AB的偏置電流有所不同,在VDD = 12V時,ISL6551IB的偏置電流典型值為13mA,ISL6551AB為3mA。

- 時鐘發生器:頻率范圍為100kHz至1000kHz,死區時間脈沖寬度范圍為50ns至1000ns。

- 帶隙參考:帶隙參考電壓在不同型號下有一定的公差范圍,如ISL6551IB在 (V_{D D}=12 V) ,399kΩ上拉, (0.1 mu F) 電容且經過修整后,范圍為1.250V至1.280V。

四、應用電路設計

(一)電源系統架構

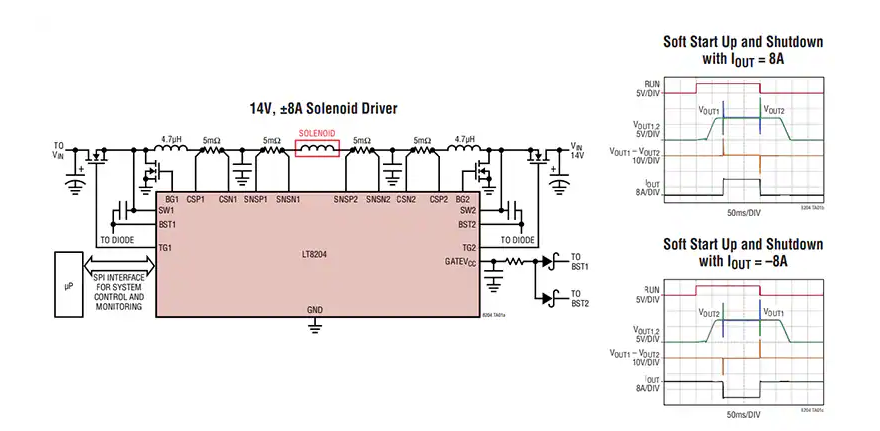

ISL6551在電源系統中可以作為全橋或推挽PWM控制器,結合其他外部元件如變壓器、脈沖變壓器、電容、電感和肖特基或同步整流器等,構成完整的電源解決方案。推薦采用“二次側控制”以充分利用其集成特性。

(二)各部分電路分析

- 輸入濾波:一般需要輸入電容來吸收功率開關(FET)的脈動電流。為了獲得良好的EMI性能,可以使用輸入L - C濾波器來降低反射回輸入線的紋波電流,過濾差模噪聲,其工作頻率為開關頻率的兩倍,即時鐘頻率(Fclock)。在某些情況下,可能還需要額外的共模扼流圈來過濾共模噪聲。

- 電流檢測:有兩種檢測方法,一種是檢測流經兩個下初級FET的電流,另一種是檢測流經兩個上初級FET的電流之和。在初級側控制系統中,還可以使用低阻抗功率電阻來檢測電流。無論采用哪種方法,都要確保檢測點的連接盡可能靠近相關元件,以保證檢測的準確性。

- 初級FET:全橋轉換器需要四個MOSFET,其漏 - 源極電壓額定值為 (V{IN}) ;推挽轉換器只需要兩個下MOSFET,兩個上驅動不使用,MOSFET的 (v{DS}) 為 (2 × V_{I N}) 。

- 反饋電路:在二次側控制系統中,只需要幾個電阻和電容就能完成反饋回路;而在初級側控制系統中,需要使用光耦進行隔離,但其帶寬會受到光耦的限制。

- 整流器:對于低輸出電壓、高輸出電流和/或高效率應用,可以使用同步FET;對于較低電流應用,則使用肖特基二極管。整流器的連接方式有電流倍增整流器、常規整流器和自驅動整流器等多種,需要根據具體的應用場景進行選擇。

- 主變壓器:不同的拓撲結構對主變壓器的要求不同,如全橋和電流倍增器拓撲不需要次級中心抽頭,次級繞組承載一半的負載;常規全橋拓撲需要次級中心抽頭,次級繞組承載全部負載等。

- 輸出濾波:電流倍增濾波器需要兩個電感,但可以集成并耦合到一個磁芯中,每個電感在開關頻率下承載一半的負載;常規濾波器只需要一個電感,該電感在兩倍開關頻率下承載全部負載。

五、總結與思考

ISL6551 作為一款功能強大的ZVS全橋PWM控制器,為電源系統設計提供了豐富的功能和靈活的配置選項。在實際應用中,電子工程師需要根據具體的設計要求,合理設置各個參數,選擇合適的外部元件和電路拓撲結構,以實現高效率、高可靠性的電源設計。

大家在使用ISL6551的過程中,有沒有遇到過什么獨特的問題或者有什么創新的應用思路呢?歡迎在評論區分享交流。

-

電源系統設計

+關注

關注

0文章

19瀏覽量

3267

發布評論請先 登錄

ISL6551:零電壓開關全橋PWM控制器的設計與應用剖析

ISL6551:零電壓開關全橋PWM控制器的設計與應用剖析

評論