深入解析AD5504:高電壓四通道12位電壓輸出DAC

在電子設計領域,數模轉換器(DAC)是連接數字世界與模擬世界的關鍵橋梁。今天我們要深入探討的是Analog Devices推出的AD5504,一款高電壓四通道12位電壓輸出DAC,它在諸多應用場景中展現出卓越的性能。

文件下載:AD5504.pdf

一、AD5504概述

1.1 產品特性

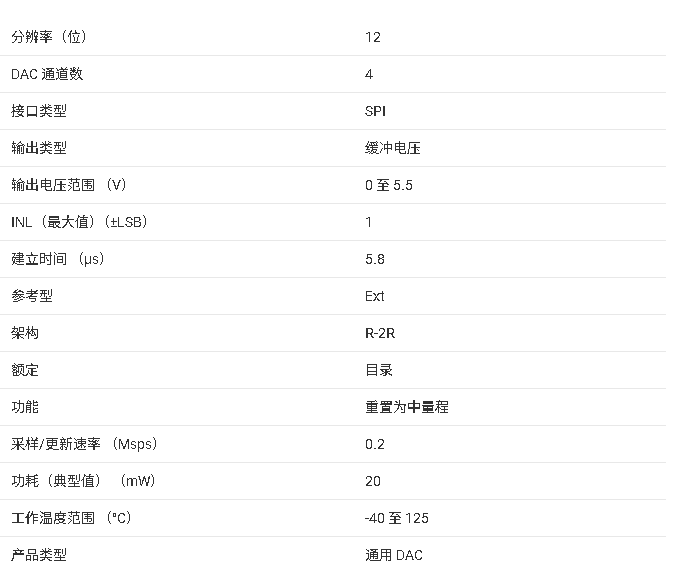

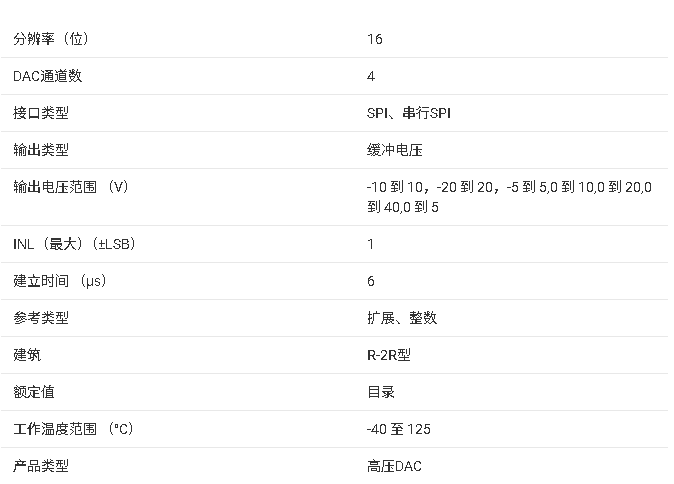

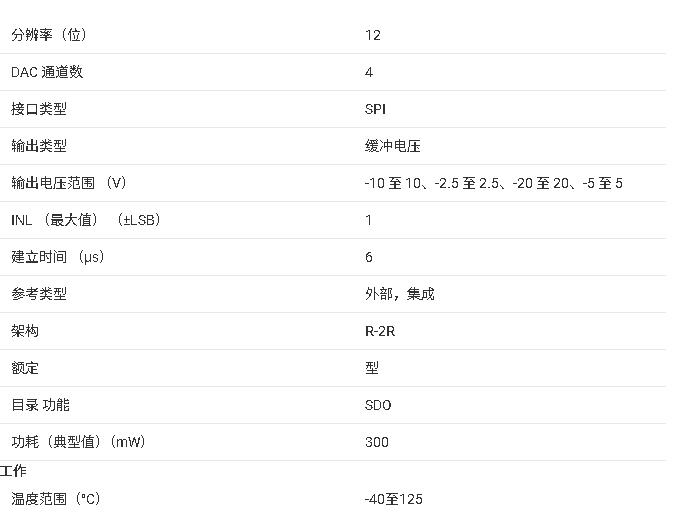

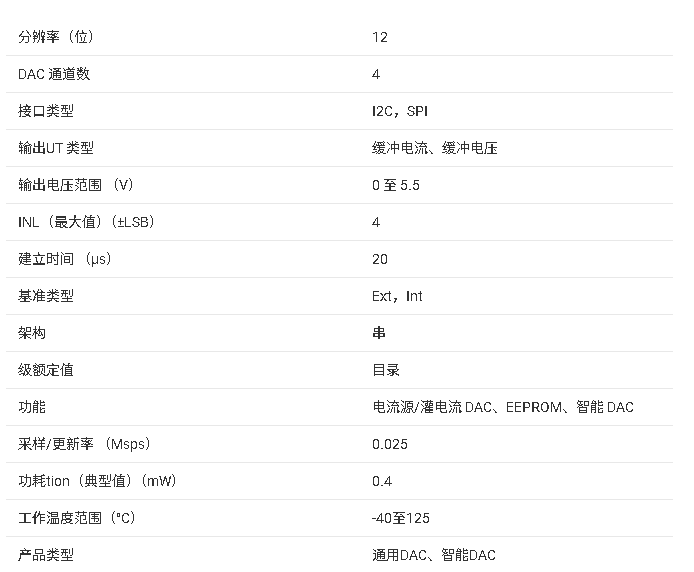

- 多通道與高分辨率:AD5504具備四通道輸出,分辨率高達12位,能夠滿足高精度的模擬信號輸出需求。

- 輸出范圍靈活:通過引腳 (R_{SEL}) 可選擇30V或60V的輸出范圍,為不同應用提供了極大的靈活性。

- 集成功能豐富:集成了精密參考源、溫度傳感器報警功能和上電復位功能,同時具備低功耗串行接口和讀回能力,還支持通過LDAC實現同步更新。

- 寬溫度范圍:可在 -40°C 至 +105°C 的寬溫度范圍內穩定工作,適應各種惡劣環境。

1.2 應用領域

- 可編程電壓源:為需要精確電壓控制的系統提供穩定的電壓輸出。

- 高電壓LED驅動:滿足高電壓LED的驅動需求,確保LED的穩定發光。

- 光通信中的接收器偏置:為光通信系統中的接收器提供合適的偏置電壓,保證信號的準確接收。

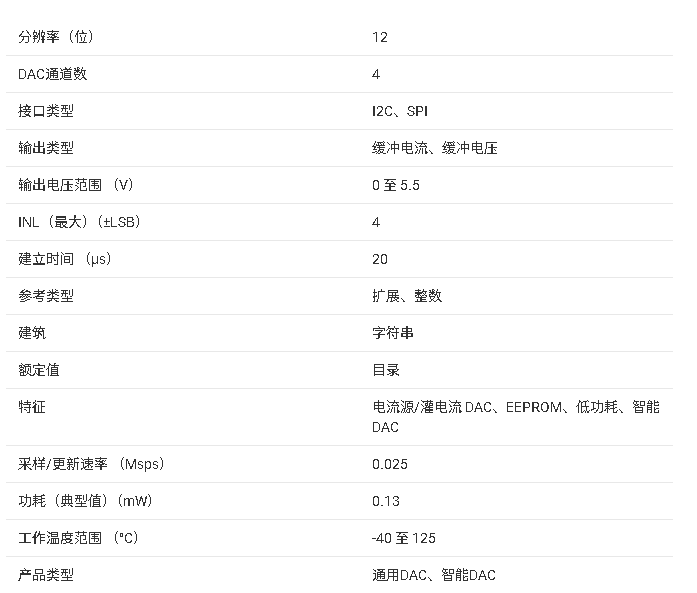

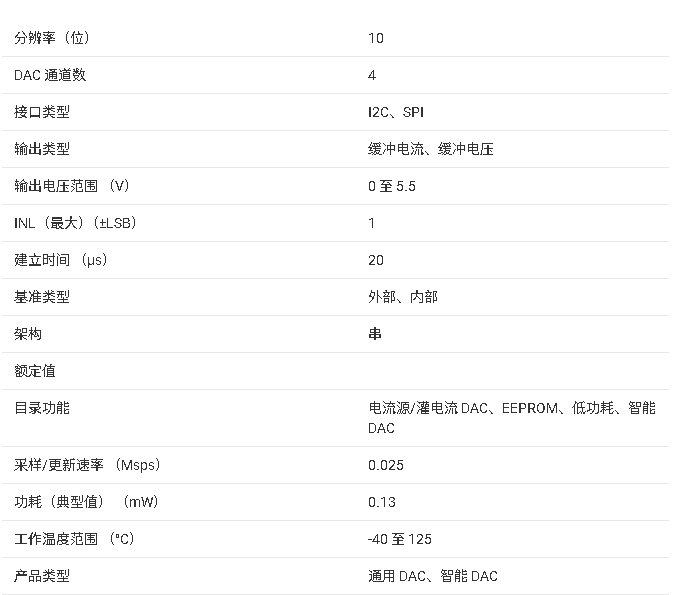

二、技術參數詳解

2.1 電氣特性

- 精度指標:分辨率為12位,差分非線性(DNL)在 -1 至 1 LSB 之間,積分非線性(INL)在不同模式下有不同的范圍,如60V模式下為 -2 至 +2 LSB,30V模式下為 -3 至 +3 LSB。

- 溫度系數:輸出電壓溫度系數為 50 ppm/°C(DAC代碼為半量程),增益溫度系數為 10 ppm of FSR/°C(60V模式)。

- 誤差指標:零刻度誤差(VZSE)最大為100 mV,滿刻度誤差(VFSE)在不同溫度區間有不同表現,增益誤差在 -0.6% 至 +0.6% of FSR 之間。

- 輸出特性:輸出電壓范圍為 AGND + 0.5 V 至 (V_{DD}-0.5 ~V),短路電流為 2 mA,直流輸出阻抗為 3 Ω,直流輸出泄漏電流為 10 μA。

2.2 交流特性

- 輸出電壓建立時間:30V模式下為 45 μs,60V模式下為 25 μs(? 至 ? 量程,±1 LSB 建立)。

- 壓擺率:為 0.65 V/μs。

- 數字到模擬毛刺能量:在60V模式下為 300 nV - s。

- 噪聲指標:峰 - 峰值噪聲在 0.1 Hz 至 10 Hz 范圍內為 140 μV p - p,在 0.1 Hz 至 10 kHz 范圍內為 1 mV p - p(DAC代碼為 0x800)。

2.3 時序特性

AD5504的時序特性對于正確的數據傳輸和操作至關重要。例如,SCLK 周期時間最小為 60 ns,SCLK 高電平時間和低電平時間最小均為 10 ns 等。這些時序參數確保了數據的準確讀寫和設備的穩定運行。

2.4 絕對最大額定值

- 電壓范圍:(V{DD}) 為 -0.3V 至 +64V,(V{LOGIC}) 為 -0.3V 至 +7V,(V{OUTx}) 為 -0.3V 至 (V{DD}+0.3V) 等。

- 溫度范圍:最大結溫為 150°C,存儲溫度范圍為 -65°C 至 +150°C。

2.5 熱阻

16引腳TSSOP封裝的熱阻 (theta_{JA}) 為 112.60 °C/W,在設計散熱方案時需要考慮這一參數,以確保設備在正常溫度范圍內工作。

三、工作原理

3.1 電源上電狀態

上電時,上電復位電路將控制寄存器的位清零為 0x40,使模擬部分初始處于掉電狀態,降低功耗。用戶可以在僅消耗 30 μA 電源電流的情況下對 DAC 寄存器進行編程。

3.2 掉電模式

每個 DAC 通道可以通過編程控制寄存器單獨上電或掉電。掉電時,相關的模擬電路關閉以降低功耗,數字部分保持上電狀態。DAC 放大器的輸出可以通過控制寄存器的 Bit C6 設置為三態或通過內部 20 kΩ 電阻連接到 AGND。

3.3 DAC 通道架構

單個 DAC 通道由一個 12 位電阻串 DAC 后跟一個輸出緩沖放大器組成。電阻串結構保證了 DAC 的單調性,12 位二進制數字代碼決定了從電阻串上的哪個節點提取電壓,輸出放大器將 DAC 輸出電壓放大以實現 0V 至 30V 或 0V 至 60V 的固定線性電壓輸出范圍。

3.4 輸出范圍選擇

通過 (R{SEL}) 引腳選擇 DAC 的輸出范圍。當 (R{SEL}) 連接到邏輯 1 時,輸出范圍為 0V 至 30V;當 (R{SEL}) 連接到邏輯 0 時,輸出范圍為 0V 至 60V。在串行接口不使用時可以隨時更改 (R{SEL}) 的狀態。

3.5 CLR 功能

(CLR) 引腳是異步清零輸入,下降沿敏感。當 (CLR) 為低電平時,所有 LDAC 脈沖被忽略,輸入寄存器和 DAC 寄存器被清零為 0x000,輸出為零刻度。

3.6 LDAC 功能

DAC 輸出可以通過硬件 (LDAC) 引腳進行更新。(LDAC) 通常為高電平,下降沿時數據從輸入寄存器復制到 DAC 寄存器,DAC 輸出同時更新。如果 (LDAC) 保持低電平或在第 16 個 SCLK 下降沿為低電平,則相應的 DAC 寄存器和輸出會自動更新。

3.7 溫度傳感器

AD5504 集成了溫度傳感器,當芯片溫度超過 110°C 時,設備進入熱關斷模式,模擬部分掉電,DAC 輸出斷開,控制寄存器的 Bit 0 置為 1,(ALARM) 引腳變為低電平。只有當控制寄存器的 Bit 0 清零為 0 時,設備才會退出熱關斷模式。

3.8 功耗計算

功耗產生的熱量會導致芯片和封裝溫度升高,可通過公式 (T{J}=T{A}+(P{TOTAL} × theta{JA})) 計算封裝結溫,其中 (T{J}) 為封裝結溫,(T{A}) 為環境溫度,(P{TOTAL}) 為總功耗,(theta{JA}) 為熱阻。為保證正常運行,封裝結溫不應超過 130°C。

3.9 電源供電順序

AD5504 的電源可以按任意順序施加,但在施加電源之前,AGND 和 DGND 引腳應連接到相關接地平面。上電期間,數字輸入引腳(SCLK、SDI、SYNC、(R_{SEL}) 和 (CLR))不應浮空,可以根據需要連接上拉或下拉電阻。

四、串行接口

4.1 接口標準

AD5504 的串行接口((SYNC)、SCLK、SDI 和 SDO)兼容 SPI 接口標準以及大多數 DSP。輸入移位寄存器為 16 位寬,由一個讀寫控制位、三個地址位和 12 位 DAC 數據位組成,數據按 MSB 優先順序加載。

4.2 寫模式

寫寄存器時,(R / overline{W}) 位應設置為 0,三個地址位確定要更新的寄存器。數據在同一幀的剩余 12 個時鐘周期內時鐘輸入到所選寄存器。寫序列從 (SYNC) 線拉低開始,數據在 SCLK 上升沿時鐘輸入到 16 位移位寄存器,第 16 個下降時鐘沿完成數據輸入并執行編程功能。

4.3 讀模式

AD5504 允許通過串行接口從除 DAC 寄存器外的所有可直接訪問的寄存器進行數據讀回。讀回寄存器時,將 (R / overline{W}) 位設置為 1,三個地址位確定要讀回數據的寄存器,數據在同一幀的接下來 12 個時鐘周期內從 SDO 引腳時鐘輸出。由于 (t_{14})(110 ns)的時序要求,讀操作期間 SPI 接口的最大速度不應超過 9 MHz。

4.4 控制寄存器寫入

當 Bits[DB14:DB12] 為 1 時寫入控制寄存器,控制寄存器設置 DAC 輸出的上電狀態。寫入控制寄存器后必須跟隨另一個寫操作,第二個寫操作可以是寫入 DAC 輸入寄存器或無操作(NOP)寫。

五、接口示例

5.1 與 Blackfin DSP 接口

AD5504 的 SPI 接口可以方便地連接到 Analog Devices 的 Blackfin? DSP。Blackfin 具有集成的 SPI 端口,可以直接連接到 AD5504 的 SPI 引腳,可編程輸入/輸出引腳可用于讀取或設置與接口相關的數字輸入或輸出引腳的狀態。

5.2 與 ADSP - 21065L DSP 接口

Analog Devices 的 ADSP - 21065L 是一款浮點 DSP,具有兩個串行端口(SPORTs)。可以使用其中一個 SPORT 控制 AD5504,通過連接相關引腳實現數據的讀寫操作。

六、總結

AD5504 作為一款高性能的高電壓四通道 12 位電壓輸出 DAC,憑借其豐富的功能、靈活的輸出范圍和良好的電氣性能,在眾多應用領域具有廣闊的應用前景。在實際設計中,電子工程師需要根據具體的應用需求,合理選擇輸出范圍、配置控制寄存器,并注意電源供電順序和時序要求,以充分發揮 AD5504 的優勢。你在使用 AD5504 或類似 DAC 時遇到過哪些問題呢?歡迎在評論區分享你的經驗和見解。

-

dac

+關注

關注

44文章

2767瀏覽量

197463 -

數模轉換器

+關注

關注

14文章

1363瀏覽量

85907 -

ad5504

+關注

關注

0文章

3瀏覽量

1300

發布評論請先 登錄

深入解析AD5504:高電壓四通道12位電壓輸出DAC

深入解析AD5504:高電壓四通道12位電壓輸出DAC

評論