AD9171:高性能雙路16位6.2 GSPS RF DAC的技術剖析與應用指南

在高速無線通信和儀器儀表領域,高性能的RF DAC扮演著至關重要的角色。今天,我們就來深入探究一款熱門的產品——AD9171,一款高性能雙路16位6.2 GSPS RF DAC,了解它的特性、工作原理、性能指標以及實際應用中的要點。

文件下載:AD9171.pdf

1. AD9171簡介

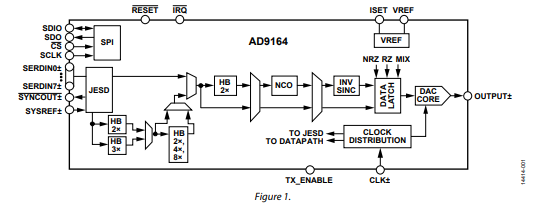

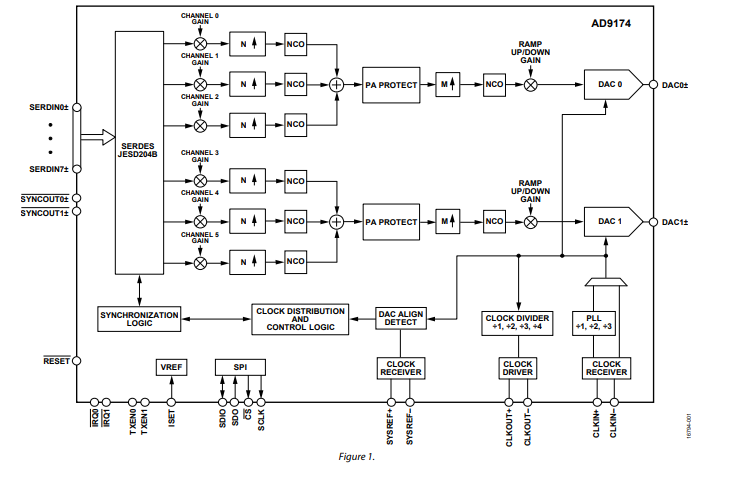

AD9171是一款專為單頻段無線應用打造的高性能雙路16位數字 - 模擬轉換器(DAC),支持高達6.2 GSPS的DAC采樣率。其擁有8通道、15.4 Gbps的JESD204B數據輸入端口,片上集成高性能DAC時鐘乘法器和針對單頻段直連射頻(RF)無線應用的數字信號處理能力。這使得它在無線通信基礎設施、單頻段基站無線電以及儀器儀表、自動測試設備(ATE)等領域都有廣泛的應用潛力。

2. 主要特性亮點

2.1 數據輸入與處理

- 單通道數據支持:每個RF DAC配備1個復數數據輸入通道,最高支持516 MSPS的復數輸入數據速率,且每個輸入通道都有獨立的NCO,為頻率規劃提供了極大的靈活性。

- 高速接口:采用靈活的8通道、15.4 Gbps JESD204B接口,支持單頻段應用場景,還支持12位高密度模式,有效提升數據吞吐量。

2.2 高性能設計

- 低雜散與失真:采用專有設計,能有效降低雜散和失真。在1.8 GHz、 - 7 dBFS/音RF輸出條件下,2音IMD可達 - 83 dBc,SFDR小于 - 80 dBc。

- 多芯片同步:支持多芯片同步,能夠實現多個DAC的同步操作,并為DAC建立恒定且確定的延遲路徑,確保數據的準確傳輸。

2.3 功耗與封裝優勢

- 低功耗:在6 GSPS單通道模式下功耗僅1.45 W,能有效降低系統的整體功耗。

- 緊湊封裝:采用10 mm × 10 mm、144球BGA_ED封裝,且帶有金屬增強散熱蓋,不僅尺寸緊湊,還能保證良好的散熱性能。

3. 工作原理詳解

3.1 數字數據路徑

AD9171的數字數據路徑由可旁路的通道數據路徑和通向模擬DAC核心的主DAC數據路徑組成。通道數據路徑包含可編程增益級、復數內插塊和48位復數NCO,可獨立配置增益和NCO參數。主DAC數據路徑包含功率放大器(PA)保護塊、復數主數據路徑內插塊、48位復數主數據路徑NCO和斜坡上升/下降增益塊,同樣可獨立配置相關參數。

3.2 JESD204B接口

該接口由物理層、數據鏈路層和傳輸層組成。物理層負責建立可靠的通道,數據鏈路層負責解包和擾碼數據,傳輸層將解擾后的JESD204B幀轉換為DAC樣本。通過多個JESD204B參數定義數據的打包方式,支持多種單鏈路和雙鏈路模式選擇,以適應不同的應用需求。

3.3 時鐘與同步

輸入數據的時鐘來源于DAC時鐘,可通過片上PLL生成或直接使用外部高保真DAC采樣時鐘。設備支持JESD204B Subclass 0和Subclass 1操作,Subclass 1模式可通過外部低抖動SYSREF±信號實現確定性延遲,確保多設備之間的同步。

4. 性能參數分析

4.1 DC參數

- 分辨率與精度:具有16位分辨率,積分非線性(INL)和差分非線性(DNL)均為 ± 7 LSB,保證了較高的轉換精度。

- 模擬輸出:模擬輸出的增益誤差在使用內部ISET參考時為 ± 15 %,滿量程輸出電流可通過RSET電阻進行調整,差分阻抗為100 Ω。

4.2 AC參數

- 無雜散動態范圍(SFDR):在不同頻率和輸出電平下,SFDR表現出色。例如,在單音、6000 MSPS、 - 7 dBFS且shuffle啟用的模式0下,fOUT為100 MHz時SFDR可達 - 85 dBc。

- 鄰道泄漏比(ACLR)和三階互調失真(IMD):在適當的測試條件下,ACLR和IMD都能滿足高性能應用的要求,確保信號的高質量輸出。

5. 實際應用考慮

5.1 電源供應

所有AD9171的電源域都應盡可能保持無噪聲,以確保最佳性能。建議在電源輸出端使用LC濾波器,并將其盡可能靠近AD9171放置。對于對噪聲敏感的AVDD1.0和AVDD1.8電源,推薦使用超低噪聲穩壓器,如ADP1763和ADM7154,以實現最佳的相位噪聲性能。

5.2 PCB布局

- JESD204B接口布線:在布局JESD204B串行接口傳輸線時,需考慮插入損耗、回波損耗、信號偏移和差分走線拓撲等因素。應盡量縮短差分走線長度,選擇低介電常數的PCB材料,合理處理過孔,以減少插入損耗和阻抗不匹配。

- 時鐘和控制信號:對于SYSREF±、SYNCOUTx±和CLK±等信號,應采用受控阻抗走線,并與潛在的噪聲源隔離,確保信號的穩定性和準確性。

5.3 啟動序列

AD9171上電后,需要按照特定的步驟對其進行編程,以使其進入正常工作狀態。啟動序列包括電源上電、DAC PLL配置、延遲鎖定環路(DLL)配置、校準、JESD204B模式設置等多個步驟,每個步驟都需要精確的寄存器寫入和適當的延時,以確保設備的穩定運行。

6. 總結

AD9171憑借其高采樣率、低雜散失真、靈活的接口配置和低功耗等優勢,在無線通信和儀器儀表等領域展現出了強大的競爭力。然而,在實際應用中,工程師需要充分考慮其電源供應、PCB布局和啟動序列等方面的要求,以確保設備能夠發揮出最佳性能。希望通過本文的介紹,能幫助電子工程師更好地了解和應用AD9171,在實際項目中取得理想的效果。大家在使用AD9171過程中遇到過哪些有趣的問題或者有獨特的應用經驗呢?歡迎在評論區分享交流!

-

無線通信

+關注

關注

58文章

5044瀏覽量

146990

發布評論請先 登錄

AD9171:高性能雙路16位6.2 GSPS RF DAC的技術剖析與應用指南

AD9171:高性能雙路16位6.2 GSPS RF DAC的技術剖析與應用指南

評論