56F8033/56F8023數字信號控制器深度解析

在電子工程領域,數字信號控制器(DSC)扮演著至關重要的角色,它結合了數字信號處理(DSP)的強大運算能力和微控制器(MCU)的控制功能。今天,我們就來深入探討飛思卡爾(Freescale)的56F8033/56F8023這兩款16位數字信號控制器。

文件下載:MC56F8033VLC.pdf

一、產品概述

1.1 核心特性

56F8033/56F8023基于56800E核心,具備高效的16位架構。在32MHz的核心頻率下,它能實現高達32 MIPS的處理速度,這意味著它可以快速處理復雜的數字信號和控制任務。其單周期16×16位并行乘法累加器(MAC)以及四個36位累加器,為數字信號處理提供了強大的運算支持。同時,它還擁有32位算術和邏輯多位移位器,以及獨特的DSP尋址模式和硬件DO與REP循環,這些特性使得它在處理復雜算法時表現出色。

1.2 設備差異

這兩款設備的主要差異體現在片上內存上。56F8033擁有64KB的程序閃存(PFLASH)和8KB的統一數據/程序隨機存取存儲器(RAM),而56F8023則配備32KB的PFLASH和4KB的RAM。這種差異使得用戶可以根據具體應用需求選擇合適的設備。

1.3 內存架構

采用雙哈佛架構,允許同時對程序和數據內存進行多達三次訪問,大大提高了數據處理效率。同時,它還具備閃存安全和保護機制,防止未經授權的用戶訪問內部閃存,保障了數據的安全性。

1.4 外設電路

- PWM模塊:擁有一個多功能六輸出脈沖寬度調制器(PWM)模塊,最高可支持96MHz的PWM工作時鐘,具備15位的分辨率,支持中心對齊和邊緣對齊的PWM信號模式,還配備四個可編程故障輸入和可編程數字濾波器,以及雙緩沖PWM寄存器,為電機控制等應用提供了強大的支持。

- ADC和DAC:兩個獨立的12位模數轉換器(ADC),支持同時和順序轉換,采樣率高達2.67MSPS,還有16字結果緩沖寄存器。同時,兩個內部12位數模轉換器(DAC),輸出擺幅從軌到軌的建立時間為2μs,還能自動生成方波、三角波和鋸齒波等波形。

- 定時器和通信接口:一個16位多功能四定時器模塊(TMR),最高工作時鐘可達96MHz,有八個獨立的16位計數器/定時器,具備捕獲和比較功能,多達12種工作模式。此外,還配備了一個具有LIN從機功能的排隊串行通信接口(QSCI)、一個排隊串行外設接口(QSPI)和一個I2C端口,滿足了不同的通信需求。

1.5 能源信息

采用高密度CMOS工藝制造,具有5V容限。片上調節器為數字和模擬電路供電,降低了成本并減少了噪聲。支持等待和停止模式,以及ADC智能電源管理,每個外設都可以單獨禁用以節省功耗。

二、時鐘合成模塊(OCCS)

2.1 概述

OCCS模塊允許用戶使用內部弛豫振蕩器、外部晶體或外部時鐘,以用戶可選擇的頻率運行56F8000系列設備,最高可達32MHz。

2.2 特性

- 具備內部弛豫振蕩器,可在外部頻率源或晶體不可用時提供參考頻率。

- 能夠對內部弛豫振蕩器或晶體振蕩器進行掉電操作,還能將內部弛豫振蕩器置于待機模式。

- 3位后置分頻器可控制PLL輸出。

- 可對PLL進行掉電操作。

- 為系統集成模塊(SIM)提供兩倍系統時鐘,為PWM和定時器模塊提供三倍系統時鐘。

- 若PLL參考時鐘丟失,具備安全關機功能。

- 可由外部時鐘源驅動。

2.3 工作模式

在56F8000系列設備中,可使用內部振蕩器、外部晶體或外部時鐘源為SIM提供參考時鐘。2X系統時鐘源輸出可由特定方程描述,SIM負責進一步將這些頻率除以2,以確保系統時鐘輸出具有50%的占空比。

2.4 內部時鐘源

內部弛豫振蕩器在不使用外部頻率源或晶體時可提供參考頻率,具有良好的溫度和電壓穩定性,還支持待機和掉電狀態以優化功耗。其中心頻率在工廠校準為8MHz,可通過微調內部電容將精度調整到8MHz的±0.078%以內。

2.5 晶體振蕩器和陶瓷諧振器

內部晶體振蕩器電路可與4 - 8MHz的并聯諧振晶體諧振器或陶瓷諧振器接口。在選擇晶體或諧振器時,應遵循供應商的建議,以確保最大穩定性和可靠啟動。

2.6 外部時鐘輸入

可通過將外部時鐘源連接到XTAL引腳,將EXTAL引腳接地,或選擇GPIO6/RXD或GPIOB5/TA1/FAULT3/XTAL/EXTAL作為外部時鐘輸入。

三、內存映射

3.1 程序地址空間

包括中斷向量表,不同設備的程序閃存和RAM分配有所不同。56F8033的程序閃存為64KB,RAM為8KB;56F8023的程序閃存為32KB,RAM為4KB。

3.2 數據地址空間

包括EOnCE內存和外設內存映射。不同設備的數據內存分配也存在差異,同時還列出了EOnCE內存映射和外設內存映射寄存器的詳細信息。

四、中斷控制器(ITCN)

4.1 功能

ITCN模塊負責仲裁各種中斷請求(IRQ),當存在足夠優先級的中斷時向56800E核心發出信號,并確定處理該中斷的跳轉地址。

4.2 特性

- 每個IRQ具有可編程的優先級級別。

- 具備兩個可編程的快速中斷。

- 可通知SIM模塊在等待和停止模式下重啟時鐘。

- 能夠在復位后驅動地址總線上的初始地址。

4.3 操作模式

- 正常中斷處理:確定要處理的中斷和最高優先級中斷后,生成中斷向量地址。

- 中斷嵌套:允許更高優先級的IRQ中斷當前異常。

- 快速中斷處理:中斷控制器在核心之前識別快速中斷,通過特定配置實現快速中斷處理。

4.4 寄存器描述

詳細介紹了ITCN的各個寄存器,包括中斷優先級寄存器、向量基地址寄存器、快速中斷匹配寄存器等,每個寄存器都有其特定的功能和位定義。

五、系統集成模塊(SIM)

5.1 功能

SIM模塊是片上系統的核心控制模塊,負責芯片復位排序、核心和外設時鐘控制與分配、停止/等待模式控制、系統狀態控制等功能。

5.2 特性

- 提供芯片復位排序功能。

- 控制核心和外設時鐘的分配。

- 支持停止、等待和運行三種電源模式,可控制電源利用率。

- 具備寫保護功能,可控制56800E核心的WAIT和STOP指令的啟用/禁用,以及大調節器待機模式的啟用/禁用。

- 允許選定的外設在停止模式下運行以生成停止恢復中斷。

- 控制可編程外設和GPIO的連接。

- 支持軟件芯片復位。

- 控制I/O短地址基位置。

- 提供外設保護控制,為安全關鍵應用提供防失控代碼保護。

- 控制內部時鐘源輸出到CLKO引腳。

- 四個通用軟件控制寄存器僅在上電時復位。

- 控制外設停止模式的時鐘。

5.3 寄存器描述

詳細介紹了SIM的各個寄存器,包括控制寄存器、復位狀態寄存器、軟件控制寄存器、功率控制寄存器等,每個寄存器都有其特定的功能和位定義。

5.4 時鐘生成概述

SIM使用來自OCCS模塊的主時鐘(2X系統時鐘),最高可達64MHz,為外設、核心和內存提供最高32MHz的系統時鐘。還可提供3X系統高速外設時鐘,最高可達96MHz,為PWM、定時器A和I2C模塊提供可選時鐘。

5.5 電源節省模式

設備可在運行、等待、停止、待機和掉電五種電源節省模式下運行,每種模式都有其特定的時鐘操作和恢復條件,用戶可根據實際需求選擇合適的模式以優化功耗。

5.6 復位和時鐘

SIM支持五種復位源,包括外部復位、上電復位、軟件復位、COP超時復位和COP參考丟失復位。復位生成模塊有三個復位檢測器,可產生四個主要復位信號。時鐘方面,內存、外設和核心時鐘通常以相同頻率運行,SIM負責時鐘分配。

六、安全特性

56F8023提供了安全特性,旨在防止未經授權的用戶讀取閃存內存(FM)陣列的內容。通過編程特定的安全字到程序內存位置,可啟用閃存安全模式,此時核心EOnCE調試功能將被禁用,但正常程序執行不受影響。同時,還提供了多種解鎖閃存的方法,如使用JTAG、CodeWarrior或編程特定的字到內存位置等。

七、通用輸入/輸出(GPIO)

7.1 配置

設備定義了四個GPIO端口,每個端口具有不同的寬度、關聯外設和復位功能。具體的GPIO端口引腳映射和功能選擇可通過SIM寄存器進行配置。

7.2 復位值

詳細列出了各個GPIO端口的寄存器映射和復位值,為工程師在設計和調試過程中提供了重要參考。

八、規格參數

8.1 一般特性

采用高密度CMOS工藝制造,具有5V容限的TTL兼容數字輸入。給出了絕對最大額定值和推薦工作條件,包括電源電壓范圍、時鐘頻率、輸入輸出電壓等參數。

8.2 電氣特性

包括DC電氣特性和AC電氣特性,如輸出電壓、輸入電流、電容等參數,以及各種外設的時序參數,如SPI、SCI、I2C等接口的時序要求。

8.3 功耗

詳細介紹了不同電源模式下的電流消耗,以及功耗的計算方法,為工程師在設計低功耗系統時提供了參考。

九、封裝和設計考慮

9.1 封裝信息

設備采用32引腳的低輪廓四方扁平封裝(LQFP),給出了封裝外形、機械參數和引腳排列信息。

9.2 設計考慮

- 熱設計:介紹了芯片結溫的估算方法,以及在使用和不使用散熱器時的熱阻計算方法,為熱設計提供了指導。

- 電氣設計:給出了一系列電氣設計考慮事項,如提供低阻抗電源路徑、旁路電容配置、減少PCB走線長度、分離模擬和數字電路等,以確保設備的正常運行。

十、訂購信息

提供了兩款設備的訂購信息,包括溫度范圍、電源電壓、封裝類型、引腳數量、頻率等參數,方便用戶進行訂購。

十一、附錄

給出了寄存器縮寫的交叉參考表,方便工程師在不同文檔中查找和使用寄存器信息。

56F8033/56F8023數字信號控制器憑借其強大的處理能力、豐富的外設資源和靈活的配置選項,適用于工業控制、運動控制、家電、通用逆變器、智能傳感器、消防和安全系統、開關模式電源、電源管理和醫療監測等眾多應用領域。工程師在設計過程中,應根據具體應用需求,合理選擇設備和配置參數,同時注意熱設計和電氣設計等方面的考慮,以確保系統的穩定性和可靠性。你在使用這兩款設備的過程中遇到過哪些問題呢?歡迎在評論區分享你的經驗和見解。

-

數字信號控制器

+關注

關注

0文章

107瀏覽量

13855

發布評論請先 登錄

Freescale MC56F827xx系列數字信號控制器深度解析

56F8347/56F8147:16位數字信號控制器的深度剖析

56F8036數字信號控制器:高效集成與卓越性能的完美融合

56F826數字信號控制器:特性、應用與設計要點

深入解析Microchip dsPIC30F4011/4012數字信號控制器

探索Microchip dsPIC30F3010/3011:高性能16位數字信號控制器

dsPIC30F6011/6012/6013/6014數字信號控制器:功能與特性解析

dsPIC30F6010:高性能16位數字信號控制器的技術剖析

dsPIC30F系列數字信號控制器編程規范詳解

SPC56ELx/SPC564Lx系列32位微控制器深度解析

探索 NXP MC56F80xxx 數字信號控制器:特性、應用與設計要點

NXP MC56F80000-EVK評估板:功能與應用深度解析

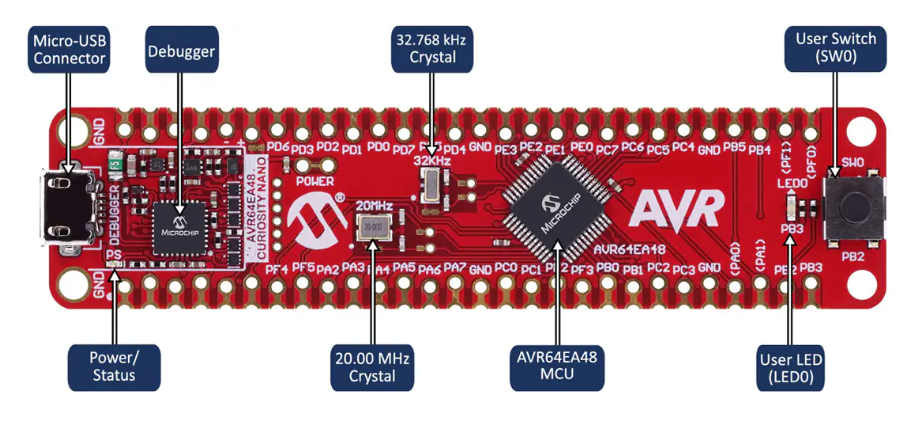

PIC18F56Q71 Curiosity Nano評估套件技術解析與應用指南

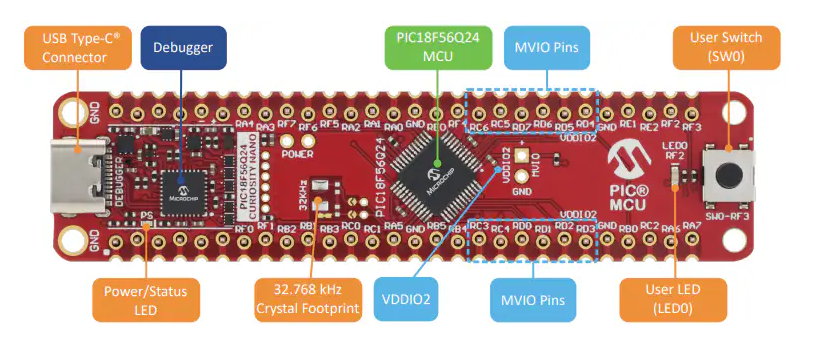

PIC18F56Q24 Curiosity Nano開發板技術解析與應用指南

56F8033/56F8023數字信號控制器深度解析

56F8033/56F8023數字信號控制器深度解析

評論