AD9445:高性能14位IF采樣ADC的技術剖析與應用指南

引言

在電子設計領域,模數轉換器(ADC)作為模擬信號與數字信號之間的橋梁,其性能直接影響著整個系統的表現。AD9445作為一款14位、具有105/125 MSPS采樣率的IF采樣ADC,以其卓越的性能和豐富的特性,在眾多應用場景中展現出強大的優勢。本文將深入剖析AD9445的技術特點、性能參數、工作原理以及應用注意事項,為電子工程師在設計過程中提供全面的參考。

文件下載:AD9445.pdf

產品概述

AD9445是一款單芯片采樣ADC,內置IF采樣跟蹤保持電路,專為高性能、小尺寸和易用性而優化。它的轉換速率最高可達125 MSPS,適用于多載波、多模式接收器,如蜂窩基礎設施設備中的相關應用。該產品需要3.3 V和5.0 V電源以及低壓差分輸入時鐘,在許多應用中無需外部參考或驅動組件。數據輸出兼容CMOS或LVDS(ANSI - 644兼容),并提供了降低短跡線距離所需總電流的方法。

產品特性

高性能指標

- 信噪比(SNR)和無雜散動態范圍(SFDR):在不同輸入頻率和幅度下,AD9445展現出出色的SNR和SFDR性能。例如,在30 MHz輸入(3.2 V p - p)時,SNR可達78.3 dBFS,SFDR可達92 dBFS;在170 MHz輸入(3.2 V p - p)時,SNR為77.0 dBFS,SFDR為87 dBFS。這些指標確保了在不同信號頻率下都能實現高質量的信號轉換。

- 低抖動:具有60 fsec rms的抖動,有效減少了采樣誤差,提高了信號處理的準確性。

- 出色的線性度:典型的DNL為±0.25 LSB,INL為±0.8 LSB,保證了信號轉換的線性度,減少了量化誤差。

靈活的輸入輸出特性

- 輸入范圍:支持2.0 V p - p至4.0 V p - p的差分滿量程輸入,可根據實際應用需求進行調整。

- 輸出模式:提供LVDS輸出(ANSI - 644兼容)或CMOS輸出,用戶可通過OUTPUT MODE引腳進行選擇。同時,數據格式可選擇偏移二進制或二進制補碼,滿足不同系統的接口要求。

- 輸出時鐘:提供輸出時鐘,方便與其他數字電路進行同步。

其他特性

- 時鐘占空比穩定器(DCS):可在寬范圍的時鐘脈沖寬度內保持ADC的整體性能,減少時鐘占空比變化對性能的影響。

- 超范圍輸出(OR):當信號超出所選輸入范圍時,OR輸出可提供指示,便于系統進行異常處理。

- RF使能引腳:用戶可通過該引腳配置設備,在采樣頻率高于210 MHz(AD9445 - 125)或240 MHz(AD9445 - 105)時優化SFDR性能。

性能參數

DC參數

- 分辨率:14位,確保了較高的量化精度。

- 精度:保證無丟失碼,偏移誤差和增益誤差在規定范圍內,如偏移誤差在25°C時為 - 7 ± 3 + 7 mV,增益誤差在25°C時為 - 2 + 2 % FSR。

- 電壓參考:輸出電壓VREF = 1.0 V,負載調節在1.0 mA時為±2 mV。

- 輸入噪聲:在25°C時為1.0 LSB rms。

- 電源:AVDD1為3.3 V(±5%),AVDD2為5.0 V(±5%),DRVDD在LVDS輸出時為3.0 - 3.6 V,在CMOS輸出時為3.0 - 3.3 V。

AC參數

- SNR和SINAD:在不同輸入頻率下,SNR和SINAD表現良好。例如,在10 MHz輸入時,SNR可達74.3 dB,SINAD可達74.2 dB。

- 有效位數(ENOB):在不同輸入頻率下,ENOB可通過SINAD計算得出,反映了ADC的實際有效精度。

- SFDR:在不同輸入頻率下,SFDR表現出色,如在30 MHz輸入時,SFDR可達92 dBc。

數字參數

開關參數

- 時鐘輸入:最大轉換速率為105/125 MSPS,最小轉換速率為10 MSPS,時鐘周期和脈沖寬度有明確要求。

- 數據輸出:輸出傳播延遲和流水線延遲等參數確保了數據輸出的及時性和準確性。

工作原理

架構設計

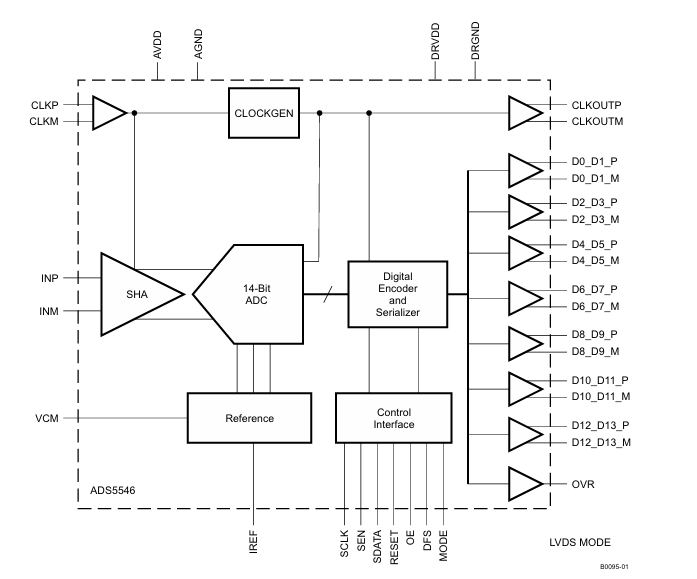

AD9445的架構針對高速和易用性進行了優化。模擬輸入驅動集成的高帶寬跟蹤保持電路,在信號被14位流水線ADC核心量化之前進行采樣。設備內置參考和輸入邏輯,可接受TTL、CMOS或LVPECL電平。數字輸出邏輯電平可通過OUTPUT MODE引腳選擇為標準3 V CMOS或LVDS(ANSI - 644兼容)。

模擬輸入和參考

- 參考配置:AD9445內置穩定準確的0.5 V帶隙電壓參考,輸入范圍可通過改變參考電壓進行調整。可選擇內部參考或外部參考,不同參考配置下,REFT和REFB驅動模數轉換核心并確定其輸入范圍。

- 模擬輸入:模擬輸入為差分輸入,可提高芯片性能,減少共模信號干擾。輸入電壓范圍偏移3.5 V,建議使用RF變壓器將單端信號轉換為差分信號,并通過串聯電阻進行阻抗匹配。

時鐘輸入

- 時鐘質量要求:高速ADC對采樣時鐘質量極為敏感,AD9445輸入采樣時鐘信號必須是高質量、極低相位噪聲的源,以防止性能下降。

- 時鐘占空比穩定器(DCS):DCS可在30% - 70%的占空比范圍內保持噪聲和失真性能幾乎不變,通過鎖定CLK +的上升沿優化內部時序。但在時鐘速率動態變化時,需考慮DCS的鎖定時間。

電源考慮

- 電源選擇:建議使用線性直流電源,每個電源引腳應盡可能靠近封裝使用0.1 μF芯片電容進行去耦。

- 電源分離:AD9445具有獨立的數字和模擬電源引腳,將AVDD1和DRVDD分開可避免數字輸出的快速擺動將開關電流耦合回模擬電源,提高性能。

數字輸出

- LVDS模式:通過OUTPUT MODE引腳配置為LVDS模式,可提供LVDS兼容的輸出電平,動態性能更佳。輸出包括互補的LVDS輸出、超范圍輸出和輸出數據時鐘輸出。

- CMOS模式:適用于對動態性能要求稍低的應用,輸出數據位為單端CMOS,輸出時鐘為差分CMOS信號。

應用領域

通信領域

雷達和成像領域

儀器儀表領域

- 通信儀器:用于通信儀器的信號測量和分析,確保測量結果的準確性和可靠性。

評估板

評估板可將AD9445配置為CMOS或LVDS模式,提供了所有支持電路,方便用戶在不同采樣率和模擬輸入頻率下測試和評估ADC的性能。評估板配備低相位噪聲的信號源和適當的濾波電路,以實現ADC的最佳性能。同時,還提供了軟件支持,方便用戶進行數據采集和分析。

注意事項

ESD防護

AD9445是靜電放電(ESD)敏感設備,盡管具有專有ESD保護電路,但仍需采取適當的ESD預防措施,避免因靜電放電導致性能下降或功能喪失。

時鐘源選擇

時鐘源的質量對ADC性能影響很大,應選擇低抖動的時鐘源,并可考慮對時鐘參考進行帶通濾波,以減少時鐘噪聲對ADC性能的影響。

電源設計

電源的穩定性和去耦對ADC性能至關重要,應選擇合適的電源,并確保電源引腳的去耦電容靠近封裝,以減少電源噪聲的影響。

總結

AD9445作為一款高性能的14位IF采樣ADC,憑借其出色的性能指標、靈活的輸入輸出特性和豐富的功能,在通信、雷達、成像和儀器儀表等多個領域具有廣泛的應用前景。電子工程師在設計過程中,應充分了解其技術特點和性能參數,合理選擇工作模式和配置參數,同時注意ESD防護、時鐘源選擇和電源設計等方面的問題,以確保系統的穩定運行和高性能表現。你在實際應用中是否遇到過類似ADC的設計挑戰呢?歡迎在評論區分享你的經驗和見解。

-

adc

+關注

關注

100文章

7796瀏覽量

556639 -

技術應用

+關注

關注

0文章

25瀏覽量

6527 -

ad9445

+關注

關注

0文章

4瀏覽量

1282

發布評論請先 登錄

AD9445:高性能14位IF采樣ADC的技術剖析與應用指南

AD9445:高性能14位IF采樣ADC的技術剖析與應用指南

評論