RZ/V2N Group芯片:功能、特性與設計考量

在當今的電子設計領域,芯片的性能和功能對于產品的成功至關重要。RZ/V2N Group芯片以其豐富的功能和出色的性能,成為眾多工程師關注的焦點。本文將詳細介紹RZ/V2N Group芯片的特性、引腳、電氣特性等方面,為電子工程師在設計過程中提供全面的參考。

文件下載:r01ds0466ej0120-rzv2n.pdf

一、概述

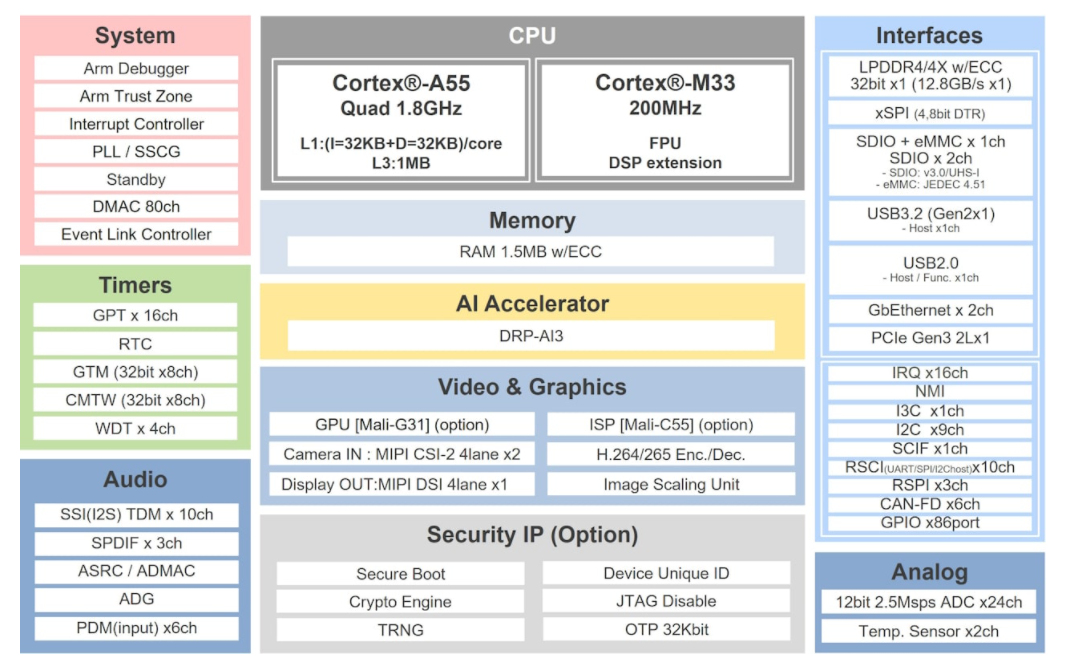

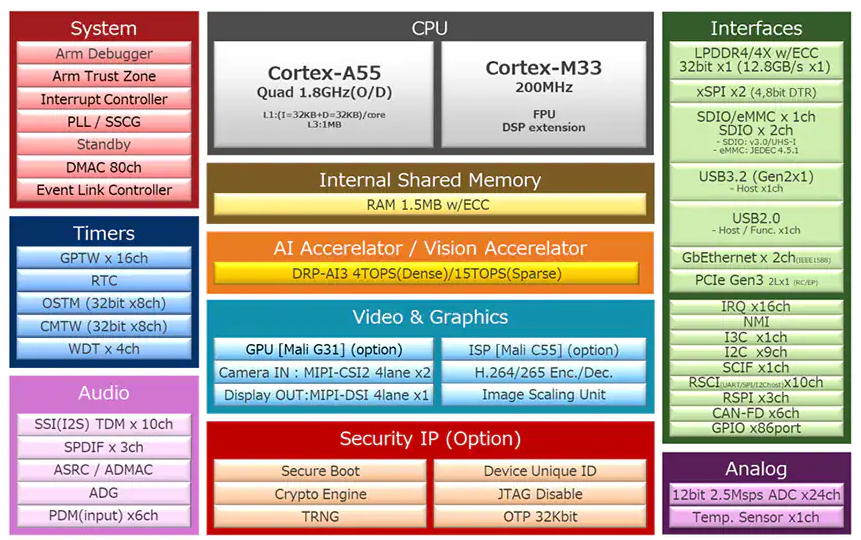

RZ/V2N Group芯片集成了多種強大的功能,包括高性能的CPU、豐富的加速器引擎、多種通信和存儲接口等。

(一)產品特性

- CPU:具備1.8 GHz Quad Arm? Cortex? - A55和200MHz Arm? Cortex? - M33處理器。其中,Cortex - A55用于應用處理,最高可達1.8 GHz;Cortex - M33用于系統管理,最高可達200 MHz。這種組合使得芯片能夠在高性能計算和系統管理方面實現高效協作。

- 加速器引擎:包含AI加速器(DRP - AI)、3D圖形引擎(GE3D)、圖像信號處理器(ISP)、圖像縮放單元(ISU)和視頻編解碼器單元(VCD)等。例如,DRP - AI最高可達4 dense TOPS和15 sparse TOPS,為AI計算提供強大的支持。

- 內存接口:擁有1.5 MB的片上SRAM和外部DDR內存接口,支持LPDDR4 - 3200或LPDDR4X - 3200,總線寬度為32位,為數據存儲和處理提供了充足的空間和高效的傳輸速度。

- 通信接口:集成了2ch GbEthernet MAC、1ch USB2.0、USB3.2 Gen 2x1、2 - MIPI? CSI - 2相機輸入接口、1 - MIPI? DSI?視頻輸出接口、PCIE? Gen3 2Lane(EP/RC)等多種接口,滿足了不同應用場景下的通信需求。

(二)產品陣容

RZ/V2N Group提供了多種型號的產品,不同型號在3D圖形引擎(GE3D)和安全功能等方面有所差異,工程師可以根據具體的應用需求進行選擇。

二、引腳說明

(一)引腳分配

芯片采用840 - pin FCBGA封裝,引腳分配詳細且復雜。通過詳細的引腳圖和表格,我們可以清晰地了解每個引腳的功能和用途。例如,DDR相關引腳用于與外部DDR內存進行數據交互,而時鐘引腳則為芯片提供穩定的時鐘信號。

(二)外部引腳

外部引腳具有多種功能,包括時鐘輸入、啟動模式控制、系統控制、中斷輸入、電源控制等。每個引腳都有特定的電壓要求、輸入輸出類型和初始值。例如,BOOTSELCPU引腳用于選擇冷啟動CPU,低電平選擇CM33,高電平選擇CA55。

(三)復用功能引腳

許多引腳具有復用功能,可以根據不同的應用場景選擇不同的功能。例如,P00引腳既可以作為GPIO/TINT_GP00使用,也可以用于PDMDAT00或GTETRGA等功能。

三、電氣特性

(一)絕對最大額定值

為了確保芯片的安全運行,需要嚴格遵守絕對最大額定值。不同的電源引腳有不同的電壓范圍,如CA55的VDD09_CA55電壓范圍為 - 0.4 V至1.2 V。超出這些范圍可能會導致芯片永久損壞。

(二)推薦工作范圍

在推薦工作范圍內使用芯片,可以保證芯片的性能和穩定性。例如,CA55的VDD09_CA55在0.86 - 0.94 V(0.9 V時為OD模式,0.8 V時為ND模式)范圍內工作。

(三)電源開關序列

芯片的電源開關序列非常重要,不同的啟動模式(CM33啟動模式和CA55啟動模式)有不同的電源開啟和關閉順序。在設計電源電路時,需要嚴格按照這些順序進行操作,以確保芯片正常啟動和運行。

(四)DC特性

DC特性包括最大供電電流、標準I/O特性等。了解這些特性可以幫助工程師合理設計電源電路和I/O接口。例如,不同單元的最大供電電流不同,CA55的0.8 - V(或0.9 - V)電源供應電流最大為3031 mA。

(五)AC特性

AC特性涵蓋了時鐘時序、各種接口的訪問時序等。例如,時鐘輸入頻率和周期有嚴格的要求,QEXTAL時鐘輸入頻率為24 ± 50 ppm MHz,周期為41.67 ns。這些特性對于確保芯片在高速運行時的穩定性至關重要。

(六)模擬特性

模擬特性主要涉及ADC和溫度傳感器的特性。ADC具有12位分辨率,模擬輸入范圍為0至ADAVDD18,轉換時間為0.4 - 4.0 μs。溫度傳感器在 - 40°C至125°C范圍內的精度為±3.0 - ±5.0°C。

四、設計考量

(一)電源設計

根據芯片的電氣特性,合理設計電源電路。確保電源的穩定性和紋波符合要求,避免電源波動對芯片性能產生影響。同時,要注意不同電源引腳的電壓范圍和啟動順序。

(二)時鐘設計

時鐘信號的穩定性對于芯片的正常運行至關重要。選擇合適的晶體諧振器,并合理布局時鐘電路,減少時鐘信號的干擾和抖動。例如,在連接晶體諧振器時,要將其和相關電容盡量靠近引腳,確保接地良好。

(三)接口設計

根據具體的應用需求,合理選擇和設計通信接口。注意接口的電氣特性和時序要求,確保數據的準確傳輸。例如,在設計USB接口時,要遵循USB 2.0或USB 3.2的標準規范。

(四)ESD防護

由于芯片對靜電放電(ESD)比較敏感,需要采取有效的ESD防護措施。例如,使用防靜電容器存儲和運輸芯片,操作人員佩戴防靜電手腕帶等。

五、總結

RZ/V2N Group芯片以其豐富的功能和出色的性能,為電子工程師提供了強大的設計平臺。在設計過程中,工程師需要深入了解芯片的特性和要求,合理設計電源、時鐘、接口等電路,同時注意ESD防護等問題。只有這樣,才能充分發揮芯片的優勢,設計出高性能、穩定可靠的電子產品。

作為電子工程師,我們需要不斷學習和掌握新的芯片技術,結合實際應用需求,進行創新設計。在使用RZ/V2N Group芯片時,你是否遇到過一些特殊的設計挑戰呢?歡迎在評論區分享你的經驗和見解。

發布評論請先 登錄

15TOPS、雙攝像頭、高能效 四核視覺AI MPU RZ/V2N數據手冊

瑞薩新款RZ/V2N視覺AI MPU產品介紹

RZ/V2N中檔嵌入式AI MPU 數據手冊和產品介紹

Banana Pi 最新邊緣 AI 系統模塊 BPI-AI2N 采用瑞薩電子 RZ/V2N

RZ/V2N Group芯片:功能、特性與設計考量

RZ/V2N Group芯片:功能、特性與設計考量

評論