碳化硅 (SiC) 功率模塊門極驅動技術:精密電壓鉗位與 DESAT 短路保護的設計細節深度解析

1. 引言與碳化硅材料的底層物理約束及驅動挑戰

在現代電力電子系統向著極高頻、極高壓和超高功率密度演進的歷史進程中,碳化硅 (SiC) 寬禁帶半導體已無可爭議地成為取代傳統硅 (Si) 基絕緣柵雙極型晶體管 (IGBT) 和硅基 MOSFET 的核心功率器件。從材料物理學的底層機理來看,傳統硅材料的禁帶寬度僅為 1.12 eV,而碳化硅的禁帶寬度高達 3.26 eV 。這一基礎屬性的飛躍意味著需要近乎三倍的能量才能將電子從價帶激發至導帶,從而賦予了 SiC 材料極佳的絕緣特性與耐高壓能力 。碳化硅的臨界擊穿電場強度達到了硅的十倍,這使得在相同的額定擊穿電壓下,SiC MOSFET 的漂移區厚度可以大幅度縮減,進而實現了極低的特定導通電阻 (RDS(on)?) 并具備了無與倫比的高頻開關能力 。此外,碳化硅的熱導率是硅和氮化鎵 (GaN) 的三倍,這意味著在給定的功率耗散條件下,SiC 器件的溫升顯著降低,能夠適應極為苛刻的高溫運行環境 。

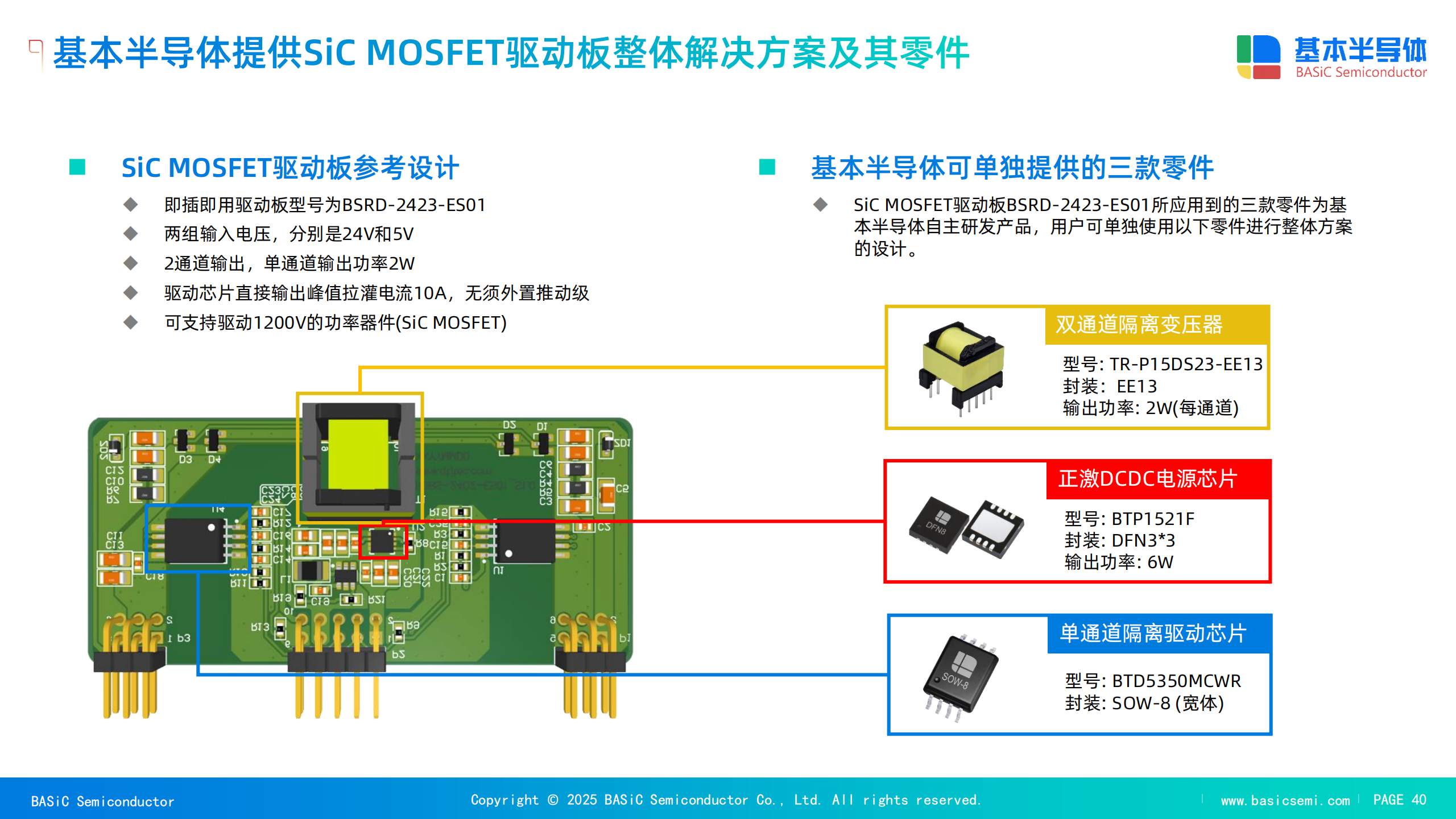

然而,這種材料層面的根本性優勢也為系統的外圍控制,尤其是門極驅動器 (Gate Driver) 的設計帶來了前所未有的嚴峻挑戰。相比于傳統的 Si IGBT,SiC MOSFET 具有跨導 (gm?) 較低、內部柵極電阻 (RG(int)?) 偏高、典型開啟閾值電壓 (VGS(th)?) 極低且具有顯著負溫度系數等特殊電氣屬性 。更為嚴峻的是,SiC MOSFET 憑借其極小的寄生電容和超快的電子遷移速度,在開關瞬態能夠產生極高的電壓變化率 (高達 50 V/ns 至 100 V/ns 的 dV/dt) 和電流變化率 (di/dt) 。這種極速的瞬態邊緣與器件自身的米勒電容相互耦合,極易在門極回路中激發出嚴重的電壓震蕩,進而引發致命的寄生導通 (Parasitic Turn-on) 現象 。傾佳電子力推BASiC基本半導體SiC碳化硅MOSFET單管,SiC碳化硅MOSFET功率模塊,SiC模塊驅動板,PEBB電力電子積木,Power Stack功率套件等全棧電力電子解決方案。?

基本半導體代理商傾佳電子楊茜致力于推動國產SiC碳化硅模塊在電力電子應用中全面取代進口IGBT模塊,助力電力電子行業自主可控和產業升級!

與此同時,由于 SiC MOSFET 利用其高臨界擊穿電場大幅縮小了裸晶 (Die) 的物理尺寸,在相同電流額定值下,SiC MOSFET 的芯片面積通常僅為同等規格 Si IGBT 的五分之一到十分之一 。芯片面積的急劇縮小直接導致了器件熱容量的驟降。在發生短路故障時,極高的短路電流密度會瞬間產生巨大的焦耳熱,使得 SiC MOSFET 的短路耐受時間 (Short Circuit Withstand Time, SCWT) 從傳統 IGBT 寬裕的 10 μs 銳減至 1 μs 到 3 μs 的極窄危險區間 。

基于上述復雜的物理與電氣雙重約束,SiC MOSFET 的門極驅動器設計早已超越了單純的電平轉換范疇。現代高性能門極驅動器不僅需要提供高度定制化的不對稱雙極性驅動電壓,以最小化導通損耗并確保關斷可靠性,還必須深度集成極具針對性的主動保護功能。本文將深入解構 SiC 功率模塊門極驅動設計中的核心技術體系,詳盡剖析有源米勒鉗位 (Active Miller Clamping)、基于非對稱 TVS 架構的精密電壓鉗位 (Precision Voltage Clamping) 以及去飽和 (DESAT) 短路保護的電路拓撲與參數計算演進模型。同時,本文將結合 BASiC Semiconductor 等商業化大功率 SiC 模塊的真實技術參數提取,為高頻大功率電力電子變換器(如新能源汽車牽引逆變器、光伏逆變器及儲能系統)提供詳實、嚴謹的驅動設計規范與前瞻性的工程理論洞察。

2. SiC MOSFET 門極驅動基礎與寄生參數效應的數學解析

2.1 不對稱門極驅動電壓的要求與動態功率計算模型

SiC MOSFET 屬于電壓控制型多數載流子半導體器件。為了充分釋放其低導通電阻的性能紅利,驅動回路必須在導通期間提供足夠高的正向柵源電壓。測試數據表明,當 VGS? 從常規的 10 V 或 15 V 提升至 18 V 或 20 V 時,器件的導通電阻 (RDS(on)?) 能夠獲得極為顯著的改善 。然而,過高的正向驅動電壓會逼近柵氧化層的絕對最大額定值(工業界通常設定在 +22 V 甚至 +25 V 的極限),進而引發長期的經時介質擊穿 (TDDB) 可靠性風險 。因此,工業界和各大半導體廠商廣泛推薦采用 +18 V 至 +20 V 作為最優的導通驅動電壓,以在極致導通效率與長期可靠性之間取得最佳平衡 。

在關斷狀態下,由于 SiC MOSFET 的閾值電壓 (VGS(th)?) 普遍偏低。在室溫下,典型閾值電壓通常在 1.9 V 至 4.0 V 之間,并且隨著結溫的升高,該閾值電壓會因其負溫度系數特性而進一步降低 。在高速開關過程中,由寄生電感和高 di/dt 產生的地彈噪聲以及由高 dV/dt 產生的耦合噪聲,極易越過這一本就微弱的閾值防線 。為確保器件在任何極端工況下都能完全且可靠地關斷,必須在關斷期間施加負偏置電壓。通常,-4 V 或 -5 V 的負偏置電壓被證明是抑制雜散導通并維持系統安全裕度的行業標準選擇 。

門極驅動器在系統運行期間需要為器件的輸入電容 (CISS?=CGS?+CGD?) 進行連續的高頻充放電,這要求驅動器輸出級具備提供足夠峰值電流和承受相應平均功率耗散的能力 。驅動功率 PG? 的理論數學模型可由開關頻率 fsw? 和總柵極電荷 QG? 精確描述:

PG?=QG?×fsw?×ΔVGS?

其中,ΔVGS?=VGS(on)??VGS(off)? 為雙極性驅動電壓的滿量程擺幅 。例如,在典型的 VGS?=+18V/?4V 配置下,電壓擺幅 ΔVGS?=22V 。對于大電流并聯模塊,由于其內部并聯了多個 SiC 晶粒,其總門極電荷 QG? 極大,驅動器必須具備充足的平均功率輸出能力。需要指出的是,如果驅動回路上串聯了外部柵極電阻 RG(ext)?,則充放電過程中產生的這部分熱損耗將由驅動器內部的推挽開關管(或緩沖晶體管)與外部電阻按阻值比例共同分擔 。無論阻值大小如何,等效的開啟電阻和關斷電阻總計將消耗掉一半的柵極驅動總功率 。

2.2 寄生電容模型、非平坦米勒平臺與高 dV/dt 誘發機制

在分析 SiC MOSFET 的開關瞬態時,其柵極電荷特性曲線 (VGS? vs. QG?) 表現出與傳統 Si MOSFET 截然不同的“非平坦米勒平臺” (Non-flat Miller Plateau) 現象 。這一獨特現象的物理根源在于 SiC 材料相對較低的跨導 (gm?) 。在理想的硅器件中,米勒平臺期間漏極電壓急劇下降,而柵極電壓保持在一個恒定的平坦值;但在 SiC MOSFET 中,非平坦的米勒平臺意味著在米勒電容 (CGD?) 充放電的關鍵區間內,柵極電壓并非維持絕對恒定,而是隨著注入電荷的變化呈現出顯著的斜率波動 。這種低跨導特性不僅導致總柵極電荷 QG?=0nC 的基準點并不出現在 VGS?=0V 處,更進一步印證了為了徹底清空輸入電容 CISS?,必須將柵極電壓拉至地電位以下(即負偏壓)的絕對必要性 。

在半橋拓撲中發生關斷瞬態時,對側開關管的導通會導致當前處于關斷狀態的 SiC MOSFET 漏源電壓 VDS? 發出極速的上升沿跳變(即產生極高的 dV/dt)。這種劇烈的電壓跳變會通過器件內部的反向傳輸電容(CGD?,即米勒電容)向柵極節點注入強烈的位移電流 。該米勒電流的解析式為:

IMiller?=CGD?×dtdVDS??

由于 SiC MOSFET 的開關速度極快,系統中的 dV/dt 輕易可攀升至 50 V/ns 甚至 100 V/ns 以上 。由此產生的巨大瞬態電流 IMiller? 被迫流經器件的內部柵極電阻 RG(int)? 以及驅動回路的外部下拉電阻 RG(off)?,從而在柵極和源極之間不可避免地產生一個正向的電壓尖峰:

ΔVGS?=IMiller?×(RG(int)?+RG(off)?)

如果這一由米勒效應誘發的電壓尖峰 ΔVGS? 超過了器件在特定溫度下的實際閾值電壓 VGS(th)?,原本處于關斷狀態的下管晶體管將發生非預期的瞬態導通 。這種現象被稱為寄生導通或米勒導通。寄生導通會導致半橋上下兩管瞬間直通 (Shoot-through),引發災難性的短路電流,不僅大幅增加開關損耗和熱耗散,嚴重時將直接擊穿器件,徹底摧毀整個電力電子變換系統 。

3. 徹底抑制寄生導通:有源米勒鉗位 (AMC) 與精密電壓鉗位技術的深度融合

為了從根本上消除由高 dV/dt 引起的米勒寄生導通風險,現代門極驅動器必須在關斷期間為門極提供一條阻抗極低且響應極快的泄放路徑。當前工業界在應對這一挑戰時,主要依賴兩種并行且高度互補的先進鉗位技術:有源米勒鉗位 (Active Miller Clamping, AMC) 與基于非對稱 TVS 架構的精密瞬態電壓鉗位 (Precision Voltage Clamping)。

3.1 有源米勒鉗位 (AMC) 的拓撲設計與物理局限性

有源米勒鉗位電路的核心理念是在門極 (Gate) 和負驅動電源 (VEE? 或單電源供電下的 GND) 之間并聯一個專用的低阻抗旁路開關管 。當門極驅動器發出關斷指令,且內部檢測電路監測到柵源電壓 VGS? 已經降至一個預設的安全閾值(通常設定在 2 V 左右)以下時,AMC 開關管會被瞬間激活導通 。

一旦 AMC 機制介入,由外部高 dVDS?/dt 誘發的巨大米勒位移電流將被該鉗位開關直接分流并旁路至負電源,而不再流經主驅動路徑上的常規關斷下拉電阻 RG(off)? 。這一設計的革命性意義在于,它徹底解耦了開關損耗優化與寄生導通抑制之間的矛盾:設計人員在選擇外部關斷電阻 RG(off)? 時,可以完全基于降低關斷開關損耗 (Eoff?) 和抑制關斷電壓過沖的單一維度進行考量,而不必為了防止米勒導通而被迫妥協去選擇極小的 RG(off)? 阻值 。此外,在某些對成本極度敏感的拓撲中,強大的 AMC 甚至允許系統在單極性電源(即僅有正壓和 0V,無負壓)下安全運行,省去了生成負電源所需的額外隔離繞組或電荷泵電路 。

內部與外部 AMC 架構的工程權衡: 內部 AMC (Internal Miller Clamp) 方案將鉗位比較器與旁路開關管完全集成在門極驅動 IC(例如 Infineon 1ED34x1Mc12M 或 TI UCC5870-Q1)內部 。這種高度集成的方案大幅減少了外部元器件數量,簡化了 PCB 走線路由,有助于實現高密度的緊湊型設計,且其觸發時序經過 IC 內部優化,與主驅動信號完美同步 。然而,受限于驅動 IC 自身的硅片面積、熱耗散預算以及封裝引腳的電流承載能力,內部 AMC 的鉗位電流峰值通常被限制在幾安培以內(如典型的 4A 有源米勒鉗位)。對于總門極電荷 QG? 動輒超過 1000 nC 的超大功率并聯 SiC 模塊(例如額定電流達 540 A 的 BMF540R12MZA3),內部 AMC 的泄放能力往往捉襟見肘 。此時,系統必須采用外部 AMC (External Clamp) 方案,利用驅動 IC 輸出的專用控制信號,去驅動外部大電流雙極結型晶體管 (BJT) 或高頻 MOSFET 陣列,從而構建出具備數十安培級瞬態泄放能力的強效外部米勒鉗位網絡 。

AMC 機制在高 dV/dt 場景下的物理局限性: 盡管 AMC 技術卓有成效,但深入的電磁兼容實驗與分析表明,當系統內的 dV/dt 極高(尤其是超過 20 V/ns 時),單純依賴 AMC 將面臨嚴峻的物理瓶頸 。這一瓶頸源于驅動 IC 的鉗位引腳到功率模塊柵極引腳之間的 PCB 走線不可避免地存在寄生電感 (LG(trace)?) 。依據法拉第電磁感應定律,高頻的米勒位移電流在流經這段寄生電感時,會產生陡峭的感性壓降 (VL?=L×dtdi?) 。這導致即便驅動 IC 端的電位已被完美鉗位至 0V 或負壓,但在模塊裸片實際的柵極節點上,仍會疊加出顯著的高頻電壓振蕩 。在此種極端瞬態下,AMC 的鉗位效率大幅衰減,已經無法作為確保柵氧絕對安全的唯一手段 。

3.2 精密電壓鉗位技術:從傳統齊納到非對稱 TVS 網絡的范式躍遷

為了彌補 AMC 在應對超高 dV/dt 及高寄生電感環境下的固有缺陷,必須在距離模塊柵源極 (G?S) 物理位置最近的節點處,引入更為直接的精密電壓鉗位電路,將其作為守衛柵氧的最后一道防線 。

在傳統的工程實踐中,設計人員通常通過將兩顆不同穩壓值的普通齊納二極管 (Zener Diode) 背靠背(反串聯)連接來進行雙向過壓保護。例如,在驅動回路中接入一顆 20 V 的齊納二極管用于強制鉗位正向電壓毛刺,并搭配接續一顆 6 V 的齊納二極管用于限制負向過壓 。這種設計可以在 AMC 受到走線寄生電感限制時,強制將正向振蕩壓制在模塊開啟閾值電壓 (Vth?) 之下,同時將負向震蕩限制在柵氧化層的絕對最大安全極值(例如 -10 V)以內,從而有效防止柵極絕緣層在高頻大電流震蕩中遭受不可逆的擊穿損傷 。

非對稱 TVS 鉗位技術的革命性突破: 然而,面對 SiC MOSFET 苛刻且高度不對稱的驅動電壓需求(典型的如 +18 V/-5 V 或 +20 V/-4 V),傳統齊納二極管網絡不僅體積龐大,更面臨著寄生電容過大、響應速度遲緩以及大浪涌下鉗位精度不足的嚴重瓶頸 。為此,業界推出了專為 SiC 門極保護定制的非對稱瞬態電壓抑制器 (Asymmetrical TVS Diodes),例如 Littelfuse 發布的 TPSMB Asymmetrical 系列,這代表了精密電壓鉗位技術的范式躍遷 。

此類非對稱 TVS 創造性地在單一緊湊型封裝(如 DO-214AA / SMB)內實現了針對正負雙向完全不同的瞬態電壓鉗位閾值 。以適配 +18 V/-5 V 邏輯的器件為例,當面對正向浪涌侵入時,其能夠將 VGS? 穩穩鉗位在 24.4 V 甚至更低的安全范圍之下,確保絕不觸碰 SiC MOSFET 典型的 +25 V 正向破壞極限;而在負向浪涌(如關斷時的振鈴)發生時,則能將反向電壓精準攔截并鉗位在 -10 V 以內 。

除了非對稱的電壓閾值,現代 TVS 技術在動態指標上同樣表現卓越。其峰值脈沖功率耗散能力高達 600 W (在 10/1000 μs 測試波形下),能夠從容吸收因極端 dV/dt 耦合進柵極回路的巨大能量 。更為關鍵的是,這些高級 TVS 二極管實現了極低的等效結電容,使得其在高達 2 MHz 的高頻開關環境下并聯于柵源兩端,也不會額外增加明顯的驅動功率損耗或拖慢開關上升/下降沿 。其理論響應時間遠小于 1.0 ns,確保了在那些極速攀升的納秒級電壓尖峰尚未對柵氧層造成物理沖擊之前,便已將其削平 。通過將這種具備車規級 AEC-Q101 認證的高性能非對稱 TVS 二極管就近并聯于 SiC 模塊引腳端,與驅動器內部的 AMC 機制形成遠近結合、高低搭配的雙重防御體系,可將大功率變換器的系統魯棒性提升至全新高度 。

4. 應對極端工況:SiC MOSFET 的短路耐受原理與 DESAT 保護深度設計

電力電子變換器(尤其是在電機驅動和逆變器應用中)的一項絕對核心安全要求是:在發生橋臂直通短路 (Shoot-through) 或負載端短路時,系統能夠迅速識別故障并安全地關斷功率器件,堅決避免發生熱失控、芯片燒毀甚至模塊爆炸等災難性后果。

4.1 SCWT 物理約束規律與 SiC 特定熱失效機制

短路耐受時間 (Short Circuit Withstand Time, SCWT) 是衡量功率器件在短路大電流應力下,能夠維持基本電氣隔離功能而不發生不可逆物理損壞的最長持續時間 。在短路事件(尤其是最嚴酷的第一類短路,即器件直接硬開關導通進入低阻抗短路網絡)發生時,漏極電流會瞬間飆升至器件額定電流的數十倍乃至數百倍;與此同時,由于短路回路特性,漏源電壓幾乎不會下降,而是維持在全直流母線電壓的極高水平 。這種“高電壓與極大電流共存”的疊加態,導致器件內部瞬間爆發出驚人的瞬態峰值耗散功率 。

正如前文在材料物理部分的分析,相比于具有相似電壓和電流額定值的 Si IGBT,SiC MOSFET 在短路耐受方面具有先天的結構性劣勢。SiC MOSFET 的極小晶粒面積意味著其在短路時承受的電流密度是傳統 IGBT 的 5 到 10 倍 。同時,微小的體積也導致其整體熱容量 (Thermal Capacitance) 大幅縮水 。

短路期間器件所能承受的臨界失效能量 EC? 受到其結至外殼熱阻抗 (Zthjc?) 的嚴格制約,其宏觀估算公式可表示為:

EC?=Zthjc?Tj(max)??Tc??×tp?

其中 tp? 代表短路脈沖的持續時間 。在巨大的焦耳熱沖擊下,由于熱量根本無法在幾微秒內通過封裝材料傳導散逸,SiC 裸片的結溫 (Tj?) 極速飆升。當溫度突破材料極限時,往往引發層間金屬鋁的熔化重構,或是導致本就薄弱的柵極氧化層在高電場與高溫的雙重蹂躪下發生災難性擊穿失效 。

因此,盡管傳統工業級 1200 V Si IGBT 能夠輕松扛住 10 μs 的短路沖擊,但對于同樣額定規格的 1200 V SiC MOSFET,其典型的短路耐受時間 (SCWT) 被殘酷地壓縮在了 1 μs 到 3 μs 這一極短的時間窗口內 。實驗數據進一步揭示了 SCWT 的動態依賴性:短路耐受時間隨著母線電壓 (VDS?) 的升高而銳減,因為更高的電壓意味著更快達到臨界失效能量 EC? 。同時,柵極驅動電壓 (VGS?) 同樣深刻影響著存活概率。以某 1.7 kV SiC MOSFET 的極限測試為例,當驅動電壓從 VGS?=15V 提高至 VGS?=20V 時,盡管器件導通性能更優,但其允許的峰值短路電流更大,導致實測的 SCWT 從 14 μs 直接衰減至 12 μs 。雖然如 NoMIS Power 等前沿廠商通過優化特定導通電阻 (Ron,sp?) 與短路魯棒性的折中平衡,成功將 SiC MOSFET 的 SCWT 延長至 5 μs 的行業新高度,但總體而言,留給系統執行檢測與保護的時間依然屬于微秒級的極速生死競速 。這要求門極驅動器的去飽和 (Desaturation, DESAT) 保護電路必須經過極致的參數尋優,實現超高速且無誤判的動作響應。

4.2 DESAT 保護拓撲分析與盲區時間 (Blanking Time) 的精密計算

目前,檢測短路故障最常見的方法分為分流電阻 (Shunt Resistor) 采樣法和去飽和 (DESAT) 檢測法。前者雖然原理直截了當且易于數字化,但在大功率系統(幾百安培級)中,串聯在功率回路中的分流電阻不僅引入了龐大的 I2R 傳導損耗和嚴重發熱問題,還會增加額外的母線寄生電感 。因此,通過利用器件自身導通時特有的伏安特性作為檢測依據的 DESAT 方法,憑借其極低損耗和易于集成的優勢,成為了中大功率 SiC 驅動保護的主流工業標準 。

一個標準的 DESAT 保護硬件回路由驅動 IC 內部的精密恒流源 (ICHG?,通常設定為 200 μA 至 500 μA 不等)、外部盲區電容 (CBLK?)、高壓隔離二極管 (DDESAT?) 以及限流電阻 (RDESAT?) 共同組成 。

運作機理: 在系統正常運行的導通狀態下,SiC MOSFET 處于線性工作區,漏源電壓 VDS? 迅速跌落至極低的導通壓降水平 (ID?×RDS(on)?) 。此時,DDESAT? 處于正向偏置導通狀態,內部恒流源 ICHG? 產生的電流通過二極管流入主電路,從而將 CBLK? 兩端的電壓強行鉗位在一個極低的水平。這一電平被設計為遠低于驅動內部故障比較器的觸發閾值電壓 (VDESAT(th)?,對于 SiC 驅動器,該閾值通常被專門設定在 6.0 V 至 7.5 V 之間,低于 IGBT 時代動輒 9 V 的標準) 。

一旦發生短路,流經 MOSFET 的電流呈指數級暴增,器件被迫退出線性區進入飽和區(或由于短路回路的特性導致壓降急劇攀升),巨大的 VDS? 使得高壓二極管 DDESAT? 瞬間反向偏置并截止 。此時,恒流源 ICHG? 無路可走,只能轉而向外部盲區電容 CBLK? 進行線性充電 。

盲區時間計算: 在這一過程中,CBLK? 的電壓從初始低電平攀升至故障閾值 VDESAT(th)? 所需的時間,被稱為“盲區時間” (Blanking Time, tblank?)。盲區時間是一把雙刃劍:它必須被設定得足夠長,以完全覆蓋正常開關導通時 VDS? 從千伏高壓跌落到毫伏低壓的整個動態振蕩瞬態,從而避免在開通瞬間由于電壓尚未完全下降而引發錯誤的短路觸發 (False Triggering) ;同時,它又必須被壓縮得足夠短,以確保整個保護鏈路的響應時間(等于 tblank? 加上 IC 內部比較器的傳輸延遲以及輸出級的關斷延遲)被嚴格限制在 SiC MOSFET 極為有限的 SCWT 容忍窗口之內 。

經典盲區時間的一階理論計算公式如下:

tblank?=ICHG?CBLK?×VDESAT(th)??

在部分復雜的工程實踐中,如果系統架構要求進一步縮短保護響應時間,但設計人員又不想改變驅動 IC 內部固化的 ICHG? 參數,可以通過在系統 VCC (正電源) 與 DESAT 引腳之間額外并聯一個外部上拉電阻 (RB?)。此舉將等效增加向電容充電的總電流,從而在線性縮短 tblank? 的同時賦予設計更高的自由度 。

4.3 核心外圍器件選型:高壓 DESAT 二極管的結電容隱患與電阻權衡

在實施 DESAT 保護網絡的設計時,最大的潛在隱患并非來自于比較器邏輯,而是來自于高壓阻斷二極管 (DDESAT?) 的非理想寄生參數,特別是其寄生結電容 (Cj?) 與系統開關節點極端 dV/dt 相互作用而產生的惡性耦合效應 。

當 SiC MOSFET 關斷或在半橋拓撲中對側開關管極速動作時,漏極節點上會產生高達 50 V/ns 到 100 V/ns 甚至更高的瞬態 dV/dt。此時,流經二極管結電容的位移電流 (Idisp?=Cj?×dtdVDS??) 將不受控制地通過限流電阻 RDESAT? 強行注入到 DESAT 引腳的盲區電容 CBLK? 中 。這在物理上構成了對盲區電容極其危險的瞬態異常充電行為。

通過定量推導可以發現,CBLK? 與二極管的結電容 Cj? 在高頻瞬態下實質上形成了一個高頻電容分壓器網絡。假定主母線開關節點上因為寄生振蕩產生了一個峰-峰值為 ΔVnoise? (例如 100 V) 的高頻噪聲,那么被耦合到高度敏感的 DESAT 引腳上的瞬態噪聲電壓 Vnoise? 可表示為:

Vnoise?=ΔVnoise?×CBLK?+Cj?Cj??

此時,若選用的二極管電容 Cj? 偏大(如 20 pF),且盲區電容設計得較小(如根據公式算得 CBLK?=200pF),那么耦合電壓 Vnoise?=100V×22020?≈9.1V。這一尖峰顯然已經大幅超出了驅動 IC 典型的 6.5 V 故障觸發閾值,必定導致嚴重的誤動作 。為了解決這一難題,如果將 CBLK? 增加到 470 pF,則噪聲被衰減為 4.1V,雖免于誤觸發,但帶來的代價是盲區時間 tblank? 陡增,極可能超出 SiC 器件的 SCWT 存活極限 。

為了徹底打破這一困局,工程選型與電路架構必須采取以下聯合策略:

苛求極低結電容器件: 在選擇 DDESAT? 時,必須將其反向阻斷能力(建議留有 2 倍以上母線電壓的裕量)與超低寄生電容視為最高優先級。通常要求選用結電容極小的超快恢復二極管或小電流的 1200 V/1700 V SiC 肖特基二極管 。

串聯降容法則: 在實際的高壓工業應用中,極少有單顆器件能在耐壓與容值上完美達標。因此,工業界廣泛采用多個低電容二極管串聯的架構。當 n 個結電容為 Cj? 的二極管串聯后,其總等效寄生電容將按比例大幅降為 nCj??。這在極大地提高阻斷電壓的同時,從根源上斬斷了交流噪聲的耦合路徑 。然而,串聯方案也會成倍增加穩態時的正向總壓降 (n×VF?),需在閾值設計中加以補償 。

限流電阻 RDESAT? 的雙刃劍效應: 串聯在回路中的阻尼電阻 RDESAT? 通常被推薦選取在 5 kΩ 到 10 kΩ 之間 。這一取值是一場精密的設計博弈。如果電阻選取過小(例如遠小于 5 kΩ),在面臨高 dV/dt 時,瞬間涌入 DESAT 引腳的瞬態位移電流可能高達數百毫安,足以擊穿驅動 IC 的內部邏輯檢測單元 。相反,如果電阻選取過大(超過 10 kΩ),RDESAT? 將與龐大的寄生電容共同形成顯著的低通濾波 RC 延遲效應。這種延遲甚至會達到上百納秒的數量級,嚴重拖慢系統對真正短路故障的響應速度,無謂地消耗掉 SiC 器件本就少得可憐的存活時間 。

除了電容充電機制,動態閾值的精確整定也必須將這些外圍壓降悉數納入考量,精確的短路觸發判據公式為:

VDESAT(trigger)?=(RDESAT?×ICHG?)+n×VF?+(ID?×RDS(on)?)

設計者必須通過微調 RDESAT? 或改變二極管串聯數量,使得最終設定的短路判定閾值能夠恰好略高于模塊在最大允許工作負載及最高結溫下所呈現的導通壓降峰值,從而實現既敏銳又穩健的完美保護 。此外,值得注意的是,二極管自身的反向恢復時間 (trr?) 也會介入并客觀上延長整體的保護盲區時間,這也是在嚴苛設計中不可忽視的動態參數 。

4.4 軟關斷 (Soft Turn-off) 與兩級關斷 (2LTO) 的系統級安全策略

當 DESAT 電路確鑿無誤地檢測到短路故障時,驅動系統絕對不能采取常規工作模式下那種以巨大負電流瞬間抽干門極電荷的“硬關斷” (Hard Turn-off) 操作。這是由于在短路狀態下,流過 MOSFET 的真實瞬態電流 ISC? 已經膨脹到額定負載電流的五倍乃至十倍之多 。此時若強行以極快的速度(即極高的 ?di/dt 下降率)阻斷電流,這些巨大的電流階躍會與系統逆變回路中的寄生電感(尤其是大體積直流母排與封裝內部積累的雜散電感 Lloop?)發生劇烈相互作用,在模塊漏源兩端激發出毀天滅地的反向過壓尖峰:

Vsurge?=Vbus?+Lloop?×dtdiSC??

這一因感性儲能釋放引發的災難性浪涌極易突破 1200 V 模塊自身的雪崩擊穿極限,從而導致原本為了保護器件而執行的關斷動作,反而成了壓死駱駝的最后一根稻草 。

為了化解這一自相矛盾的安全死局,高級 SiC 門極驅動器內部均標配了高度可編程的軟關斷 (Soft Turn-off, STO) 或更為精細的兩級關斷 (Two-Level Turn-Off, 2LTO) 硬件機制 。一旦確認為短路故障,驅動 IC 內部邏輯將迅速屏蔽常規的大功率下拉開關,轉而接通一條并聯的高阻抗、低電流放電路徑 。這種受控的低電流泄放人為延長了門極電壓衰減的時間常數,從而迫使 MOSFET 漏極短路電流呈現出平緩的下降斜率(有效壓制 di/dt)。通過這種主動控制手段,可以將災難性的過電壓浪涌尖峰安全地限制在器件的反向偏置安全工作區 (RBSOA) 輪廓之內,最終實現短路能量的安全卸載 。

5. 先進門極驅動芯片架構及 PCB 寄生電感優化原理

面對 SiC 功率器件嚴苛的動態保護與隔離需求,各大半導體巨頭紛紛推出了深度定制化的集成式門極驅動 IC(如 TI UCC217xx、UCC5870-Q1、UCC57102-Q1;Infineon 1ED34x1Mc12M;onsemi NCP51705;Skyworks Si828x 以及 Cissoid CMT 系列等)。這些先進驅動器不僅將共模瞬態抗擾度 (CMTI) 推高至 100 kV/μs 以上以抵御極端的 dV/dt 干擾,還全面集成了內部 AMC 比較器、高速 DESAT 盲區時間可編程控制邏輯以及關鍵的軟關斷功能,代表了當今驅動架構的技術巔峰 。

然而,在高速開關應用中,即便是性能最完美的驅動芯片,若缺乏經過精心優化的底層硬件 PCB 布局,也絕無可能發揮出預期效能。板級雜散電感 (Stray Inductance) 和寄生電容的交互作用,是制約一切高頻變換器發揮性能的根本物理瓶頸 。

5.1 開爾文源極 (Kelvin Source) 的深度物理機制與接線準則

在缺乏獨立開爾文源極的傳統封裝(如標準 3 引腳的 TO-247)或粗放的模塊走線布局中,柵極驅動返回回路與主功率輸出回路被迫共享著一段物理源極引腳或 PCB 大銅皮走線。這段無可避免的共享路徑在電學模型中等效為一個共源極寄生電感 (LS?) 。

當主功率回路開通或關斷時,會產生高達數十甚至數百 A/ns 的超高電流變化率 (di/dt)。這個急劇攀升或驟降的電流流經 LS? 時,會依據電磁定律感應出一個極強的反向電動勢:

VL?=LS?×dtdiD??

在開啟期間,該感應電壓的極性與門極驅動電壓恰好相反。它在物理層面上抵消了實際施加在 SiC 芯片內部柵極與源極之間的有效正向驅動電壓。其直接后果是嚴重削弱了瞬態驅動電流,造成器件開啟過程變得遲緩拖沓,開關損耗急劇飆升 ;而在關斷瞬態,該寄生電動勢又會反過來異常抬高門極電位,極大地加劇了本就棘手的寄生導通風險 。

為徹底斬斷這一惡性負反饋,現代大功率模塊及高級分立器件(例如采用 TO-247-4L 封裝或具備獨立輔助控制端子的模塊型號)均標配了專屬的開爾文源極(或稱驅動源極)引腳 。其不可觸碰的核心布局設計原則是:門極驅動回路的返回路徑必須以極短的走線直接且排他性地連接至該開爾文源極引腳,絕對禁止在驅動電路的任何物理節點處將其與攜帶大電流的主功率源極 (Power Source) 地網絡短接混用 。這種從芯片級延伸至 PCB 級的絕對物理隔離,徹底消除了主功率回路高頻強電流對微弱敏感的控制回路產生的感性負反饋干擾,從而真正釋放了 SiC MOSFET 實現納秒級極速開關的核心潛能 。

5.2 布局拓撲優化與磁場對消的高級布線策略

在落實開爾文隔離之后,進一步優化驅動回路的另一個重中之重是必須將柵極回路自身的環路寄生電感 (LG?) 壓縮至物理極限 。 針對這一目標的具體實施策略包括:

極致的物理縮距設計: 驅動 IC 芯片、作為緩沖放大級的圖騰柱電路以及相關的外圍保護網絡(特別是針對高頻瞬態響應的非對稱 TVS 鉗位二極管、AMC 專用晶體管電路、DESAT 檢測阻容網絡等)必須緊貼功率模塊的柵極與開爾文源極引腳進行貼片布局。核心鉗位組件的走線距離應被嚴格控制在 20 mm 甚至更短的范圍內,以切斷寄生電感的物理累積路徑 。

回流路徑重疊與磁場對消: 門極的輸出驅動走線 (Gate) 與源極的信號回流走線 (Return) 絕不能平鋪在同一層形成一個張開的大環路,而應當分別鋪設在彼此緊挨的上下兩個 PCB 層級中(例如 Top 層與緊鄰的內部 Ground 層),且保證兩者在垂直方向上保持近乎完全的重疊投影,形成微帶線結構或借由大面積敷銅 (Copper Pour) 進行包裹 。這種高度重合的走線分布允許前向驅動電流和回流電流所激發的高頻電磁場在物理空間上實現高度耦合與相互抵消 (Magnetic Field Cancellation),從而將這一關鍵環路的寄生電感抑制在幾納亨級別的極低水平 。由于大功率模塊的引腳物理布局常常導致布線必須發生平面交叉(因為引腳定義往往與傳統驅動器布局呈鏡像反轉),設計者必須利用多層板特性確保過孔互聯的交叉路徑維持閉合環路面積均等,借此令感應到的電磁干擾電動勢極性相反并完成二次自身抵消 。

高壓母線的高頻去耦網絡: 此外,對于承載數百安培的高壓直流母線,必須在距離模塊導電端子僅僅幾厘米的核心輻射范圍內,密集布置具備極低等效串聯電感 (ESL) 特性的高頻吸收電容器陣列(如優質薄膜電容或車規級多層陶瓷電容 MLCC)。這些電容充當了高頻諧波的泄放旁路,能夠顯著縮短整體高頻瞬態換流功率環路 (Lloop?) 的物理長度并降低寄生電感,從根本源頭上大幅削弱導致器件關斷擊穿的浪涌過壓問題 。

6. 商業化大功率 SiC 模塊參數提取與驅動需求映射:以 BASiC Semiconductor 體系為例

為將前述繁復的物理理論與工程實際緊密結合,本節對 BASiC Semiconductor (基本半導體) 研發的涵蓋多款工業級與車規級、覆蓋 1200 V 耐壓規格的 SiC MOSFET 模塊進行了系統性的橫向數據提取與底層驅動需求映射分析。這類先進模塊的額定電流涵蓋了從 60 A 起步,直至單體 540 A 的寬廣范圍,并采用了 34 mm、62 mm 以及極具代表性的高密度 Pcore?2 ED3 等多種先進封裝基板(如鋁碳化硅與高性能氮化硅 Si3?N4? AMB 基板結合銅基底)形式。這些詳實的第一手測試數據全面而客觀地反映了處于全球前沿水平的碳化硅模塊在高頻、高密、高可靠性應用場景下的電氣屬性演進規律與物理極限 。

6.1 器件靜態絕緣參數與最佳驅動電壓邏輯選型對比

如下表所示,本文詳細提取了不同封裝規格與容量模塊的門極耐受物理極限以及出廠推薦的最佳驅動電壓偏置參數:

| 模塊型號 | 額定電流 / 封裝 | VGSS? 絕對最大耐受 | 推薦驅動 VGS(on)?/VGS(off)? | VGS(th)? (典型值@25℃) | RDS(on)? (典型值@25℃) |

|---|---|---|---|---|---|

| BMF60R12RB3 | 60 A / 34mm | +22 V / -10 V | +18 V / -5 V | 2.7 V | 21.2 mΩ |

| BMF80R12RA3 | 80 A / 34mm | +22 V / -10 V | +18 V / -4 V | 2.7 V | 15.0 mΩ |

| BMF120R12RB3 | 120 A / 34mm | +22 V / -10 V | +18 V / -5 V | 2.7 V | 10.6 mΩ |

| BMF160R12RA3 | 160 A / 34mm | +22 V / -10 V | +18 V / -4 V | 2.7 V | 7.5 mΩ |

| BMF240R12KHB3 | 240 A / 62mm | +22 V / -10 V | +18 V / -5 V | 2.7 V | 5.3 mΩ |

| BMF240R12E2G3 | 240 A / Pcore?2 | +25 V / -10 V | +1820 V / -40 V | 4.0 V | 5.5 mΩ |

| BMF360R12KHA3 | 360 A / 62mm | +22 V / -10 V | +18 V / -5 V | 2.7 V | 3.3 mΩ |

| BMF540R12KHA3 | 540 A / 62mm | +22 V / -10 V | +18 V / -5 V | 2.7 V | 2.2 mΩ |

| BMF540R12MZA3 | 540 A / Pcore?2 | +22 V / -10 V | +18 V / -5 V | 2.7 V | 2.2 mΩ |

技術洞察與趨勢分析: 絕大多數被測試的 1200 V 模塊均展現出了高度一致的不對稱偏置驅動邏輯,均強烈推薦采用 +18 V / -5 V 或是 +18 V / -4 V 的驅動電壓配置組合 。這一數據的收斂并非巧合,而是深刻印證了前文所述的半導體物理折中:+18 V 的開啟電平恰好足以使得 1200 V 的溝道層充分反型并呈現出極低的導通電阻(不同模塊隨晶粒并聯數量增加,電阻從 21.2 mΩ 平滑下降直至驚人的 2.2 mΩ),同時這又距離由柵氧化層物理厚度決定的絕對最大破壞閾值(普遍為 +22 V 乃至部分型號能達到的 +25 V)保留了充分且必要的設計安全裕量。

特別值得業界關注的是關于器件閾值電壓 (VGS(th)?) 設計針對高頻魯棒性的演進。盡管該系列中的主流模塊均將開啟閾值控制在 2.7 V 的典型水平以兼顧通用驅動匹配性,但其中采用 Pcore?2 ED3 先進封裝技術的 BMF240R12E2G3 型號,通過革新的柵極工藝結構,將其標稱閾值電壓顯著提升到了 4.0 V (并且其工藝離散性被精準控制在 3.0 V 到 5.0 V 之間) 。這一看似不起眼的參數提升,從根本上強化了該模塊在面對超強寄生米勒電容注入干擾以及地電位反彈噪聲時的原生抑制能力,極大程度地降低了其在復雜高頻工況下的雜散導通概率 。這一高魯棒性設計解釋了為何該特定型號甚至被廠家允許在某些苛刻環境中實行 VGS(off)?=0V 的關斷操作下界,打破了寬禁帶器件必然需要深度負電壓關斷的傳統認知約束,為工程師在隔離電源拓撲設計(特別是去除負壓電荷泵)上提供了寶貴的降本優化空間 。

6.2 大功率并聯的動態開關電荷挑戰與內部驅動阻抗耗散趨勢

在模塊內部,為了實現高達數百安培的總電流輸出,封裝體必然需要采用多個微小的 SiC MOSFET 裸芯片進行并聯互聯。這種大功率并聯架構的技術代價,最直觀地反映在了總開關電荷 (QG?) 的規模化累積以及相應的驅動阻抗 (RG(int)?) 平衡設計上。

| 模塊型號 | 總門極電荷 QG? (典型值) | 內部柵極電阻 RG(int)? (典型值) | 測試基準狀態 (dV / 導通阻抗電流配置) |

|---|---|---|---|

| BMF60R12RB3 | 168 nC | 1.40 Ω | 800V,55A,+18V/?5V |

| BMF80R12RA3 | 220 nC | 1.70 Ω | 800V,80A,+18V/?4V |

| BMF120R12RB3 | 336 nC | 0.70 Ω | 800V,110A,+18V/?5V |

| BMF160R12RA3 | 440 nC | 0.85 Ω | 800V,160A,+18V/?4V |

| BMF240R12KHB3 | 672 nC | 2.85 Ω | 800V,220A,+18V/?5V |

| BMF360R12KHA3 | 880 nC | 2.93 Ω | 800V,240A,+18V/?5V |

| BMF540R12KHA3 | 1320 nC | 1.95 Ω | 800V,360A,+18V/?5V |

技術洞察與趨勢分析: 上述圖表直觀地揭示了門極驅動電源在應對巨型模塊時的功率挑戰。從入門級的 60 A 型號拓展至頂級 540 A 規格的演進過程中(電流承載能力增加了整整 9 倍),其對應的驅動負載——總門極電荷 QG? 從 168 nC 按近乎剛性的線性正比例狂飆至 1320 nC 。 為了衡量這種變化對系統設計的真實沖擊,我們可以進行一項極端的工程極限推演:假設目標電力電子系統(例如電動汽車的高頻 OBC 或牽引逆變器)運行在 50kHz 的連續開關頻率下,并且采用典型的雙極性驅動電壓配置(即 +18 V 導通至 -5 V 關斷,形成全振幅 23V 的電平躍遷)。 此時,為了維持單顆 540 A 容量模塊 (如 BMF540R12KHA3) 的基礎開關動作,其驅動器必須持續提供的基礎靜態門極充電功率即可通過理論公式得出:

PG?=1320nC×50kHz×23V=1.518W

這區區 1.5 W 的功耗看似微不足道,但必須清醒認識到這僅僅是維持單側開關管驅動的凈充放電消耗,且這些熱量大部分將直接以焦耳熱的形式耗散在驅動器微小的推挽緩沖級結構或外置的柵極阻尼電阻網絡中。該量化數據無可辯駁地表明,在此類超大功率的 SiC 模塊應用中,由于驅動電流常常需要數安培乃至十數安培的瞬態尖峰吞吐,系統級設計絕不能存在絲毫僥幸心理。不僅必須強制采用推放電電流能力達到十安培級、具備獨立分離式推挽放大級的強化隔離驅動 IC,同時還必須在驅動器本體與外圍吸收電阻周圍實施極其嚴謹的 PCB 散熱過孔或附銅冷卻設計方案。

另一個值得深思的工程規律體現在內部柵極電阻 (RG(int)?) 的阻值分布上。在常規的半導體并聯理論模型中,隨著內部晶粒數量的成倍增多,模塊總的并聯內阻理應表現出顯著的下降趨勢。然而,實際的商業數據卻展現了微妙的制衡策略:例如旗艦級的 540 A 模塊 (BMF540R12KHA3) 反而刻意將整體等效內部柵極電阻維持在一個高達 1.95 Ω 的阻值水平 。這種有悖常理的設計在物理機制上有其深意:在一個包含數十個并聯高頻開關節點的微觀系統中,故意植入并保留一定額度的內置阻尼 (RG(int)?),能夠極其有效地在模塊內部第一時間吸收并平抑多個微小 SiC 晶粒間由于參數微小離散和互連微電感不均而引發的高頻共振或電流群聚現象。這一制造工藝側的前瞻性保留,從物理本源上極大地預先緩解了外部驅動器由于面對極低阻抗負載時所帶來的高頻阻尼匹配設計壓力。

6.3 開關延遲特性映射與惡劣溫度環境下的非線性反轉

開關變換速度是驗證 SiC 技術優勢的最終落腳點。通過對相關大功率型號在標準室溫 (25℃) 與極限惡劣運行高溫 (175℃) 兩種截然不同的熱工況下進行的精確開關響應速度提取,我們可以清晰地觀測到極其特殊的熱電非線性耦合效應。

| 模塊型號 (電流容量) | 驅動網絡電阻配置 RG(on)?/RG(off)? | 開啟延遲窗口 td(on)? (25℃ / 175℃) | 上升爬坡時間 tr? (25℃ / 175℃) | 關斷延遲脫出 td(off)? (25℃ / 175℃) |

|---|---|---|---|---|

| BMF240R12KHB3 (240 A) | 3.0Ω/1.2Ω | 65 ns / 56 ns | 37 ns / 29 ns | 110 ns / 124 ns |

| BMF540R12KHA3 (540 A) | 5.1Ω/1.8Ω | 119 ns / 89 ns | 75 ns / 65 ns | 205 ns / 256 ns |

熱力學與時間常數的非線性非對稱特征分析: 上述從大量實驗圖表中解析出的開關數據網絡,揭示了一個僅存在于先進寬禁帶器件中且極具研究價值的反常理物理學現象:當系統處于惡劣的負載狀態,模塊核心結溫從平靜的 25℃ 一路攀升至狂暴的 175℃ 時,模塊的導通動作延遲 (td(on)?) 與電壓/電流上升爬坡時間 (tr?) 不僅沒有變慢,反而出現了顯著且穩定的加速縮短效應。例如,旗艦級 BMF540R12KHA3 模塊在高溫下的開啟延遲時間令人驚訝地從 119 ns 縮水至 89 ns,進入爬坡的響應速度變得更為凌厲 。這一違反直覺的數據表現,與那些由于高溫下載流子晶格散射加劇導致整體載流子遷移率直線下降,進而使得一切開關動作都全面變慢拖沓的傳統大功率 Si 硅基雙極型器件(如高壓 IGBT)形成了鮮明的技術代差對比。 該“高溫加速”效應的最核心底層物理機制歸因于 SiC MOSFET 柵極開啟閾值電壓 (VGS(th)?) 本身所具備的強烈負溫度系數。當模塊處于極高熱量環境中時,由于反型層形成的物理勢壘有所削弱,閾值電壓被自動拉低,這就導致在給定的相同的驅動電源內阻及相同的高速電容充電曲線下,觸發導通動作的電壓交點被顯著提前了。

然而,物理世界的因果定律總是在另一方面收取代價。同樣的高溫誘發的閾值下沉現象,會在關斷周期引發了截然相反的關斷延遲 (td(off)?) 嚴重惡化與下降時間變緩效應。數據精準顯示,同型號模塊的關斷脫出延遲時間在高溫下從 205 ns 被災難性地拉長到了 256 ns 。這種非對稱的時間膨脹規律是對所有高級電力電子保護設計工程師敲響的最嚴厲警鐘。關斷速度變得遲緩拖沓,意味著在真正發生短路故障的惡劣熱工況下,AMC 有源米勒鉗位控制的介入時序以及 DESAT 檢測比較器盲區時間 (tblank?) 判定機制的動作窗口將被無情地擠壓侵蝕。它不可辯駁地證明,模塊在滿載甚至過載短路狀態下掙脫毀滅、進入安全斷流狀態所需要經歷的高能量應力時間,將比常溫預期更為漫長危險。這一關鍵發現無可爭議地鎖定了工程保護校準的“木桶效應短板”:在為大功率多芯片 SiC 系統規劃致命的短路保護網絡盲區時間計算時,絕對禁止以室溫 25℃ 下測得的各項響應參數作為安全演算的標尺,必須且只能將基于該器件聲明能夠忍受的最高極端額定工作結溫 (Tvjop?=175°C) 的衰退后遲緩延遲時間,作為錨定系統最終動作邊界并計算 SCWT 裕量的唯一法則與安全底線,才能在物理上徹底保證整套系統的生還率。

7. 結語

碳化硅 (SiC) MOSFET 功率半導體架構,正憑借其令人震撼的 3.26 eV 寬帶隙材料物理紅利,以及由此衍生的打破記錄的高頻切換速度和超低導通阻抗耗散屬性,深刻且不可逆轉地重塑并引領著整個下一代高密度電力電子能量轉換拓撲網絡的發展格局。但是,若想在此類極致緊湊的變換器中,真正將晶粒微縮帶來的能量密度潛能轉化為安全、穩定且長期可靠的產品輸出,其先決條件且唯一的充要條件,便在于其最為貼身的外圍控制中樞——高級門極驅動器必須能夠在納秒與微秒的夾縫中,完美、果決地執行全行業最為嚴苛與非線性的電氣動態響應與主動干預保護邏輯。

通過本文由宏觀材料特性深入至微觀電子漂移行為的系統性剖析框架,我們能夠沉淀出以下用于指引新一代硬核設計與實踐工程走向的終極核心研判準則:

首先,由于器件具有令人發指的高 dV/dt 納秒級開關切變率,寄生在其脆弱節點周遭的米勒反饋位移瞬態電流,已經成為隨時可能引發半橋災難性直通毀滅的最大夢魘。在構建高頻開關隔離防御陣線時,現代設計絕不能容忍任何單薄的妥協方案。必須強制引入由智能控制 IC 接管的有源米勒鉗位 (AMC) 來提供動態的泄放通道,以在低電平時剝離有害電荷;并且,當空間不可避免的寬闊物理走線和過孔結構產生的引線寄生電感嚴重削弱了低阻抗旁路的真實響應時,應當于最貼近功率模塊裸芯片源柵端子的封裝管腳處,物理加裝響應速度突破 1 ns 極限的非對稱瞬態電壓抑制器 (TVS) 陣列(即那些能夠承受高頻斬波能量并嚴格支撐如 +24 V/-10 V 這樣極不均等電壓防線的專門抗擾保護微縮器件),從而在虛實結合之間構成一套阻絕任何感性毛刺偷襲的鐵壁防御。

其次,受制于由微小晶粒體積衍生而出的遠高于傳統的電流集中密度以及極度匱乏的熱緩沖容載能力,新一代 SiC MOSFET 的致命短路耐受存活時間 (SCWT) 已被逼近了通常不到三個微秒的生命倒計時。這對傳統的過流容錯邏輯發起了致命挑戰。應對如此短暫的安全窗口,這不僅要求所搭建的去飽和 (DESAT) 全自動短路監控雷達體系必須具備近乎零延遲的納秒級嗅探捕捉與狀態翻轉判定能力,更對研發人員施加了極其苛刻的設計審視要求——必須通過極其精密復雜的阻抗/時間參數平衡博弈計算(如精準鎖定限流分壓電阻 RDESAT? 取值在幾千歐姆狹小窗口以平衡泄放遲滯,并極度苛求將具備超低微觀本征結電容的并聯高頻高壓隔離二極管應用到盲區電容 CBLK? 旁路隔離陣列中),徹底規避和切斷由超強 dV/dt 引發且長久以來一直被工程界忽視的電容性誤觸發通道風險。同時,系統必須果斷引入并啟用受控階梯泄放緩降技術的智能軟關斷 (Soft Turn-off) 和多段電平管理 (2LTO) 強干預手段,以此堅決遏制、鉗制并最終消化那些可能因巨大短路關斷瞬間突變導致且極易超過隔離耐壓上限并擊穿絕緣層薄膜的電磁致命回火(浪涌過電壓)。

最后,對來自諸如 BASiC Semiconductor 的工業應用量產主流多芯 1200 V 模塊系列中巨量真實物理參數的大數據驗證深刻揭示:隨著功率目標由初級的 60 A 向前向深層探入 540 A 的頂級應用水準,驅動器承載的能量傳遞需求將無視任何緩和地呈現出極具挑戰的成倍爆炸性猛增;更加致命的是,模塊的每一個動態開關和電容特性時間曲線,都展示出隨內部結區極端高頻熱化積聚而不可控制地發生的非線性且高度反常的熱依變偏離。因此在所有的主從布局中,底層硬件與載板必須嚴格遵循建立在開爾文源極徹底物理絕緣與走線寄生電感結構拓撲最小化基礎之上的強制隔離布線設計法則,毫無保留地將微弱的控制電源、采樣監控回傳網絡與大功率強磁場能量傳輸路徑在物理空間維度和交變磁場輻射維度上實現徹底的雙重解耦斬斷。唯有如此,將深層次的微觀硅碳材料晶格電氣缺陷機理、超高速主動反饋與隔離抗擾保護邏輯網絡以及宏觀的電磁交變抵消布線工程統籌納入到一個不可分割的系統全局考量框架之內,我們方能真正降伏這種充滿野性的高能器件,最終構筑起具有高度自愈能力、絕對物理隔離且能量轉化效率逼近完美的大功率碳化硅工業轉換拓撲架構。

審核編輯 黃宇

-

功率模塊

+關注

關注

11文章

679瀏覽量

47018 -

碳化硅

+關注

關注

26文章

3526瀏覽量

52626 -

DESAT

+關注

關注

0文章

21瀏覽量

6346

發布評論請先 登錄

碳化硅(SiC)模塊短路保護與多級自適應去飽和(DESAT)技術研究

打線門極電阻,助力SiC碳化硅模塊性能提升

傾佳電子碳化硅SiC MOSFET驅動特性與保護機制深度研究報告

傾佳電子BTD5452R隔離型SiC碳化硅MOSFET門極驅動器米勒鉗位串擾抑制與DESAT短路保護的技術價值

碳化硅 (SiC) 功率模塊門極驅動技術:精密電壓鉗位與 DESAT 短路保護的設計細節

碳化硅 (SiC) 功率模塊門極驅動技術:精密電壓鉗位與 DESAT 短路保護的設計細節

評論