解析 MICREL SY89295U:1.5GHz 精密 LVPECL 可編程延遲線

在電子設計領域,可編程延遲線是實現信號精確延遲控制的關鍵組件。今天,我們來深入探討 MICREL 公司的 SY89295U 可編程延遲線,它在高速信號處理和時鐘同步等應用中具有重要作用。

文件下載:SY89295UTG.pdf

一、產品概述

SY89295U 是一款采用數字控制信號對輸入信號進行延遲的可編程延遲線。其延遲范圍從 3.2ns 到 14.8ns,以 10ps 為增量進行調節。輸入信號為 LVPECL 類型,支持 2.5V ±5% 或 3.3V ±10% 的電源供電,并且能在 -40°C 到 +85°C 的全工業溫度范圍內穩定工作。

(一)控制機制

延遲通過一個 10 位的控制字進行離散調節,每一位的變化對應 10ps 的延遲增量。第 11 位 D[10] 用于級聯多個 SY89295U 芯片,從而擴展延遲范圍。此外,輸入引腳 IN 和 /IN 在浮空時默認處于低電平狀態,控制寄存器接口可接受 CMOS 或 TTL 電平信號,提供了極大的靈活性。

(二)相關產品

對于需要模擬延遲輸入的應用,可選擇 SY89296L 可編程延遲芯片,它具備精細調節控制功能。SY89295U 和 SY89296U 都屬于 Micrel 的高速 Precision Edge? 產品線。

二、產品特性

(一)高精度與高性能

- 頻率與上升/下降時間:保證在溫度和電壓變化時,AC 性能穩定,最大工作頻率 (f_{MAX}) 大于 1.5GHz,上升/下降時間小于 160ps。

- 低抖動設計:總抖動小于 10ps,周期到周期抖動小于 (2 ps{RMS}),隨機抖動小于 (1 ps{RMS}),確保信號的穩定性和準確性。

(二)可編程延遲范圍

延遲范圍為 3.2ns 到 14.8ns,以 10ps 為步長進行調節,能滿足多種不同的延遲需求。

(三)單調性提升

相較于 MIC100EP195,SY89295U 具有更高的單調性,積分非線性(INL)為 ±10ps。

(四)多種輸入輸出特性

- 參考電壓輸出:提供 (V_{BB}) 輸出參考電壓,可用于單端輸入信號源的偏置或交流耦合輸入的重新偏置。

- 輸入兼容性:并行輸入可接受 LVPECL 或 CMOS/LVTTL 信號。

- 低電壓操作:支持 2.5V ±5% 和 3.3V ±10% 的低電壓供電,適用于多種電源環境。

- 寬溫度范圍:能在 -40°C 到 +85°C 的工業溫度范圍內正常工作。

(五)封裝形式

提供 32 引腳(5mm x 5mm)的 MLF 和 32 引腳的 TQFP 封裝,方便不同的 PCB 布局需求。

三、應用場景

(一)時鐘去偏斜

在時鐘信號傳輸過程中,由于線路長度、負載等因素的影響,時鐘信號可能會出現偏斜。SY89295U 可以精確調節時鐘信號的延遲,消除時鐘偏斜,確保系統中各個模塊的時鐘同步。

(二)時序調整

在數字電路中,不同信號之間的時序關系至關重要。通過 SY89295U 對信號進行延遲調整,可以優化信號的時序,提高系統的性能和穩定性。

(三)孔徑中心對準

在數據采集和處理系統中,孔徑中心對準是確保數據準確采集的關鍵。SY89295U 可以用于調整采樣時鐘的延遲,使采樣時刻與信號的最佳采樣點對齊,提高數據采集的精度。

四、訂購信息

| SY89295U 提供多種不同的封裝和版本,包括含鉛和無鉛封裝,以及卷帶包裝選項。具體的訂購信息如下: | 產品編號 | 封裝類型 | 工作范圍 | 封裝標記 | 引腳鍍層 |

|---|---|---|---|---|---|

| SY89295UMI | MLF - 32 | 工業級 | SY89295U | Sn - Pb | |

| SY89295UMI TR | MLF - 32 | 工業級 | SY89295U | Sn - Pb | |

| SY89295UTI | T32 - 1 | 工業級 | SY89295U | Sn - Pb | |

| SY89295UTITR | T32 - 1 | 工業級 | SY89295U | Sn - Pb | |

| SY89295UMG | MLF - 32 | 工業級 | Pb - Free bar - line indicator SY89295U with Pb - Free NiPd Au | ||

| SY89295UMGTR | MLF - 32 | 工業級 | Pb - Free bar - line indicator SY89295U with NiPd Au Pb - Free | ||

| SY89295UTG | T32 - 1 | 工業級 | Pb - Free bar - line indicator SY89295U with Pb - Free NiPd Au | ||

| SY89295UTGTR | T32 - 1 | 工業級 | Pb - Free bar - line indicator SY89295U with Pb - Free NiPd Au |

需要注意的是,對于裸片的可用性,需要聯系廠家確認,且裸片僅在 (T_{A}=25^{circ} C) 時保證直流電氣性能。新設計推薦使用無鉛封裝。

五、引腳配置與功能

(一)引腳配置

SY89295U 采用 32 引腳封裝,不同的引腳具有不同的功能。以下是部分重要引腳的介紹:

- D[9:0]:CMOS、ECL 或 TTL 控制位,用于調節從 IN 到 Q 的延遲。這些引腳內部有下拉電阻,浮空時默認低電平。

- D[10]:用于級聯設備以擴展延遲范圍,同時驅動 CASCADE 和 /CASCADE 引腳,內部有下拉電阻,浮空時默認低電平。

- IN, /IN:LVPECL/ECL 信號輸入引腳,用于輸入需要延遲的信號。IN 引腳內部有 75kΩ 下拉電阻,浮空時默認邏輯低電平。

- VBB:參考電壓輸出引腳,可用于單端輸入信號源的偏置或交流耦合輸入的重新偏置。使用時需通過 0.01μF 電容與 VCC 去耦,最大灌/拉電流為 ±0.5mA。

- VEF, VCF:參考電壓相關引腳,用于設置邏輯標準和輸入選擇電壓。

- GND:接地引腳,MLF 封裝的外露焊盤必須連接到與接地引腳電位相同的接地平面。

- LEN:ECL 控制輸入引腳,高電平時鎖存 D[9:0] 和 D[10] 位,低電平時這些鎖存器透明。

- SETMIN, SETMAX:ECL 控制輸入引腳,用于設置延遲的最小值和最大值。

- VCC:正電源引腳,需使用 0.1μF 和 0.01μF 的低 ESR 電容進行旁路。

- /Cascade, Cascade:LVPECL 差分輸出引腳,用于級聯多個 SY89295U 以擴展延遲范圍。

- /EN:LVPECL 單端控制輸入引腳,低電平時 Q 為 IN 的延遲版本,高電平時 Q 為差分低電平。

- /Q, Q:LVPECL 差分輸出引腳,Q 是 IN 的延遲版本,輸出需用 50Ω 電阻端接到 VCC - 2V。

- NC:無連接引腳。

(二)真值表

| 輸入/輸出 | 0 | 1 | 0 | 1 |

|---|---|---|---|---|

| L | 0 | 1 | 0 | |

| /OUT | OUT | NI/ | NI |

| 數字控制鎖存 | LEN | 鎖存動作 |

|---|---|---|

| 0 | 直通 D[10:0] | |

| 1 | 鎖存 |

| 輸入使能 | /EN | Q, /Q |

|---|---|---|

| 0 | IN, /IN 延遲 | |

| 1 | 鎖存 D[10:0] |

六、電氣特性

(一)絕對最大額定值

- 電源電壓(VCC):-0.5V 到 +4.0V

- 輸入電壓(VIN):-0.5V 到 VCC

- LVPECL 輸出電流(IOUT):連續 50mA,浪涌 100mA

- 引腳溫度(焊接,20 秒):+260°C

- 存儲溫度范圍(TS):-65°C 到 +150°C

(二)工作額定值

- 電源電壓(VCC):+2.375V 到 +3.6V

- 環境溫度(TA):-40°C 到 +85°C

- 封裝熱阻:

- MLF(θJA):靜止空氣下 35°C/W

- MLF(ψJB):結到板 28°C/W

- TQFP(θJA):靜止空氣下 28°C/W

- TQFP(ψJB):結到板 20°C/W

(三)直流電氣特性

在不同的電源電壓和溫度條件下,SY89295U 的直流電氣特性有所不同。例如,在 (V{CC}=3.3V) 時,輸入高電壓(VIH)為 2.075 - 2.420V,輸入低電壓(VIL)為 1.355 - 1.675V;在 (V{CC}=2.5V) 時,VIH 為 1.275 - 1.62V,VIL 為 0.555 - 0.875V。

(四)交流電氣特性

- 最大工作頻率(fMAX):時鐘 (V_{OUT} ≥ 400mV) 時,為 1.5GHz

- 傳播延遲(tpd):IN 到 Q 的延遲根據控制字 D[0 - 10] 的不同而變化,范圍從 4200ps 到 14800ps

- 可編程范圍(tRANGE):tpd(max.) - tpd(min.)為 8300ps

- 占空比偏斜(tSKEW):tPHL - tPLH 為 25ps

- 步長延遲(Δt):不同控制位的變化對應不同的延遲步長,從 10ps 到 9220ps 不等

- 積分非線性(INL):±10ps

- 建立時間(tS):D 到 LEN 為 200ps,D 到 IN 為 350ps,/EN 到 IN 為 300ps

- 保持時間(tH):LEN 到 D 為 200ps,IN 到 /EN 為 400ps

- 釋放時間(tR):SETMAX 到 LEN 為 500ps,/EN 到 IN 為 500ps,SETMIN 到 LEN 為 450ps

- 抖動特性:周期到周期抖動小于 (2 ps{RMS}),總抖動小于 10psPP,隨機抖動小于 (1 ps{RMS})

- 輸出上升/下降時間(tr, tf):20% 到 80% 時,Cascade 為 90 - 160ps,Q 為 50 - 300ps

- 占空比:45 - 55%

七、典型工作特性與時序圖

(一)典型工作特性

在 (V{CC}=3.3V),(GND = 0),(D{iN}=100 mV),(T_{A}=25^{circ} C) 的條件下,給出了延遲與 D[9:0] 的關系曲線以及幅度與頻率的關系曲線。這些曲線可以幫助工程師更好地了解 SY89295U 在不同條件下的性能表現。

(二)時序圖

提供了單端和差分信號的電壓擺幅圖,以及輸入和輸出階段的電路圖。這些時序圖有助于工程師理解信號的傳輸和處理過程,確保系統的正確設計和調試。

八、輸出接口應用

(一)并行端接

在 +3.3V 系統中,通過合適的電阻進行并行端接,以匹配負載阻抗,減少信號反射。對于 +2.5V 系統,需要調整電阻值。

(二)Y 端接

同樣用于匹配負載阻抗,適用于不同的系統需求。

(三)未使用 I/O 端接

對于未使用的 I/O 引腳,采用適當的端接方式,以避免信號干擾和反射。

九、應用信息

(一)布局與電源濾波

為了獲得最佳性能,建議使用良好的高頻布局技術,對 (V_{CC}) 電源進行濾波,并保持接地連接短。在可能的情況下,使用多個過孔,并采用受控阻抗傳輸線與 SY89295U 的數據輸入和輸出接口。

(二)(V_{BB}) 參考電壓

(V{BB}) 引腳是內部生成的參考電壓,僅用于 SY89295U。當不使用時,該引腳應保持未連接狀態。它主要用于處理單端 PECL 輸入和交流耦合應用中的輸入重新偏置。在使用時,(V{BB}) 的灌/拉電流必須限制在 0.5mA 以下。

(三)設置 D 輸入邏輯閾值

在 SY89295U 的 GND 電源為零伏的設計中,D 輸入可以兼容 CMOS、TTL、PECL 或 LVPECL 電平信號。通過合理連接 (V{CF}) 和 (V{EF}),可以滿足不同邏輯標準的需求。

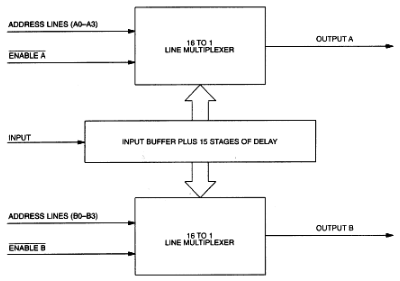

(四)級聯應用

兩個或多個 SY89295U 可以級聯使用,以擴展延遲范圍。每個額外的 SY89295U 會增加約 3.2ns 的最小延遲和 10240ps 的延遲范圍。內部級聯電路允許 SY89295U 在無需外部門控的情況下進行級聯。

十、總結

SY89295U 作為一款高性能的可編程延遲線,具有高精度、低抖動、寬延遲范圍等優點,適用于多種高速信號處理和時鐘同步應用。在設計過程中,工程師需要根據具體的應用需求,合理選擇封裝、電源電壓和控制方式,同時注意布局、電源濾波和信號端接等問題,以確保系統的性能和穩定性。你在實際應用中是否遇到過類似的可編程延遲線,你是如何解決相關問題的呢?歡迎在評論區分享你的經驗。

-

高速信號處理

+關注

關注

0文章

47瀏覽量

6551

發布評論請先 登錄

SY89297U,GB以太網交換機延遲線評估板

通過數字控制和模擬控制延遲輸入信號的SY89296L可編程延遲線評估板

SY89296L 2.5V/3.3V 2.5GHz可編程延遲線評估板

如何計算延遲線的最大工作頻率

Data Delay Device, Inc模擬和數字延遲線以及延遲線應用模塊和濾波器的設計者

基于CPLD的高速可程控數字延遲線系統的設計與實現

SY89295U EV 延遲線參考設計

基于SY89295U EV延遲線的參考設計

基于SY89295L EV延遲線的參考設計

DS1045雙通道4位可編程延遲線的器件特性

解析 MICREL SY89295U:1.5GHz 精密 LVPECL 可編程延遲線

解析 MICREL SY89295U:1.5GHz 精密 LVPECL 可編程延遲線

評論