SM320VC5421-EP 定點數字信號處理器深度剖析

在當今數字化浪潮中,數字信號處理器(DSP)的性能和功能對各類電子設備的運行起著關鍵作用。SM320VC5421-EP 作為一款性能卓越的定點數字信號處理器,為我們帶來了諸多創新特性和強大功能。下面,我們就來深入了解這款處理器。

文件下載:sm320vc5421-ep.pdf

一、處理器概述

1.1 核心特性

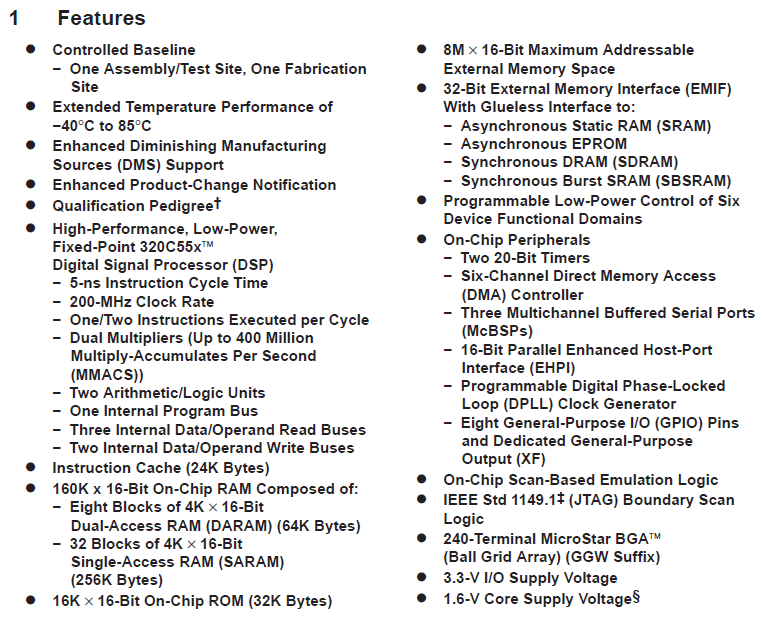

SM320VC5421-EP 具備諸多令人矚目的特性。它采用受控基線,擁有單一的組裝/測試地點和單一的制造地點,這確保了產品的質量穩定性。其工作溫度范圍為 -40°C 至 85°C,能適應較為惡劣的環境。同時,它還提供了增強的制造資源支持和產品變更通知資格認證,為長期使用提供了保障。

這款處理器是 200-MIPS 的雙核 DSP,由兩個獨立的子系統組成。每個核心都擁有先進的多總線架構,包含三條獨立的 16 位數據存儲器總線和一條程序總線,能夠高效地處理數據和指令。40 位算術邏輯單元(ALU)搭配 40 位桶形移位器和兩個 40 位累加器,為復雜的算術運算提供了強大的支持。此外,它還具備 17 位×17 位并行乘法器和 40 位加法器,可實現單周期的乘法/累加(MAC)操作,大大提高了運算效率。

1.2 與 5420 的遷移

對于從 5420 遷移到 5421 的用戶來說,需要注意一些變化。5421 的內存結構進行了調整,引入了 128K x 16 位的雙向共享內存,增強了數據共享和處理能力。DMA 功能也得到了增強,能夠訪問外部和內部內存,并且 HPI 和 DMA 內存映射也進行了相應的更新。此外,5421 還增加了 2K x 16 位的 ROM 用于引導加載,VCO 引腳被 HOLDA 引腳取代,同時新增了 HOLD 引腳。McBSPs 也進行了更新,具備 128 通道選擇能力,并且 CLKX/R 引腳可作為內部時鐘速率發生器的輸入,無需額外引腳。

二、功能模塊詳解

2.1 內存系統

2.1.1 各類內存類型

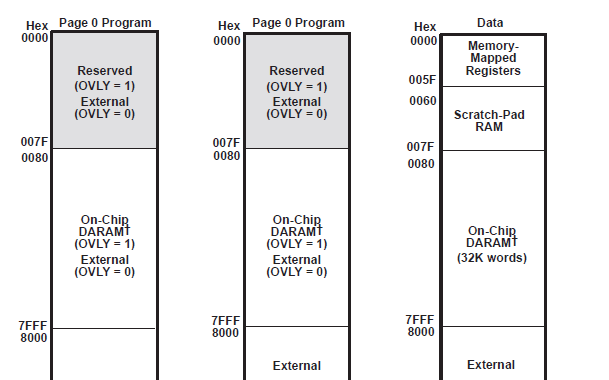

SM320VC5421-EP 的內存系統豐富多樣。每個子系統都有 32K 16 位字的片上雙訪問 RAM(DARAM),可在每個機器周期內訪問兩次,既可以存儲數據,也可以存儲程序。片上單訪問 RAM(SARAM)同樣為 32K 16 位字,每個周期只能訪問一次,主要用于存儲數據。此外,還有 128K 16 位字的片上雙向共享 DARAM,供兩個 DSP 子系統共享,用于存儲程序。每個子系統還有 2K 16 位字的片上 ROM,用于引導加載功能。

2.1.2 內存訪問規則

程序內存空間可尋址高達 512K 16 位字,采用分頁擴展內存方案。訪問程序內存時,不同頁面和地址范圍的訪問規則不同,例如在低 32K 部分,取決于 OVLY 的狀態;在高 32K 部分,取決于 MP/MC 和 XPC 的值。數據內存空間為單頁 64K,低 32K 始終從本地 DARAM 訪問,高 32K 則取決于 DROM 的狀態。I/O 空間也是單頁 64K,訪問始終是外部的。

2.2 外設模塊

2.2.1 軟件可編程等待狀態發生器

該發生器可將外部總線周期延長至最多 14 個機器周期,以適應較慢的片外內存和 I/O 設備。軟件等待狀態寄存器(SWWSR)控制其操作,可針對五個不同的地址范圍插入不同數量的等待狀態。軟件等待狀態控制寄存器(SWCR)中的軟件等待狀態乘數(SWSM)位可將等待狀態數量乘以 1 或 2。

2.2.2 可編程銀行切換

可編程銀行切換可在跨越內存銀行邊界時自動插入一個周期,避免總線爭用。銀行切換控制寄存器(BSCR)定義了內存銀行的大小,不同的位具有不同的功能,如確定外部內存銀行大小、插入額外周期、發送處理器間中斷等。

2.2.3 并行 I/O 端口

5421 擁有 64K 字的 I/O 端口地址空間,可通過 PORTR 和 PORTW 進行尋址。IS 信號指示通過 I/O 端口的讀寫訪問,設備可通過 I/O 端口輕松與外部設備接口,同時所需的片外地址解碼邏輯較少。SELA/B 引腳用于選擇訪問外部 I/O 空間的子系統。

2.2.4 16 位雙向主機端口接口(HPI16)

HPI16 是 TMS320C54x DSP 8 位主機端口接口的增強版,允許 16 位主機訪問 DSP 片上內存。它具有 16 位雙向數據總線、多個數據選通和控制信號,支持多路復用和非多路復用地址/數據模式。在多路復用模式下,主機可通過 HD 雙向數據總線訪問 HPI16 數據寄存器、地址寄存器和控制寄存器;在非多路復用模式下,主機可通過 18 位 HA 地址總線和 16 位 HD 數據總線訪問 HPI16 數據寄存器和地址寄存器。

2.2.5 多通道緩沖串行端口(McBSP)

5421 提供六個多通道緩沖串行端口(McBSPs),每個子系統有三個。McBSP 支持全雙工通信,具有雙緩沖數據寄存器,可實現連續數據流。它還具有獨立的幀和時鐘控制,可直接與多種設備接口,如 T1/E1 成幀器、MVIP 交換兼容設備等。此外,McBSP 支持多達 128 個通道的多通道收發,可選擇多種數據大小,具備 μ 律和 A 律壓縮功能,可編程幀同步和數據時鐘極性,以及內部時鐘和幀生成功能。

2.2.6 直接內存訪問(DMA)控制器

5421 包含兩個 6 通道的直接內存訪問(DMA)控制器,每個子系統一個。DMA 控制器可獨立于 CPU 進行數據傳輸,控制對片外程序/數據/IO 和內部數據/程序內存的訪問。它具有六個通道,每個通道可獨立編程優先級,支持 32 位內部訪問和 16 位外部訪問。DMA 控制器的同步事件可通過 DSYN 位字段選擇,中斷選擇可通過 INTSEL 位字段進行。此外,DMA 還支持自動初始化模式,可通過全局重載寄存器實現連續和重復操作。

2.3 時鐘與定時器

2.3.1 軟件可編程鎖相環(PLL)

時鐘發生器由鎖相環(PLL)電路組成,需要外部時鐘源提供參考時鐘。PLL 可將參考時鐘頻率乘以一個比例因子來生成設備時鐘,也可將參考時鐘除以 2 或 4。軟件可編程 PLL 具有高度靈活性,可通過 16 位內存映射的時鐘模式寄存器(CLKMD)進行控制,包括 PLL 乘數、分頻器、計數器等設置。

2.3.2 硬件定時器

54x 設備具有 16 位定時電路和 4 位預分頻器。定時器計數器在每個 CLKOUT 周期減 1,當計數器減到 0 時,會產生定時器中斷。定時器可通過特定狀態位停止、重啟、重置或禁用,當 TOUT 位在通用 I/O 控制寄存器中設置為 1 時,定時器輸出脈沖將驅動在 GPIO3 上。

三、電氣特性與時序

3.1 電氣規格

SM320VC5421-EP 的絕對最大額定值規定了其在不同條件下的工作范圍,如電源電壓、存儲溫度等。推薦的工作條件包括設備的電源電壓、輸入輸出電壓、電流等參數。電氣特性則描述了在推薦工作條件下的輸出電壓、輸入電流、電源電流等性能指標。

3.2 時鐘選項

處理器支持多種時鐘選項,包括將參考時鐘除以 2 或 4 來生成內部機器周期,以及通過 PLL 將參考時鐘乘以 N 來生成內部機器周期。不同時鐘選項有相應的時序要求和開關特性。

3.3 接口時序

外部內存接口、并行 I/O 接口、HPI 接口等都有各自的時序要求和開關特性。例如,內存讀寫操作的訪問時間、設置時間、保持時間等都有明確的規定,這些時序參數對于確保處理器與外部設備的正確通信至關重要。

四、總結與思考

SM320VC5421-EP 以其豐富的功能和卓越的性能,為電子工程師在設計各類數字信號處理系統時提供了強大的支持。其多核架構、多樣化的內存系統和豐富的外設模塊,使得它能夠滿足不同應用場景的需求。然而,在實際應用中,我們也需要根據具體需求合理配置處理器的各項參數,充分發揮其性能優勢。同時,對于處理器的電氣特性和時序要求,我們必須嚴格遵守,以確保系統的穩定性和可靠性。大家在使用這款處理器的過程中,是否也遇到過一些有趣的問題或者有獨特的應用經驗呢?歡迎在評論區分享交流。

-

數字信號處理器

+關注

關注

5文章

519瀏覽量

28431 -

功能模塊

+關注

關注

0文章

22瀏覽量

2963

發布評論請先 登錄

SM320VC5510AEP定點數字信號處理器的詳細英文資料概述

SM320VC5421-EP 增強型產品定點數字信號處理器

SM320C6414-EP/SM320C6415-EP/SM320C6416-EP定點數字信號處理器數據表

SM320DM642-EP視頻/圖像定點數字信號處理器數據表

SM320VC5421-EP 定點數字信號處理器深度剖析

SM320VC5421-EP 定點數字信號處理器深度剖析

評論