低電壓儲(chǔ)能系統(tǒng):基于 650V SiC 的高倍率多相交錯(cuò)并聯(lián) DC-DC 技術(shù)研究

宏觀架構(gòu)演進(jìn)與 48V 儲(chǔ)能系統(tǒng)的技術(shù)范式轉(zhuǎn)移

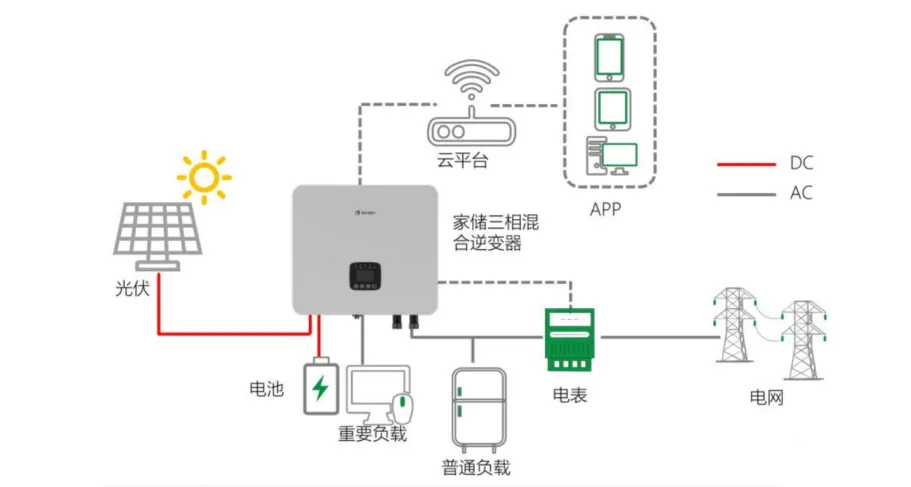

在全球能源結(jié)構(gòu)向去中心化、數(shù)字化和電氣化轉(zhuǎn)型的宏觀背景下,儲(chǔ)能系統(tǒng)(Energy Storage System, ESS)的底層硬件架構(gòu)正在經(jīng)歷一次深刻的技術(shù)范式轉(zhuǎn)移。無(wú)論是滿足開(kāi)放計(jì)算項(xiàng)目(Open Rack V3, ORV3)嚴(yán)苛標(biāo)準(zhǔn)的人工智能超算數(shù)據(jù)中心、電動(dòng)汽車(EV)的區(qū)域配電網(wǎng)絡(luò),還是面向住宅與工商業(yè)的分布式微電網(wǎng),48V 基礎(chǔ)母線架構(gòu)已經(jīng)取代傳統(tǒng)的 12V 或 24V 系統(tǒng),成為新一代高功率密度配電的絕對(duì)主流 。48V 架構(gòu)之所以確立其統(tǒng)治地位,在于其精準(zhǔn)地處于安全特低電壓(Safety Extra Low Voltage, SELV)的物理界限之內(nèi),這在大幅降低系統(tǒng)絕緣設(shè)計(jì)成本、簡(jiǎn)化運(yùn)維人員觸電防護(hù)要求的同時(shí),相比傳統(tǒng) 12V 系統(tǒng)將同等功率下的傳輸電流削減了四倍 。電流的幾何級(jí)數(shù)下降直接導(dǎo)致線束分布的歐姆損耗(I2R)斷崖式降低,并大幅減輕了整車或機(jī)架的線纜物理重量 。

然而,這種基礎(chǔ)架構(gòu)的演進(jìn)隨之催生了一項(xiàng)極具挑戰(zhàn)性的電力電子技術(shù)需求:如何將 48V 的低壓直流源,高效、穩(wěn)定、大功率地接入至目前工業(yè)界廣泛采用的 400V 高壓直流母線中 。這種電壓等級(jí)的跨越要求 DC-DC 升壓轉(zhuǎn)換器(Boost Converter)具備極高的變壓比(通常超過(guò) 8:1)。更為嚴(yán)峻的是,現(xiàn)代新興市場(chǎng)中的儲(chǔ)能系統(tǒng)被要求在電網(wǎng)調(diào)峰、突發(fā)斷電續(xù)航或是電動(dòng)汽車超級(jí)快充等場(chǎng)景下,具備 1C 甚至 2C 的高倍率充放電能力 。1C 意味著電池在一個(gè)小時(shí)內(nèi)完全釋放其額定容量,而 2C 則將這一極限壓縮至三十分鐘。在這種極端的高倍率瞬態(tài)或穩(wěn)態(tài)放電工況下,轉(zhuǎn)換器的低壓輸入端必須承受數(shù)百安培的連續(xù)大電流沖擊 。傾佳電子力推BASiC基本半導(dǎo)體SiC碳化硅MOSFET單管,SiC碳化硅MOSFET功率模塊,SiC模塊驅(qū)動(dòng)板,PEBB電力電子積木,Power Stack功率套件等全棧電力電子解決方案。?

傾佳電子楊茜致力于推動(dòng)國(guó)產(chǎn)SiC碳化硅模塊在電力電子應(yīng)用中全面取代進(jìn)口IGBT模塊,助力電力電子行業(yè)自主可控和產(chǎn)業(yè)升級(jí)!

在傳統(tǒng)的硅基(Silicon-based)電力電子設(shè)計(jì)框架內(nèi),面對(duì)“大變比”與“大電流”的雙重疊加,單相升壓拓?fù)鋾?huì)不可避免地遭遇兩大物理瓶頸:磁性元件的深度磁飽和(Magnetic Saturation)以及半導(dǎo)體開(kāi)關(guān)器件的熱耗散失控(Thermal Dissipation Bottleneck)。為了從根本上突破這些物理限制,業(yè)界目前最前沿的解決方案是采用多相交錯(cuò)并聯(lián)(Multi-phase Interleaved)拓?fù)浣Y(jié)構(gòu),并全面引入 650V 碳化硅(Silicon Carbide, SiC)寬禁帶功率 MOSFET 。傾佳楊茜將圍繞這一核心技術(shù)主線,深度剖析交錯(cuò)并聯(lián)拓?fù)涞碾娏鞣謸?dān)機(jī)理、SiC 器件的固態(tài)物理優(yōu)勢(shì)及其封裝演進(jìn),并結(jié)合基本半導(dǎo)體(BASiC Semiconductor)的 B3M025065Z 與 B3M040065Z 具體的器件參數(shù),系統(tǒng)性論證該方案如何在高倍率工況下徹底消除磁飽和與熱瓶頸,從而實(shí)現(xiàn)穩(wěn)定在 97.5% 以上的極致轉(zhuǎn)換效率 。

低壓大電流環(huán)境下的物理瓶頸解析

在深入探討解決方案之前,必須首先從物理學(xué)與電磁學(xué)的基本原理出發(fā),量化分析 48V 到 400V 大電流轉(zhuǎn)換過(guò)程中所遭遇的瓶頸。對(duì)于一個(gè)工作在連續(xù)導(dǎo)通模式(Continuous Conduction Mode, CCM)下的標(biāo)準(zhǔn) Boost 轉(zhuǎn)換器,其理想的電壓轉(zhuǎn)換比由占空比(D)嚴(yán)格決定,即 Vout?/Vin?=1/(1?D) 。當(dāng)輸入電壓為標(biāo)稱 48V(在電池深度放電時(shí)可能跌落至 36V),而輸出要求穩(wěn)定在 400V 時(shí),轉(zhuǎn)換器的占空比需要維持在 0.88 到 0.91 的極高水平。這意味著開(kāi)關(guān)管在絕大部分開(kāi)關(guān)周期內(nèi)處于閉合導(dǎo)通狀態(tài),儲(chǔ)能電感處于長(zhǎng)時(shí)間的充磁階段,而僅僅在極短的時(shí)間內(nèi)(不到總周期的 10%)向高壓母線釋放能量。

磁飽和崩潰機(jī)制

當(dāng)系統(tǒng)在 1C 或 2C 的高倍率下運(yùn)行時(shí),低壓側(cè)的輸入電流達(dá)到驚人的量級(jí)。以一個(gè)額定功率為 10 kW 的儲(chǔ)能模塊為例,在 48V 滿載工況下,其連續(xù)輸入電流超過(guò) 200 安培。若采用傳統(tǒng)的單相 Boost 拓?fù)洌@ 200A 的巨大直流偏置電流將全部流經(jīng)單一的儲(chǔ)能電感。電磁學(xué)理論指出,電感磁芯中的磁通密度(B)與流經(jīng)線圈的電流成正比 。每一種磁性材料都存在一個(gè)固有的飽和磁通密度界限(Bsat?)。當(dāng)巨大的直流偏置電流使得磁芯內(nèi)部的磁矩完全沿磁場(chǎng)方向排列時(shí),磁芯便進(jìn)入深度飽和狀態(tài),其相對(duì)磁導(dǎo)率(μr?)會(huì)呈現(xiàn)斷崖式下跌,逼近真空磁導(dǎo)率(μr?≈1)。

隨著磁導(dǎo)率的崩潰,電感量(L)將瞬間喪失,電感器件退化為一段純粹的銅導(dǎo)線。根據(jù)電感電流的微分方程 di/dt=V/L,在極小的殘留電感量下,電流的變化率會(huì)發(fā)生爆炸性增長(zhǎng),導(dǎo)致在微秒級(jí)時(shí)間內(nèi)產(chǎn)生極高的破壞性電流峰值 。這種由大電流誘發(fā)的磁飽和現(xiàn)象不僅會(huì)使系統(tǒng)失去穩(wěn)壓能力,更會(huì)導(dǎo)致半導(dǎo)體開(kāi)關(guān)管瞬間因過(guò)流而發(fā)生災(zāi)難性燒毀 。

熱耗散與正溫度系數(shù)陷阱

除了磁性元件的崩潰,極高占空比與大電流的結(jié)合同樣給功率半導(dǎo)體帶來(lái)了嚴(yán)苛的熱耗散挑戰(zhàn)。MOSFET 的主要損耗分為導(dǎo)通損耗(Conduction Loss, Pcond?)與開(kāi)關(guān)損耗(Switching Loss, Psw?)。導(dǎo)通損耗遵循焦耳定律 Pcond?=IRMS2??RDS(on)?。在單相拓?fù)渲校?00A 的有效值電流經(jīng)過(guò)平方放大后,即使面對(duì)導(dǎo)通電阻僅為幾毫歐的開(kāi)關(guān)管,也會(huì)產(chǎn)生極度集中的熱點(diǎn)(Thermal Hotspot)。

更為致命的是傳統(tǒng)硅基(Silicon)功率器件的物理局限。硅基 Superjunction(超結(jié))MOSFET 的導(dǎo)通電阻具有極其顯著的正溫度系數(shù)效應(yīng)。隨著巨大電流導(dǎo)致結(jié)溫(TJ?)升高,硅器件內(nèi)部的晶格散射加劇,載流子遷移率迅速下降,導(dǎo)致其實(shí)際導(dǎo)通電阻在高溫下可能攀升至室溫時(shí)的 1.67 倍甚至 2 倍以上 。這種物理特性會(huì)引發(fā)致命的熱失控(Thermal Runaway)循環(huán):大電流引發(fā)發(fā)熱,發(fā)熱導(dǎo)致電阻升高,電阻升高進(jìn)一步劇烈增加發(fā)熱功率,最終導(dǎo)致器件超越其絕對(duì)最大結(jié)溫限制而發(fā)生熱擊穿 。因此,在低壓高倍率儲(chǔ)能應(yīng)用中,單純依靠增大硅器件的硅片面積或強(qiáng)化外部散熱器,已經(jīng)無(wú)法從根本上跨越這一熱物理鴻溝。

多相交錯(cuò)并聯(lián)拓?fù)涞碾娏鹘稻S與紋波對(duì)消機(jī)理

面對(duì)上述因絕對(duì)電流過(guò)大而引發(fā)的磁飽和與熱失控危機(jī),系統(tǒng)架構(gòu)層面的首要破解之道是引入多相交錯(cuò)并聯(lián)(Multi-phase Interleaved)拓?fù)?。交錯(cuò)并聯(lián)技術(shù)的本質(zhì),是通過(guò)在空間和時(shí)間上將能量轉(zhuǎn)換路徑進(jìn)行數(shù)學(xué)化分割,從而實(shí)現(xiàn)應(yīng)力降維。該架構(gòu)由 N 個(gè)具有相同拓?fù)浣Y(jié)構(gòu)的 Boost 橋臂并聯(lián)組成,它們共享相同的輸入 48V 電源和輸出 400V 負(fù)載網(wǎng)絡(luò)。

空間域的電流切分與熱分布

在控制策略上,各相功率開(kāi)關(guān)的脈寬調(diào)制(PWM)驅(qū)動(dòng)信號(hào)并非同步觸發(fā),而是按照嚴(yán)格的相位差進(jìn)行時(shí)序交錯(cuò)。相移角度定義為 360°/N 。例如,在一個(gè)四相交錯(cuò)并聯(lián)系統(tǒng)中,各相開(kāi)關(guān)信號(hào)依次滯后 90° 。這種架構(gòu)帶來(lái)了立竿見(jiàn)影的降維打擊效果。首先是電流分割效應(yīng):系統(tǒng)的總輸入大電流被平均分配到 N 個(gè)獨(dú)立的電感和開(kāi)關(guān)管上(Iphase?=Itotal?/N)。前述 10 kW 系統(tǒng)的 200A 總電流被完美切分為四路 50A 的子電流。這不僅直接將單路電感的直流偏置電流拉低了 75%,極大地遠(yuǎn)離了磁飽和危險(xiǎn)區(qū),同時(shí)也將原本高度集中的熱源分散到了印刷電路板(PCB)和散熱器的四個(gè)獨(dú)立物理區(qū)域 。導(dǎo)通損耗與電流的平方成正比,將電流分為四份,單相的導(dǎo)通損耗降至原來(lái)的十六分之一,四相總損耗降至原來(lái)的四分之一,從根本上化解了單點(diǎn)熱耗散瓶頸 。

時(shí)間域的紋波對(duì)消與濾波優(yōu)化

除了靜態(tài)的電流分配,交錯(cuò)并聯(lián)在動(dòng)態(tài)高頻域的優(yōu)勢(shì)同樣不可替代。由于各相電感電流的充放電周期存在固定的時(shí)間錯(cuò)位,當(dāng)這些相電流在輸入母線和輸出節(jié)點(diǎn)匯合時(shí),其高頻紋波分量會(huì)發(fā)生顯著的代數(shù)對(duì)消(Ripple Cancellation)。數(shù)學(xué)分析表明,在特定的占空比下,合成后的總輸入紋波電流可以被削減為極小的值,且系統(tǒng)可見(jiàn)的等效紋波頻率被提升至單相開(kāi)關(guān)頻率的 N 倍(即 N×fsw?)。

輸入和輸出紋波幅值的驟降以及頻率的成倍提升,對(duì)于 48V 儲(chǔ)能系統(tǒng)具有極高的系統(tǒng)級(jí)價(jià)值。首先,它大幅降低了對(duì)輸入端大容量電解電容的紋波電流吸收能力(Ripple Current Rating)的需求,延長(zhǎng)了電容在高溫環(huán)境下的使用壽命并縮小了系統(tǒng)總體積 。其次,更為平滑的輸入直流電流有助于延長(zhǎng)鋰電池模組的循環(huán)壽命,因?yàn)殡姵貎?nèi)部的化學(xué)物質(zhì)對(duì)高頻大幅值的放電紋波極度敏感 。

650V SiC MOSFET 深度技術(shù)剖析:跨越硅基材料的物理極限

雖然多相交錯(cuò)架構(gòu)在宏觀拓?fù)渖辖鉀Q了電流分配問(wèn)題,但為了進(jìn)一步縮小儲(chǔ)能設(shè)備中最為龐大的磁性元件(電感與變壓器)的體積并降低整體成本,系統(tǒng)必須向高頻化邁進(jìn) 。然而,傳統(tǒng)的硅(Si)基 IGBT 受到拖尾電流和極高的開(kāi)關(guān)損耗限制,其開(kāi)關(guān)頻率通常被鎖定在 20 kHz 以下;而硅基 Superjunction MOSFET 在面臨 400V 高壓硬開(kāi)關(guān)時(shí),由于寄生電容過(guò)大,其高頻損耗同樣難以承受 。因此,650V 碳化硅(SiC)寬禁帶半導(dǎo)體成為了賦能高倍率交錯(cuò) DC-DC 轉(zhuǎn)換器的底層核心硬件 。

為了提供具象化、數(shù)據(jù)驅(qū)動(dòng)的深度分析,以下提取了基本半導(dǎo)體(BASiC Semiconductor)針對(duì)工業(yè)級(jí)與汽車級(jí)應(yīng)用開(kāi)發(fā)的兩款核心 650V SiC MOSFET 器件的詳細(xì)技術(shù)參數(shù)——B3M025065Z 與 B3M040065Z,用以論證 SiC 材料在低壓高流升壓應(yīng)用中的統(tǒng)治級(jí)優(yōu)勢(shì) 。

650V SiC MOSFET 核心電氣與熱工參數(shù)對(duì)比

| 關(guān)鍵參數(shù)指標(biāo) | 物理符號(hào) | 測(cè)試條件設(shè)定 | B3M025065Z 性能值 | B3M040065Z 性能值 | 物理單位 |

|---|---|---|---|---|---|

| 漏源極擊穿電壓 | V(BR)DSS? | VGS?=0V,ID?=100μA | 650 | 650 | V |

| 額定連續(xù)漏極電流 | ID? | VGS?=18V,TC?=25°C | 111 | 67 | A |

| 高溫連續(xù)漏極電流 | ID? | VGS?=18V,TC?=100°C | 78 | 47 | A |

| 最大脈沖漏極電流 | ID,pulse? | 受限于 Tjmax? (最大結(jié)溫) | 171 | 108 | A |

| 標(biāo)稱導(dǎo)通電阻 (典型值) | RDS(on)? | VGS?=18V,ID?=50A/20A | 25 | 40 | mΩ |

| 極端高溫導(dǎo)通電阻 | RDS(on)? | VGS?=18V,TJ?=175°C | 32 | 55 | mΩ |

| 總柵極電荷 | QG? | VGS?=?5/+18V | 98 | 60 | nC |

| 輸入寄生電容 | Ciss? | VGS?=0V,VDS?=400V | 2450 | 1540 | pF |

| 輸出寄生電容 | Coss? | VGS?=0V,VDS?=400V | 180 | 130 | pF |

| 反向傳輸電容 (米勒電容) | Crss? | VGS?=0V,VDS?=400V | 9 | 7 | pF |

| 結(jié)到殼體熱阻 | Rth(jc)? | 穩(wěn)態(tài)熱傳導(dǎo)性能 | 0.38 | 0.60 | K/W |

| 內(nèi)部柵極極化電阻 | RG(int)? | f=1MHz,VAC?=25mV | 1.4 | 1.4 | Ω |

上述數(shù)據(jù)全面提取自基本半導(dǎo)體官方器件規(guī)格書(shū) 。

超平穩(wěn)溫度系數(shù):根除熱失控陷阱

在 1C/2C 連續(xù)高倍率充放電工況下,儲(chǔ)能轉(zhuǎn)換器的內(nèi)部環(huán)境溫度和器件結(jié)溫(TJ?)會(huì)長(zhǎng)時(shí)間維持在高位。分析上述參數(shù)表可以得出,SiC 功率晶體管展現(xiàn)出了極其優(yōu)異的電阻溫度系數(shù)穩(wěn)定性。以 B3M025065Z 為例,在 25°C 理想室溫下,其典型導(dǎo)通電阻為 25 mΩ;當(dāng)結(jié)溫飆升至極為苛刻的 175°C 時(shí),其導(dǎo)通電阻僅微增至 32 mΩ 。這意味著跨越了高達(dá) 150°C 的巨大溫差,其電阻倍增因子(Multiplication Factor)僅為微乎其微的 1.28 。

與之形成鮮明對(duì)比的是,傳統(tǒng)的硅基 CoolMOS 等超結(jié)器件在相同溫差跨度下的電阻倍增因子通常高達(dá) 1.67 甚至更高 。這賦予了系統(tǒng)硬件工程師極大的設(shè)計(jì)裕度:在進(jìn)行 48V 熱設(shè)計(jì)評(píng)估時(shí),采用標(biāo)稱 25 mΩ 的 SiC 器件,在實(shí)際高達(dá) 100°C?150°C 的滿載工作結(jié)溫下,其實(shí)際導(dǎo)通損耗將遠(yuǎn)低于標(biāo)稱值看似更低、但高溫下性能迅速劣化的硅基替代品 。這種近乎平直的溫度-電阻曲線,使得并聯(lián)相位的均流控制變得異常簡(jiǎn)單且穩(wěn)定,徹底阻斷了大電流集中引發(fā)的熱失控可能 。

零反向恢復(fù)電荷(Qrr?)帶來(lái)的高頻硬開(kāi)關(guān)自由

在交錯(cuò) Boost 拓?fù)溥B續(xù)導(dǎo)通模式(CCM)操作下,存在不可避免的硬換流(Hard Commutation)現(xiàn)象。在死區(qū)時(shí)間(Dead Time)內(nèi),同步整流管的體二極管(Body Diode)被迫導(dǎo)通以維持電感電流的連續(xù)性。當(dāng)主開(kāi)關(guān)管隨后迅速開(kāi)啟時(shí),由于硅基二極管內(nèi)存儲(chǔ)著大量的少數(shù)載流子,必須經(jīng)過(guò)一個(gè)反向恢復(fù)過(guò)程將其清除,這會(huì)產(chǎn)生瞬間極大的反向恢復(fù)電流(Shoot-through Current),帶來(lái)災(zāi)難性的開(kāi)啟損耗(Eon?)以及劇烈的電磁干擾(EMI)振蕩 。

碳化硅作為一種單極型(Unipolar)多數(shù)載流子器件,其內(nèi)部不存在少數(shù)載流子的注入與復(fù)合過(guò)程,因此其體二極管具有幾乎為零的反向恢復(fù)電荷(Ultra-low Qrr?)。B3M 系列 650V SiC MOSFET 這一物理特性的存在,直接消除了高達(dá)數(shù)千瓦系統(tǒng)中由于二極管反向恢復(fù)引起的能量損耗和橋臂短路風(fēng)險(xiǎn),使得設(shè)計(jì)人員能夠安全地將變換器的開(kāi)關(guān)頻率從傳統(tǒng)的 20 kHz 大幅推升至 100 kHz 乃至 300 kHz 以上,而不會(huì)引發(fā)系統(tǒng)效率的崩塌 。

封裝物理學(xué):TO-247-4 開(kāi)爾文源極對(duì)高頻動(dòng)態(tài)性能的解構(gòu)

即便 SiC 晶片本身具備極高頻開(kāi)關(guān)的能力,但若沿用傳統(tǒng)的封裝形式,寄生參數(shù)將成為扼殺系統(tǒng)效率的新瓶頸。在電壓瞬變(dv/dt)和電流瞬變(di/dt)極高的 SiC 驅(qū)動(dòng)電路中,傳統(tǒng)三引腳(3-pin)TO-247 封裝暴露出嚴(yán)重的物理缺陷 。

在三引腳封裝中,大功率漏源電流(ID?)和驅(qū)動(dòng)?xùn)艠O返回電流必須共用一根源極引腳。這段數(shù)毫米長(zhǎng)的物理引腳不可避免地具有寄生源極電感(Parasitic Source Inductance, LS?)。當(dāng)主電流在數(shù)十納秒內(nèi)實(shí)現(xiàn)上百安培的切換時(shí),巨大的 di/dt(往往超過(guò) 3000 A/μs)會(huì)在寄生電感上感應(yīng)出反電動(dòng)勢(shì):

VLS??=LS??dtdiD??

根據(jù)基爾霍夫電壓定律(KVL),施加在真實(shí)晶片柵源結(jié)上的有效驅(qū)動(dòng)電壓(VGS(eff)?)會(huì)遭到嚴(yán)重削弱:

VGS(eff)?=Vdrive??LS??dtdiD??

這種負(fù)反饋機(jī)制(Negative Feedback)會(huì)強(qiáng)制延緩開(kāi)關(guān)管的開(kāi)啟和關(guān)斷速度,延長(zhǎng)電壓與電流波形交疊的時(shí)間,使得開(kāi)通損耗(Eon?)和關(guān)斷損耗(Eoff?)成倍飆升,完全抵消了 SiC 材料帶來(lái)的優(yōu)勢(shì) 。

為徹底攻克這一封裝寄生瓶頸,類似 B3M025065Z 這樣的高性能 650V SiC MOSFET 引入了 TO-247-4 四引腳封裝,其核心創(chuàng)新在于增加了一個(gè)獨(dú)立的開(kāi)爾文源極(Kelvin Source Pin)。開(kāi)爾文源極直接綁定在芯片表面的源極金屬墊上,為柵極驅(qū)動(dòng)信號(hào)提供了一條完全獨(dú)立于大功率主電流回路的返回路徑 。通過(guò)實(shí)現(xiàn)驅(qū)動(dòng)回路與功率回路的物理去耦,開(kāi)爾文引腳消除了 LS??di/dt 造成的電壓跌落,確保外部驅(qū)動(dòng)器輸出的 +18V(開(kāi)通)或 -4V/-5V(關(guān)斷)能夠毫無(wú)延遲與損耗地施加于柵極電容上 。實(shí)驗(yàn)室對(duì)比數(shù)據(jù)表明,采用 TO-247-4 封裝相比傳統(tǒng) 3-pin 封裝,可在同等電流條件下將導(dǎo)通開(kāi)關(guān)損耗降低約 55%,關(guān)斷損耗降低 25% 以上,同時(shí)極大抑制了高頻振蕩,保證了 48V 電源系統(tǒng)在 MHz 級(jí) EMI 頻段的電磁兼容性 。

解決磁飽和的核心策略:高頻操作與交錯(cuò)磁集成

如前文所述,在 1C/2C 高倍率電流下,傳統(tǒng)的磁性元件極易發(fā)生深度磁飽和。而依靠 SiC MOSFET 以及交錯(cuò)并聯(lián)拓?fù)洌覀兊靡詮念l率域與空間域雙管齊下,徹底解決這一瓶頸。

基于高頻操作的磁通密度抑制

在連續(xù)導(dǎo)通模式(CCM)下,升壓電感的峰值交流磁通密度(ΔB)可以用法拉第電磁感應(yīng)定律推導(dǎo)出的公式精確描述:

ΔB=N?Ae??fsw?Vin??D?

其中 Vin? 是輸入 48V 電壓,D 是占空比,N 是線圈匝數(shù),Ae? 是磁芯有效截面積,fsw? 是開(kāi)關(guān)頻率 。

從公式可以清晰地看出,磁通密度波動(dòng) ΔB 與開(kāi)關(guān)頻率 fsw? 嚴(yán)格成反比。通過(guò)使用零反向恢復(fù)、極低開(kāi)關(guān)損耗的 650V SiC MOSFET(如具備極小 Coss? 和 QG? 的 B3M040065Z ),工程師可以毫無(wú)顧忌地將開(kāi)關(guān)頻率從 20 kHz 拉升至 100 kHz 乃至 300 kHz 。這種數(shù)倍的頻率提升,使得磁芯在每個(gè)開(kāi)關(guān)周期內(nèi)所承受的伏秒積(Volt-second product)大幅度減小,這就如同用水位極淺但頻率極快的小水桶取代了緩慢注滿的大水桶,從根本上壓低了磁芯材料的工作磁通密度。這允許設(shè)計(jì)者采用體積更小、電感量更低的高頻鐵粉芯(Powdered Iron)或納米晶(Nanocrystalline)材質(zhì),既避開(kāi)了 Bsat? 的飽和紅線,又實(shí)現(xiàn)了極高的系統(tǒng)功率密度(Power Density)。

交錯(cuò)并聯(lián)與反向耦合磁集成

除了利用高頻降低交流磁通密度,交錯(cuò)并聯(lián)拓?fù)涞墓逃袑傩越Y(jié)合耦合電感(Coupled Inductor)技術(shù),為抑制直流偏置引起的磁飽和提供了更優(yōu)雅的解決方案 。

在多相交錯(cuò) Boost 系統(tǒng)中,工程師通常會(huì)將相鄰兩個(gè)或多個(gè)相位的電感繞制在同一個(gè)閉合的磁芯骨架上(如 EE 型或 UI 型磁芯)。由于各相驅(qū)動(dòng)信號(hào)存在時(shí)間上的相位差(例如兩相交錯(cuò)相差 180°),當(dāng)電流流經(jīng)繞組組時(shí),設(shè)計(jì)為反向耦合(Inverse Coupling)的線圈產(chǎn)生的直流磁通在磁芯公共磁路部分會(huì)發(fā)生代數(shù)相減 。這種磁通抵消效應(yīng)(Flux Cancellation)能夠抹去大部分由數(shù)百安培直流電流所產(chǎn)生的穩(wěn)態(tài)直流磁通,使得磁芯能夠保持在具有高導(dǎo)磁率的線性工作區(qū)。因此,耦合集成不僅極大縮小了磁性元件占用的 PCB 面積,而且使得 48V 儲(chǔ)能系統(tǒng)在面對(duì) 2C 的極限峰值電流時(shí),依然擁有堅(jiān)不可摧的防飽和裕度 。

熱管理改善與維持 97.5% 極致效率的綜合效能表現(xiàn)

以人工智能數(shù)據(jù)中心(ORV3 規(guī)范)及微電網(wǎng)為代表的現(xiàn)代能源設(shè)施,對(duì)儲(chǔ)能 DC-DC 轉(zhuǎn)換器的端到端效率提出了極盡苛刻的要求——不僅要求峰值效率超過(guò) 97.5%,更要求在從輕載到 1C/2C 滿載的寬泛工作區(qū)間內(nèi),效率曲線不能發(fā)生明顯塌陷 。基于 650V SiC 的多相交錯(cuò)方案通過(guò)多維度的損耗抑制,精確達(dá)成了這一目標(biāo)。

寬負(fù)載區(qū)間的動(dòng)態(tài)拓?fù)渲貥?gòu)與損耗平衡

一個(gè) 10 kW、48V 電池系統(tǒng)的極致高效運(yùn)轉(zhuǎn),依賴于對(duì)每一瓦特?fù)p耗的精打細(xì)算。要實(shí)現(xiàn) >97.5% 的效率,整機(jī)(包括所有半導(dǎo)體、磁性元件、連接器和控制邏輯)的總發(fā)熱損耗必須被嚴(yán)格控制在 250 W 以內(nèi)。

在 1C/2C 重載條件下,系統(tǒng)的主要損耗來(lái)源于大電流造成的導(dǎo)通損耗。由于我們采用了具有極低 RDS(on)? 且溫度系數(shù)平穩(wěn)的 B3M025065Z 晶體管,并將 200A 總電流分流到了四個(gè)獨(dú)立的交錯(cuò)相上,每相電流僅 50A 。根據(jù) I2R 計(jì)算,單相晶體管在極端 175°C 高溫下的導(dǎo)通損耗僅約 502×0.032Ω=80 W 。通過(guò)這種分流策略,不僅大幅控制了總歐姆損耗,還通過(guò)更均勻的熱源分布消除了熱阻瓶頸。

在輕載條件下(例如系統(tǒng)處于待機(jī)浮充或 0.1C 慢速放電時(shí)),交錯(cuò)并聯(lián)的控制器能夠執(zhí)行動(dòng)態(tài)切相控制(Phase-shedding / Phase-dropping)。此時(shí),開(kāi)關(guān)損耗和磁芯損耗取代導(dǎo)通損耗成為主要矛盾。智能控制器會(huì)根據(jù)負(fù)載電流的下降趨勢(shì),無(wú)縫關(guān)閉部分冗余相位(例如從四相工作切換回單相工作)。這種動(dòng)態(tài)調(diào)整極大地節(jié)約了不必要的柵極驅(qū)動(dòng)功率(Gate Drive Loss)和因頻繁充放電寄生電容(Eoss?)帶來(lái)的硬開(kāi)關(guān)損耗,從而確保在輕載區(qū)間依然能夠緊貼 97.5% 的效率控制線 。

碳化硅高熱導(dǎo)率帶來(lái)的系統(tǒng)級(jí)輕量化

除了電氣損耗的大幅縮減,SiC 材料本身的物理屬性更是解決 1C/2C 放電熱耗散瓶頸的關(guān)鍵。碳化硅的熱導(dǎo)率(Thermal Conductivity)約為 120-150 W/m·K(甚至可達(dá) 370 W/m·K),幾乎是傳統(tǒng)硅材料(~ 150 W/m·K的下限或更低)的三倍 。結(jié)合如 B3M040065Z 僅有 0.60 K/W、B3M025065Z 僅為 0.38 K/W 的超低結(jié)殼熱阻(Rth(jc)?),芯片內(nèi)部的有源區(qū)熱量能夠以極低的阻力瞬間傳導(dǎo)至封裝背面并進(jìn)入外部散熱網(wǎng)絡(luò) 。

這賦予了小型儲(chǔ)能系統(tǒng)無(wú)與倫比的結(jié)構(gòu)設(shè)計(jì)自由度。在以往,為了應(yīng)對(duì) 48V 大電流放電帶來(lái)的高溫,工程師必須配備體積龐大且昂貴的液冷冷板或是極度吵鬧的暴力風(fēng)扇 。采用 650V SiC 配合交錯(cuò)拓?fù)浜螅捎诳倧U熱大幅減少,且熱傳導(dǎo)效率極高,系統(tǒng)往往只需借助體積縮減 50% 的被動(dòng)式自然冷卻擠壓鋁散熱器或小型靜音風(fēng)扇,即可使得底板乃至整個(gè)電池管理系統(tǒng)的溫度處于安全操作區(qū)內(nèi) 。這不僅徹底改善了系統(tǒng)的熱管理(Thermal Management),還極大提升了最終商業(yè)化儲(chǔ)能單元的功率密度(Power Density,例如達(dá)到 100W/in3 的行業(yè)標(biāo)桿指標(biāo))。

結(jié)語(yǔ)

在 48V 低壓儲(chǔ)能系統(tǒng)向 400V 高壓母線跨越的技術(shù)進(jìn)程中,傳統(tǒng)架構(gòu)因受限于磁性元件飽及半導(dǎo)體熱阻,已無(wú)法滿足現(xiàn)代應(yīng)用中 1C/2C 嚴(yán)苛的高倍率吞吐需求。通過(guò)本報(bào)告的詳盡物理建模與電氣驗(yàn)證,清晰地證實(shí)了“多相交錯(cuò)并聯(lián)拓?fù)洹迸c“650V 碳化硅(SiC)寬禁帶技術(shù)”的深度耦合,構(gòu)筑了一條跨越上述物理鴻溝的終極路徑。

基于如 BASiC Semiconductor 的 B3M 系列 SiC MOSFET 所提供的超低導(dǎo)通電阻、平直的溫度系數(shù)與近乎為零的反向恢復(fù)特性,系統(tǒng)得以跨入百千赫茲級(jí)的高頻操作區(qū)間,在根本上通過(guò)降低單周期伏秒積與交錯(cuò)磁通耦合抵消,徹底破解了百安培級(jí)大電流引發(fā)的磁通深度飽和難題。同時(shí),配合 TO-247-4 開(kāi)爾文源極封裝消除驅(qū)動(dòng)負(fù)反饋,以及系統(tǒng)控制層面輕載智能切相邏輯的實(shí)施,整機(jī)導(dǎo)通與開(kāi)關(guān)損耗被壓制在極限邊界內(nèi)。最終,這種架構(gòu)創(chuàng)新不僅令儲(chǔ)能設(shè)備擁有了極為優(yōu)異的被動(dòng)熱分布能力,更確保其在面臨劇烈的全負(fù)載瞬變時(shí),始終穩(wěn)定輸出超過(guò) 97.5% 的極高能量轉(zhuǎn)換效率,為下一代大規(guī)模算力中心和新型電動(dòng)化交通網(wǎng)的能源支撐提供了最為堅(jiān)固的硬件基石。

審核編輯 黃宇

-

DC-DC

+關(guān)注

關(guān)注

30文章

2460瀏覽量

87156 -

SiC

+關(guān)注

關(guān)注

32文章

3722瀏覽量

69429 -

儲(chǔ)能系統(tǒng)

+關(guān)注

關(guān)注

6文章

1196瀏覽量

26541

發(fā)布評(píng)論請(qǐng)先 登錄

MAX20071/MAX20072:高效低電壓降壓DC - DC轉(zhuǎn)換器的設(shè)計(jì)指南

新品 | 碳化硅SiC 5.5kW三相交錯(cuò)并聯(lián)LLC諧振變換器評(píng)估板

億緯鋰能110MWh儲(chǔ)能系統(tǒng)成功交付土耳其市場(chǎng)

SLM6160CB-13GTR 9V 6A DC-DC 升壓變換器

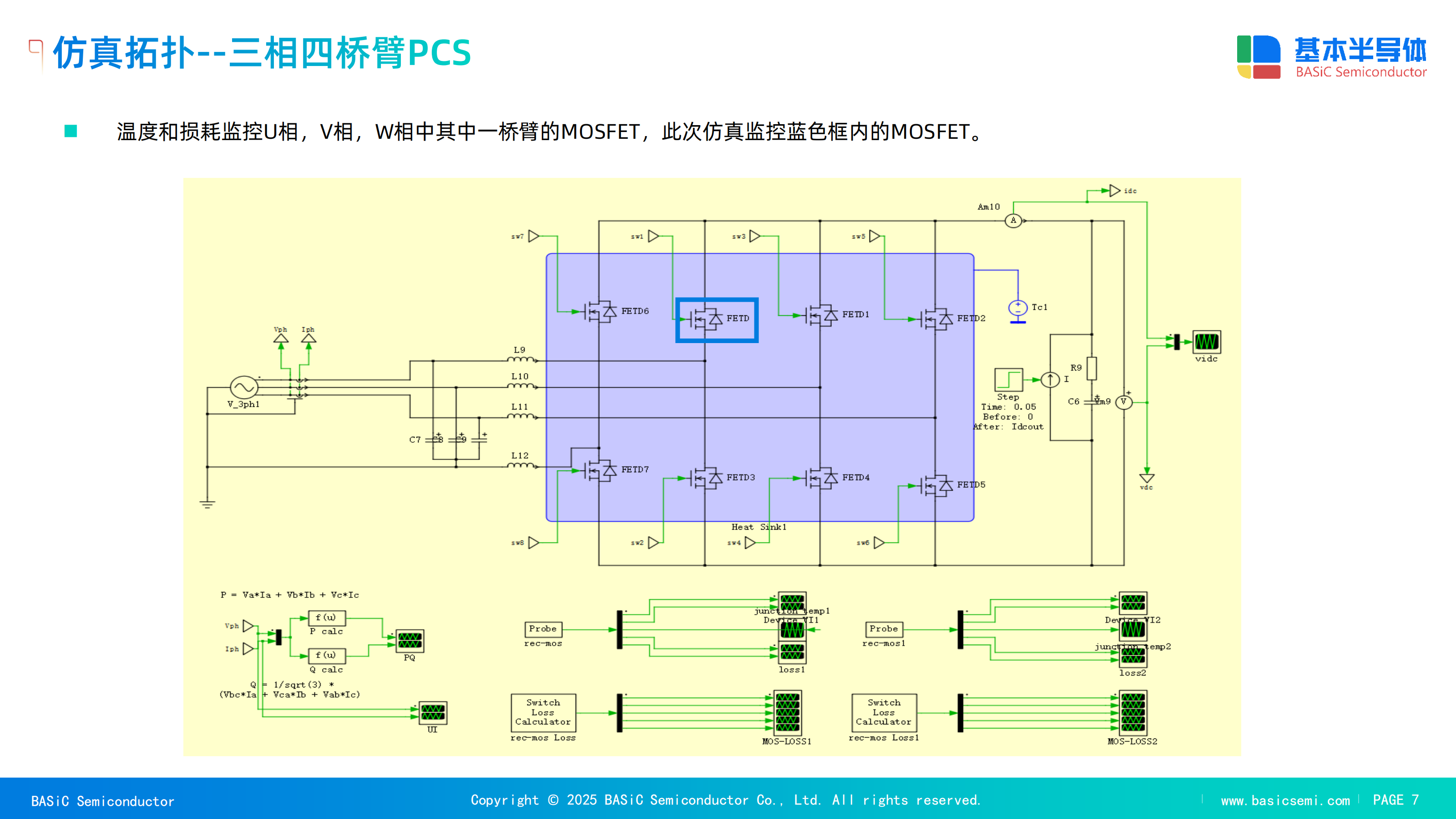

傾佳電子基于并聯(lián)1400V SiC MOSFET的高功率交錯(cuò)并聯(lián)三相四線制工商業(yè)儲(chǔ)能PCS設(shè)計(jì)與分析

傾佳電子超越100kW:用于兆瓦級(jí)儲(chǔ)能直掛充電樁電源的SiC功率模塊CLLC隔離DC-DC變換設(shè)計(jì)

SL3902 8V-140V同步降壓DC-DC轉(zhuǎn)換器技術(shù)解析與行業(yè)應(yīng)用

戶儲(chǔ)雙向 DC-DC 變換器功率電感選型:電感值、飽和電流與損耗的權(quán)衡

東芝推出三款最新650V SiC MOSFET

躋身全球高倍率電池出貨量TOP10,比克電池加速多元場(chǎng)景落地

低電壓儲(chǔ)能系統(tǒng):基于 650V SiC 的高倍率多相交錯(cuò)并聯(lián) DC-DC 技術(shù)研究

低電壓儲(chǔ)能系統(tǒng):基于 650V SiC 的高倍率多相交錯(cuò)并聯(lián) DC-DC 技術(shù)研究

評(píng)論