ICS951462:ATi RS/RD690 系統的可編程系統時鐘芯片

在電子設備的設計中,系統時鐘的穩定性和精確性對于設備的性能和可靠性起著至關重要的作用。今天我們要探討的主角——ICS951462,是一款專門為基于 ATI RS/RD690 的系統設計的可編程系統時鐘芯片,它能提供所需的各種時鐘,為系統的穩定運行提供有力支持。

文件下載:951462AGLFT.pdf

1. 推薦應用與輸出特性

ICS951462 主要應用于使用 AMD K8 處理器和 SB600 南橋的 ATI RS/RD690 系統。它具有豐富的輸出特性,包括 2 對 CPU 時鐘、8 對 SRC 時鐘、4 對 ATIG 時鐘,還有 1 個 66MHz 的 HyperTransport 時鐘種子、2 個 48MHz 的 USB 時鐘以及 3 個 14.318MHz 的參考時鐘。這些多樣化的輸出可以滿足系統不同組件的時鐘需求,為設備的高效運行提供保障。

2. 關鍵規格亮點

2.1 低抖動性能

ICS951462 在時鐘抖動方面表現出色。其中,CPU 輸出的周期到周期抖動小于 85ps,SRC 輸出和 ATIG 輸出的周期到周期抖動均小于 125ps。低抖動意味著時鐘信號的穩定性更高,能夠減少系統中的信號干擾和錯誤,提高系統的可靠性和性能。例如,在處理器的高速數據傳輸過程中,低抖動的時鐘能夠確保數據的準確傳輸,避免數據丟失或錯誤。

2.2 高精度頻率

這款芯片在 CPU、SRC 和 ATIG 時鐘上實現了 ±300ppm 的頻率精度。高精度的頻率可以保證系統中各個組件的時鐘同步,避免因時鐘偏差導致的設備故障或性能下降。在多處理器系統中,精確的時鐘同步能夠確保處理器之間的協調工作,提高整個系統的處理效率。

3. 功能與特性優勢

3.1 可編程時鐘請求引腳

ICS951462 設有 3 個可編程的時鐘請求引腳,用于控制 SRC 和 ATIG 時鐘。這些引腳可以通過編程實現靈活的時鐘配置,滿足不同系統的個性化需求。例如,在某些特定的應用場景中,可以根據系統的負載情況動態調整時鐘頻率,以達到節能和提高性能的目的。

3.2 頻率可編程與擴頻功能

ATIGCLK 時鐘的頻率是可編程的,工程師可以根據實際需求進行調整。同時,芯片還具備擴頻功能,能夠有效降低電磁干擾(EMI)。在電子設備日益小型化和集成化的今天,電磁干擾問題越來越突出,擴頻功能可以減少設備對其他電子設備的干擾,提高設備的電磁兼容性。

3.3 輸出禁用與高精度電容

芯片的輸出可以通過 SMBus 進行禁用,這為系統的調試和維護提供了便利。此外,外部晶體負載電容的使用可以確保最大的頻率精度,進一步提高時鐘信號的穩定性。

4. 引腳配置與功能

ICS951462 采用 64 - TSSOP 封裝,擁有眾多引腳,每個引腳都有其特定的功能。

4.1 電源引腳

包括 VDD 和 GND 引腳,為不同的時鐘輸出和芯片內部電路提供電源。例如,VDD48 為 48MHz 輸出提供 3.3V 電源,VDDSRC 為 SRC 時鐘提供 3.3V 電源等。合理的電源引腳配置可以確保芯片各個部分的正常工作,避免因電源問題導致的性能下降。

4.2 時鐘輸出引腳

如 48MHz_0 和 48MHz_1 輸出 48MHz 時鐘,SRCCLKT 和 SRCCLKC 輸出差分 SRC 時鐘等。這些時鐘輸出引腳的設計能夠滿足系統中不同組件對時鐘信號的需求,保證系統的正常運行。

4.3 控制引腳

像 SMBCLK 和 SMBDAT 是 SMBus 的時鐘和數據引腳,用于與控制器進行通信,實現對芯片的編程和控制。RESET_IN# 是實時活動低輸入引腳,當該引腳被觸發時,SMBus 將被重置為上電默認狀態。這些控制引腳的存在使得芯片的配置和管理更加靈活方便。

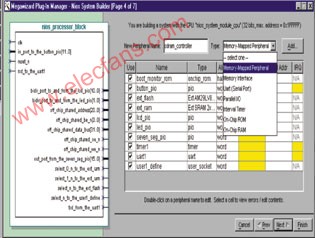

5. SMBus 通信與寄存器配置

ICS951462 通過 SMBus 接口實現對設備的全面控制。在進行讀寫操作時,需要遵循特定的通信協議。

5.1 寫操作流程

- 控制器發送起始位。

- 發送寫地址 D2 (H),芯片進行確認。

- 發送起始字節位置 N,芯片確認。

- 發送數據字節數 X,芯片確認。

- 依次發送從字節 N 到字節 N + X - 1 的數據,芯片逐個字節確認。

- 控制器發送停止位。

5.2 讀操作流程

- 控制器發送起始位。

- 發送寫地址 D2 (H),芯片確認。

- 發送起始字節位置 N,芯片確認。

- 控制器再次發送起始位。

- 發送讀地址 D3 (H),芯片確認。

- 芯片發送數據字節數 X,然后依次發送從起始字節 N 到 N + X - 1 的數據。

- 控制器對每個字節進行確認,最后發送不確認位和停止位。

此外,芯片還有多個寄存器用于配置不同的功能,如 Spread Spectrum Enable 和 CPU Frequency Select Register 用于控制擴頻和 CPU 頻率選擇,Output Control Register 用于控制各個時鐘輸出的啟用和禁用等。通過合理配置這些寄存器,可以實現芯片的個性化功能。

6. 電氣特性與性能指標

ICS951462 在不同的時鐘輸出上都有嚴格的電氣特性要求。

6.1 K8 推挽差分對

在 K8 推挽差分對輸出方面,上升沿和下降沿速率在 2 - 10V/ns 之間,差分電壓在 0.4 - 2.3V 之間,周期到周期抖動小于 85ps 等。這些特性確保了 K8 處理器時鐘信號的穩定性和準確性,為處理器的正常工作提供了保障。

6.2 HTTCLK 時鐘

HTTCLK 時鐘的長期精度在 ±300ppm 范圍內,33.33MHz 輸出的時鐘周期在 29.9910 - 30.0090ns 之間,66.67MHz 輸出的時鐘周期在 14.9955 - 15.0045ns 之間等。高精度的時鐘周期和長期精度能夠保證 HyperTransport 總線的高速穩定運行。

6.3 SRC/ATIG 0.7V 電流模式差分對

SRC/ATIG 0.7V 電流模式差分對的電壓高在 660 - 850mV 之間,電壓低在 -150 - 150mV 之間,長期精度在 ±300ppm 范圍內等。這些特性使得 SRC 和 ATIG 時鐘能夠滿足系統中相關組件的需求。

6.4 USB - 48MHz 和 REF - 14.318MHz 時鐘

USB - 48MHz 時鐘的長期精度在 ±100ppm 范圍內,REF - 14.318MHz 時鐘的長期精度在 ±300ppm 范圍內。高精度的時鐘可以確保 USB 設備和參考時鐘的穩定工作,提高系統的兼容性和可靠性。

7. 設計注意事項與建議

7.1 RESET_IN# 引腳操作

RESET_IN# 引腳的操作需要特別注意。當該引腳從高電平變為低電平時,所有輸出(除了 REF[2:0] 時鐘)將停止工作。REF 時鐘會在兩個時鐘周期后斷電并重新上電,SMBus 也會重新加載。整個過程中,時鐘恢復到正確頻率且無毛刺的時間不超過 2.5ms,而時鐘停止無毛刺的時間為 3μs。需要注意的是,當該引腳從低電平變為高電平時,對時鐘沒有影響。在實際設計中,要合理使用該引腳進行系統的復位操作,避免因誤操作導致系統故障。

7.2 SRC 路由信息

在進行 SRC 時鐘的路由設計時,要遵循一定的規則。例如,L1、L2、L3 長度應分別不超過 0.5 英寸、0.2 英寸、0.2 英寸,且應采用非耦合 50 歐姆走線。L4 長度在不同的路由方式(耦合微帶線和耦合帶狀線)下也有不同的要求,同時 Rs 和 Rt 的阻值分別為 33 歐姆和 49.9 歐姆。合理的路由設計可以減少信號干擾和衰減,提高時鐘信號的質量。

7.3 共享引腳操作

ICS951462 上的輸入/輸出(I/O)引腳具有雙重信號功能。在初始上電時,它們作為輸入引腳,將邏輯電平存儲到內部數據鎖存器中。上電復位結束后,這些引腳變為輸出引腳,為外部負載提供時鐘信號。為了對這些引腳進行編程,需要連接一個 10K 電阻到 VDD 或 GND。編程電阻應靠近串聯端接電阻放置,而串聯端接電阻應更靠近驅動器。這樣的設計可以確保在不同的工作模式下,引腳能夠正常工作,同時減少信號干擾。

綜上所述,ICS951462 是一款功能強大、性能出色的可編程系統時鐘芯片。它通過豐富的輸出特性、高精度的時鐘信號、靈活的編程功能以及嚴格的電氣特性要求,為基于 ATI RS/RD690 的系統提供了穩定可靠的時鐘解決方案。在實際設計中,工程師需要充分了解芯片的各項特性和設計注意事項,根據具體的應用需求進行合理的配置和設計,以發揮芯片的最佳性能。大家在使用這款芯片的過程中,有沒有遇到過一些獨特的問題或者有一些創新的應用呢?歡迎一起交流討論!

發布評論請先 登錄

怎么利用FPGA設計可編程電壓源系統?

可編程系統芯片的設計構架

可編程系統級芯片提供了最大設計的靈活性

在系統可編程模擬電路的原理與應用

采用FPGA的可編程電壓源系統原理及設計

可編程SoC(SoPC),什么是可編程SoC(SoPC)

新型系統級可編程芯片設計方案

可編程直流電源監控系統設計

ICS951462:ATi RS/RD690 系統的可編程系統時鐘芯片

ICS951462:ATi RS/RD690 系統的可編程系統時鐘芯片

評論