序言

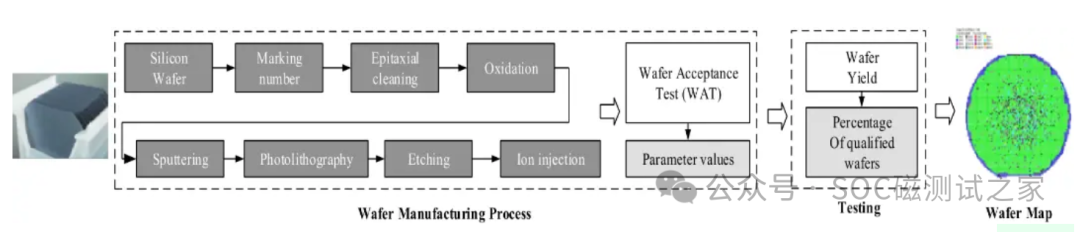

晶圓允收測試(WAT),也稱之為半導體參數測試(Parametric Test), 電測試(E-Test),或工藝控制監控(Process Control Monitor,PCM)。它是半導體制造的基石,可確保晶圓實現最高的質量、可靠性和性能標準。通過在晶圓上(通常在劃片線上)設計專門的測試結構,WAT能夠優化制造過程的質量控制,幫助晶圓廠提升良率、降低成本,并加速尖端技術的市場化進程。隨著半導體行業的持續發展,WAT在新工藝研發、工藝監控與生產維護、新產品導入、可靠性工程等方面發揮著關鍵作用。

01 晶圓允收測試(WAT)概述

晶圓允收測試(WAT)技術作為半導體制造過程控制的關鍵組成部分,其發展歷程可追溯至1978年。作為行業先驅,臺積電(TSMC)率先在該領域取得突破性進展,成功申請了"自動晶圓驗收測試方法"專利。隨著半導體制造工藝的不斷演進,TSMC于1997年進一步獲得"集成缺陷良率管理與查詢系統"專利,標志著WAT技術在半導體制造過程控制中的應用進入新的發展階段。

1.1 典型關鍵參數和測試結構

WAT(晶圓允收測試)的標準化實施方法是在晶圓上嵌入特殊測試結構,進行非破壞性測量。WAT測試主要針對晶圓的特定測試結構(Test Structure)中的器件,測量和獲取它們的電性能與物理參數,以確保晶圓符合設計規格和工藝要求。測試結構有時也稱之為測試鍵(Test Key),測試單元組(Test Element Group,TEG)等。測試結構中典型的待測器件包括:

用于測量薄膜電阻和接觸電阻。

旨在評估電容和介電完整性。

二極管 / PN結:

用于評估PN結的特性和漏電流。

提供關于關鍵晶體管參數的數據,例如 Ids 電流、閾值電壓和柵氧完整性。

視工藝研發或規模量產等的不同階段,測試結構和待測器件數量在晶圓上會有不同。比如在TD研發時,晶圓上每個Reticle內往往布滿測試結構;而在量產時,測試結構被設計在產品Die之間的劃片線位置,并均勻發布在不同位置(如中心和左右上下5個點),以助于識別制造過程中的空間變化。

Reticle上每個Die都布滿WAT測試結構

WAT測試結構分布在Die和Die之間的劃線道上

WAT測試結構中的待測器件示意圖

1.2 WAT局部差異和全局差異

WAT 數據必須區分局部差異(Local Variations )和全局差異(Global Variations)。通過分析這些差異,制造商可以找出缺陷的根本原因,并評估它們是否僅限于特定地區,或是否表明系統性問題。這種區分對于實施有針對性的過程優化和保持整個生產線的一致性至關重要。

*局部差異

局部變化是指在單個晶圓或小區域內的差異。這些差異可能源于光刻或蝕刻的不一致性。局部差異在先進技術中尤為關鍵,因為即使是微小的偏差也會對設備性能產生重大影響。

*全局差異

全局差異指的是晶圓與晶圓之間或批次與批次之間的數據差異。這些差異可以識別設備漂移或工藝不穩定性。

02 WAT重要性

作為半導體制造過程控制的核心工具之一,WAT測試始終保持著其不可替代的重要地位,在確保芯片良率和提升制程穩定性方面發揮著關鍵作用。

WAT測試能夠獲取數據來監控和驗證制造過程的穩定性,成為過程控制監測(PCM)體系中的重要一環,為生產質量的提升提供支持。WAT數據由晶圓制造廠(FAB)在制造過程結束時生成,作為對晶圓的初始測量,旨在確認其在制造過程中的結構完整性。由于數據量有限,評估和分析PCM具有挑戰性,但WAT數據卻是預測后續工藝可能出現問題或故障的重要工具。因此,WAT不僅是生產中的PCM工具,也是工程師在新產品開發過程中最重要的工具之一,廣泛的工程WAT測試結構有助于識別影響產量和操作效率低下的故障和問題。

通常情況下,Fabless(無晶圓廠客戶)能夠獲取每個出廠晶圓的生產WAT數據,這對于確保半導體制造工藝的一致性至關重要,旨在避免因良品率低下而導致重大收益的損失。

標有WAT待測器件位置的晶圓圖

03 WAT測試手段

3.1 WAT測試機

WAT測試需要使用各種不同測試資源,進行電流與電壓(IV)和電容與電壓(CV)等方面的測量。這些測試資源或者儀器通常包括源/測量單元(SMU)、精密數字電壓表(DMM)、脈沖發生器(PGU)和電容表(LCR)等。所有的測試資源將通過一個開關矩陣 (低壓低漏電開關矩陣,或者針對功率半導體的高壓開關矩陣) 連接到晶圓上每個測試結構的測試點,使用探針卡與探針進行接觸,完成對待測器件(MOSFET,電阻,電容等)的電測試。上述測試資源與儀器,由WAT測試系統軟件進行管理和控制,結合測試頭、結構件等部件,共同構成了完整的WAT測試系統。

下圖是聯訊高壓WAT測試系統的示意圖:

WAT測試機示意圖

3.2 WAT測試挑戰

首先是低電流測量,由于電纜絕緣的電容效應,需要更長的穩定時間。特別是在測試過程中需要對電壓進行掃描時,這種寄生電容會引發充電電流,從而影響測量精度。

其次,隨著碳化硅(SiC)等寬帶隙器件的廣泛應用,對測試設備提出了新的要求,包括需要高壓SMU,高壓開關矩陣等新型測試資源。

最后,先進工藝將需要新型的測試結構,如陣列測試(Array Test),以布置數量眾多的待測器件來獲取各種參數數據,深入獲知Intra-Reticle的局部差異。由于傳統的串行WAT測試機架構陳舊、測試效率低下等缺點,已無法滿足Array Test的需求。行業勢必需要新型測試方法以及高效率的并行WAT測試機。

陣列測試結構

04 結論

WAT(晶圓允收測試)是晶圓制造過程中至關重要的過程控制監測(PCM)工具,在半導體產品質量和良率方面發揮著決定性作用。它能夠提供局部(晶圓特定)和全局(晶圓到批次或批次到批次)的統計數據,為制造過程的優化提供關鍵支持。

未來的發展方向將聚焦于更復雜的測試陣列設計和并行測試能力的提升,以進一步縮短測試時間并降低成本。

-

半導體

+關注

關注

339文章

30829瀏覽量

264795 -

晶圓

+關注

關注

53文章

5419瀏覽量

132380

發布評論請先 登錄

晶圓接受測試的具體內容與重要作用

晶圓制造中的WAT測試介紹

半導體WAT測試的常見結構

晶圓清洗設備概述

晶圓接受測試中的閾值電壓測試原理

晶圓允收測試 (WAT)概述

晶圓允收測試 (WAT)概述

評論