MCU芯片是產品開發過程中的核心器件——選型得當,后續開發順理成章;否則從功耗測試到量產交付,處處都是填不完的坑。

近期,擁有十余年德州儀器(TI)芯片設計經驗的資深工程師John Teel,在Youtube上發布視頻,結合其行業閱歷,深度剖析了工程師在MCU芯片選型時最易踩中的十大隱性陷阱。

圖/Youtube截圖

《半導體器件應用網》對John Teel的觀點進行了梳理整理,希望能幫助工程師與工程師團隊避開MCU芯片選型中的隱形陷阱。

一、產品開發規劃期:MCU頂層架構的缺失

許多工程師團隊急于推進項目,往往在頂層架構尚未明朗時便倉促敲定MCU芯片型號,這種工程師團隊的短視行為常引發后續MCU芯片開發中的連鎖問題。

誤區1:受制于MCU開發慣性,先定芯片再看架構

工程師團隊們常因熟悉某款芯片或評估板而優先選定MCU,再圍繞其展開工程設計。這導致電源劃分、總線分配、休眠邏輯等均需妥協適配,微小的技術妥協將隨開發進程不斷放大,最終導致硬件系統異常臃腫。工程師的正確路徑應是系統架構先行:厘清整機供電、實時性與吞吐量后,再篩選能完美支撐的MCU。

誤區2:在MCU芯片“成本平衡”與“冗余堆料”間失去焦點

評估I/O與存儲資源時,MCU芯片選型易陷入兩個極端:一是工程師團隊過度追求成本控制,資源算得剛剛好,產品迭代時稍有增加便打破平衡,被迫引入擴展芯片或復雜邏輯;二是工程師盲目堆料,選用集成繁雜外設的高階MCU芯片,閑置硅片區域不僅抬高BOM成本,其漏電流還損耗系統能效。合理選型應在精準滿足需求基礎上,預留20%擴展空間。

誤區3:陷入MCU芯片“唯高主頻論”隱形陷阱

“主頻越高越穩定”是MCU選型的常見誤區。但根據全球半導體巨頭ADI(亞德諾)發布的應用數據指出:典型的電池供電物聯網(IoT)傳感器節點,其工作占空比通常僅在0.01%到1%之間。這意味著,設備在其生命周期中超過99%的時間都處于極低功耗的休眠模式。

工程師團隊為不到1%的低頻交互任務配備高性能內核,不僅顯著提高了電源管理IC的設計門檻和熱設計難度,更會在潛移默化中導致固件代碼質量劣化。當算力資源顯得取之不盡時,工程師往往會忽視對循環執行效率及中斷響應時序的精細化優化。直至整機功耗測試暴露出嚴重短板時,那些深植于底層架構的低效邏輯已然積重難返。

圖/AI生成

架構階段的隱患一旦帶入實質性的研發周期,真正的軟硬協同挑戰才剛剛拉開帷幕。

二、底層研發期:MCU軟硬協同的“暗礁”

進入軟硬件聯合調試階段后,早期看似無關痛癢的MCU選型妥協,會逐漸演化為拖延研發周期的工程師的主要障礙。

誤區4:唯工具論,讓MCU開發便利性凌駕于物理約束

工程師通常更青睞生態完善的開發平臺——例如具備成熟的HAL(硬件抽象層)庫或可一鍵生成初始化代碼的IDE。因為這能使得工程師團隊有效縮短早期驗證周期。但開發便利性可能掩蓋了芯片的物理短板,一款軟件體驗極佳的MCU,可能在射頻底噪、待機功耗或寬溫域穩定性上存在先天缺陷。此類隱患在實驗室往往難以發現,卻會進入嚴苛的高低溫或者復雜電磁環境測試后暴露,最終工程師只能以軟件復雜性彌補硬件缺陷。

誤區5:忽視MCU芯片開發生態,陷入孤島式排障的泥潭

部分冷門MCU技術手冊上的參數規格競爭力強且富有性價比,但工程師實際開發后卻生態劣勢盡顯:工具鏈不穩定、數據手冊含糊、寄存器定義不明。遇到底層異常時,社區支持缺失,開發者難以判斷問題是源于代碼、編譯器,還是芯片本身的缺陷。硬件延期往往源于這種孤島式排查困境。

誤區6:MCU芯片存儲資源盲目樂觀,缺乏對動態資源的預先建模

工程師在初期驗證固件時僅運行核心邏輯,這使得Flash與RAM看似充裕。但隨著加密、OTA、RTOS等模塊加入,存儲資源迅速消耗。內存枯竭不報錯,而表現為系統隨機崩潰。此時工程師便只能被迫削減功能、重構代碼或換大容量MCU重新排產。

誤區7:忽視MCU芯片全鏈路功耗追蹤:系統級漏電的歸因困境

續航是產品的核心指標之一,功耗超標多為系統性失誤:固件未關閑置時鐘、硬件GPIO浮空漏電、無線模塊握手產生尖峰電流。盡管芯片的技術手冊中詳細標注了各種卓越的深度休眠模式,但其能否在實際產品中兌現,完全取決于立項初期對時鐘分配、喚醒源機制的精細統籌。若試圖在硬件定型后再進行“純軟件層面的功耗優化”,工程師會發現大多數可優化的路徑已被底層硬件架構徹底封死。

圖/AI生成

工程師團隊歷經嚴苛的聯合調試,當技術指標終于達成時,產品想要從實驗室步入規模化量產及售后維護,工程師團隊仍需跨越最后三道生死關卡。

三、量產與生命周期:MCU從實驗室到市場的最后三道關卡

在商業化硬件產品的演進中,工程師將代碼調通、功能實現僅是第一步。若工程師在選型階段缺乏全生命周期的前瞻性視野,產品在量產與市場投放階段將面臨最為嚴厲的反噬。

誤區8:工程師團隊無視OTA升級規劃,使產品喪失迭代能力

智能化時代,出廠即固化、不具備后續升級能力的產品已難以適應市場需求。國際權威學術期刊《IEEE軟件工程匯刊》曾發表過一項針對全球超100萬臺聯網IoT設備的大規模實證分析。數據顯示:在實際部署的設備中,僅有約2.45%運行著最新版本的固件,而設備平均搭載的固件版本已經過時老舊長達19.2個月。

圖/IEEE截圖

導致這一現象的核心原因之一,正是工程師團隊在選型初期未將固件演進機制納入考量。對于需要提供網絡連接的設備而言,支持安全的OTA(空中下載技術)雙分區回滾機制,通常意味著需要配置至少兩倍于當前固件體積的Flash空間。若未在硬件層面預留充足的存儲冗余,或者對于非聯網設備未規劃便捷的有線升級接口,一旦首批投放市場的產品暴露出嚴重的底層缺陷,那對于整個產品的影響將是災難級的。

誤區9:工程師團隊低估EMC與射頻合規壁壘

在EMC(電磁兼容性)半電波暗室中,硬件工程師常常會面臨產品與實驗室環境表現嚴重不符的困境。這絕非個例,根據國際權威測試與認證機構Intertek在其發布的白皮書中披露的統計數據:高達50%的電子產品在首次提交EMC測試時遭遇失敗。

MCU內部的時鐘倍頻、晶振電路布局及I/O驅動配置,本身就是輻射源。若工程師心存僥幸應對EMC測試,往往換來一份輻射發射(RE)嚴重超標的報告。實驗室里的貼銅箔、換磁珠只是權宜之計,治標不治本。為了通過FCC/CE認證,PCB往往被迫推倒重來。工程師前期省下的那點主控成本,最終將變成數十萬的認證整改費用,外加錯失數月的市場窗口。

誤區10:工程師團隊無視供應鏈預判:生命周期管理的缺失

將這一誤區置于十大誤區之末,是因為該因素對項目的打擊往往是毀滅性的。

當工程師研發歷經數月攻堅,產品性能達標、各項國際認證順利通過,市場營銷已全面鋪開、量產指令即將下達。此時供應鏈端卻反饋:核心MCU面臨全球性缺貨,交貨周期長達52周,甚至原廠已發布該MCU型號的停產通知。

在供應鏈的波動面前,若被迫更換替代MCU,意味著需要重新設計原理圖及PCB、耗費大量時間重構固件驅動層,并重新執行所有嚴苛的可靠性測試與合規認證。

圖/AI生成

當下MCU早已不是單純的控制芯片,其選型實際是系統架構、軟件工程、電磁兼容、供應鏈研判的多維博弈。

上述這10個隱形陷阱,看似只是經驗之談,實則是工程師無數項目用真金白銀換來的教訓,選對一顆MCU,項目就成功了一半。希望這篇文章,能夠幫各位工程師朋友們省下那一半的試錯成本。

各位工程師們,您在開發產品的實踐過程中,是否曾因MCU選型失誤而面臨嚴峻的項目挑戰?歡迎在評論區分享您的工程實踐經驗。

本文為嗶哥嗶特資訊原創文章,未經允許和授權,不得轉載,

審核編輯 黃宇

-

mcu

+關注

關注

147文章

19044瀏覽量

401684 -

功耗測試

+關注

關注

0文章

20瀏覽量

9799

發布評論請先 登錄

射頻選型“翻車”現場:一文看懂SMA與RP-SMA在企業應用中的隱形陷阱

室外光纜線:室外通信的“隱形動脈”

車載功放芯片選型指南——CD7377CZ/CD7388核心參數解析與實測對比

新購設備選不對?AI 選型系統算 20 年成本,不花冤枉錢

MCU選型晉級思維:安全為基石,可升級為動脈,生態防鎖定

不止于性能:MCU選型中那些“四兩撥千斤”的關鍵外設

N32 MCU IO 5V 耐壓選型指南

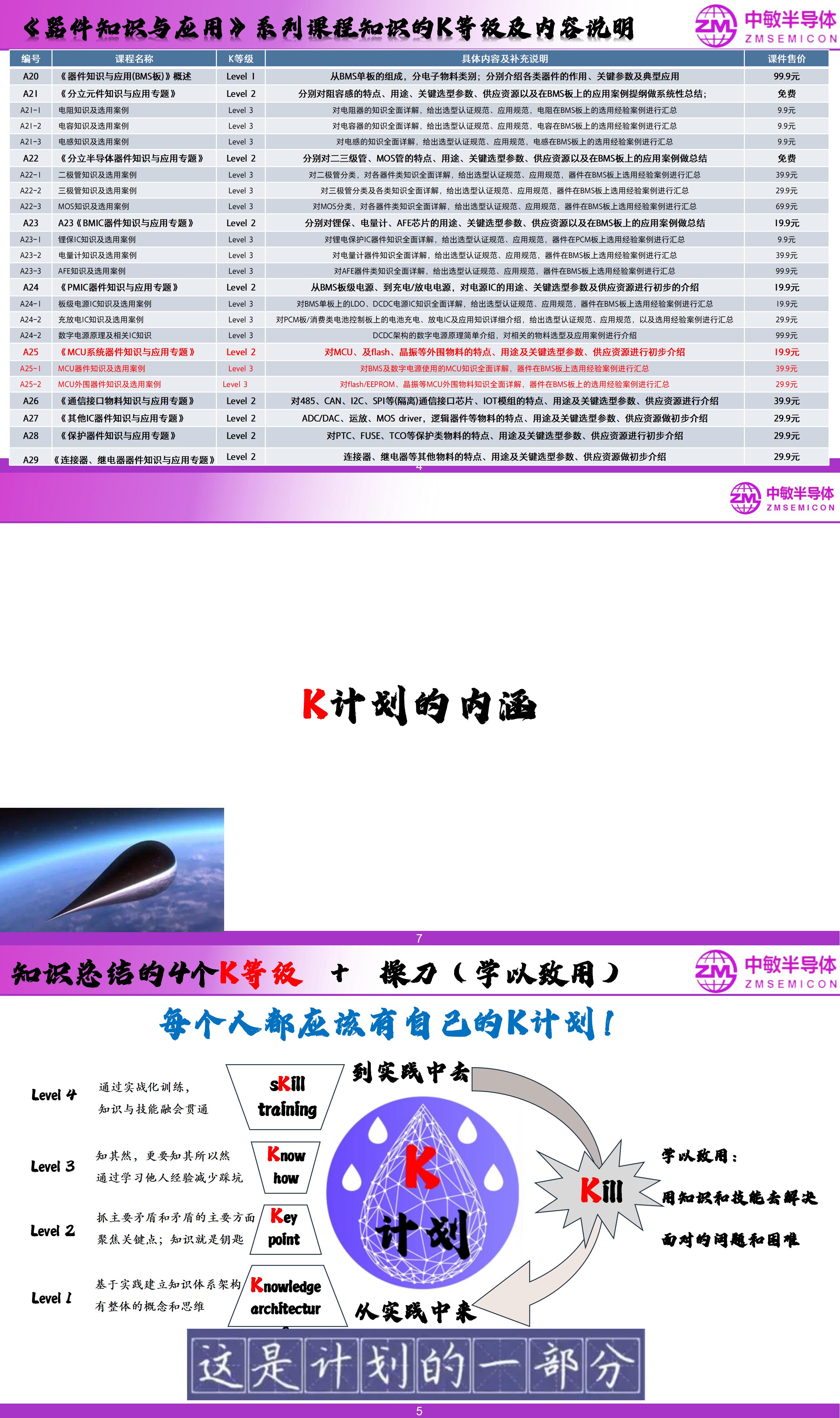

A25:MCU系統器件知識與應用專題--MCU、EEPROM/FLASH和晶體/晶振知識及應用案例

雷達遙感星座微波射頻組件抗輻照MCU的選型與實踐

晶振選型三大陷阱:工作溫度、電壓與負載電容的隱藏矛盾

靈動微電子MM32MCU的主流型芯片選型

MCU選型的10大隱形陷阱

MCU選型的10大隱形陷阱

評論