本博文主要交流設(shè)計(jì)思路,在本博客已給出相關(guān)博文約170篇,希望對初學(xué)者有用。注意這里只是拋磚引玉,切莫認(rèn)為參考這就可以完成商用IP設(shè)計(jì)。

RoCE v2原語

它是RoCE v2協(xié)議進(jìn)行信息及數(shù)據(jù)交換的核心機(jī)制,也是DUT需要實(shí)現(xiàn)的核心機(jī)制之一,對該功能的仿真驗(yàn)證需要考慮指令的提交數(shù)據(jù)包的組裝及發(fā)送、數(shù)據(jù)的DMA處理等。RoCE v2原語功能驗(yàn)證的測試項(xiàng)與測試步驟如表1所示。

表1 RoCE v2原語功能驗(yàn)證測試項(xiàng)與測試步驟

(1)指令提交驗(yàn)證

測試步驟 1 的關(guān)鍵波形如圖 1 所示,寫入指令控制寄存器之后,指令控制模塊自動將信息組裝為提交隊(duì)列條目寫入提交隊(duì)列,返回的指令狀態(tài)為 0x1f 表示指令已被正確寫入,存儲的數(shù)據(jù)如圖2 所示,符合設(shè)計(jì)預(yù)期,驗(yàn)證通過。

圖1 指令組裝及存儲仿真波形圖

圖2 提交隊(duì)列存儲數(shù)據(jù)圖

B站已給出相關(guān)性能的視頻,如想進(jìn)一步了解,請搜索B站用戶:專注與守望

https://www.bilibili.com/video/BV1mPV5eCE8z/?spm_id_from=333.337.search-card.all.click&vd_source=c355545d27a44fe96188b7caefeda6e7

審核編輯 黃宇

-

RDMA

+關(guān)注

關(guān)注

0文章

100瀏覽量

9651

發(fā)布評論請先 登錄

RDMA設(shè)計(jì)50: 如何驗(yàn)證網(wǎng)絡(luò)嗅探功能?

RDMA設(shè)計(jì)48:雙邊語義驗(yàn)證2

RDMA設(shè)計(jì)46:RoCE v2原語功能:單邊語義

RDMA設(shè)計(jì)45:RoCE v2 原語功能驗(yàn)證與分析2

RDMA設(shè)計(jì)37:RoCE v2 子系統(tǒng)模型設(shè)計(jì)

RDMA設(shè)計(jì)35:基于 SV 的驗(yàn)證平臺

RDMA設(shè)計(jì)29:RoCE v2 發(fā)送及接收模塊設(shè)計(jì)2

RDMA設(shè)計(jì)28:RoCE v2 發(fā)送及接收模塊設(shè)計(jì)

RDMA設(shè)計(jì)19:RoCE v2 發(fā)送及接收模塊設(shè)計(jì)

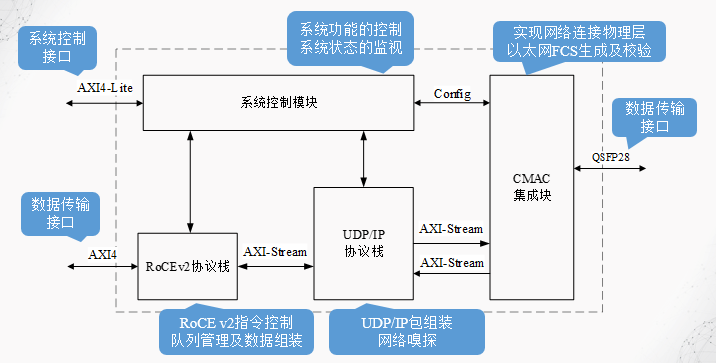

RDMA設(shè)計(jì)5:RoCE V2 IP架構(gòu)

RDMA over RoCE V2設(shè)計(jì)2:ip 整體設(shè)計(jì)考慮

RDMA over RoCE V2設(shè)計(jì)2:ip 整體框架設(shè)計(jì)考慮

RDMA over RoCE V2設(shè)計(jì)1:為什么要設(shè)計(jì)它?

RDMA設(shè)計(jì)44:RoCE v2原語功能驗(yàn)證與分析

RDMA設(shè)計(jì)44:RoCE v2原語功能驗(yàn)證與分析

評論