在嵌入式Linux產品開發中,U-Boot SPL啟動崩潰、主板不上電、啟動卡死在初始化階段是最讓人頭疼的硬故障之一。日志亂碼、CPU異常復位、看不到完整啟動流程,往往讓軟件工程師誤以為是代碼BUG,硬件工程師無從下手。

本文結合真實量產故障案例,通過兩段串聯的啟動日志,從SPL異常崩潰,到底層DDR自檢報錯,一步步抽絲剝繭,鎖定終極根因,給出可直接落地的排查方案,堪稱RK平臺啟動故障的“教科書級排障”。

一、故障現場:主板啟動失敗,兩段詭異日志

本次故障主板為瑞芯微RK系列平臺,現象為:上電后無法啟動,串口不停打印異常信息,反復自動復位,完全無法進入U-Boot與系統。

我們抓取到兩段關鍵日志,也是本次排障的核心依據。

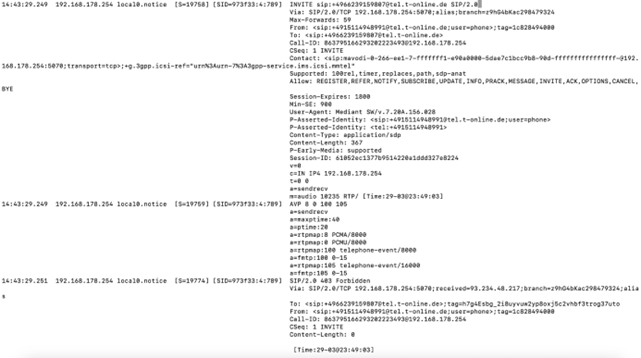

日志1:U-Boot SPL崩潰,CPU異常復位

主板上電初期,U-Boot SPL 2017.09運行至板級初始化后,直接觸發CPU硬件異常,打印大量無效寄存器、棧信息,隨后強制提示復位。

U-Boot SPL2017.09U-Boot SPL boardinitSynchronous abort handler......Call trace:......ERROR: Please RESET the board

初步表象:SPL跑飛、數據中止異常、棧無效、CPU訪問非法地址,多數開發者第一反應會懷疑:U-Boot配置錯誤、編譯問題、鏡像燒錄異常、軟件棧配置錯誤。

但僅憑這段日志,只能確定內存訪問非法,無法定位是軟件還是硬件問題。

日志2:DDR底層自檢報錯,暴露致命硬件問題

在開啟芯片底層DDR自檢模式后,出現了更關鍵、更直白的報錯,這也是解開整個故障的鑰匙:

DDRdfs8434ice typ24/09/86-09:51:11,fwver v1.18unknowndeviceIfno 'may be ch* soldering abnormality' is printed, it may be ch0 soldering abnormalitypd/nu vdd ddrunknowndeviceERROR

這段日志來自RK平臺最底層的DDR PHY自檢程序,優先級高于U-Boot SPL,它的報錯,直接宣判了故障性質。

二、逐句拆解:DDR自檢日志,每一句都是硬件結論

很多工程師看到這段自檢日志,只知道“報錯了”,卻讀不懂背后的硬件含義,我們逐行翻譯:

1.dfs8434ice:瑞芯微平臺專用DDR控制器與PHY標識,說明系統已經運行到DDR硬件初始化訓練階段,還未進入U-Boot主邏輯。

2.unknown device:DDR控制器完全讀取不到DDR顆粒的ID、型號、寄存器信息,DDR芯片與主控之間通信徹底中斷,芯片處于“不在線”狀態。

3.ch0 soldering abnormality:日志明確提示,未檢測到其他通道故障時,默認判定為DDR通道0(CH0)焊接/硬件通路異常。

4.pd/nu vdd ddr:核心致命報錯!pd = power down(掉電),nu = not up(未上電),翻譯為:DDR核心供電VDD_DDR無電壓、供電失效、電源未啟動。

5.最終ERROR:DDR識別失敗、供電異常、通路故障,自檢不通過,啟動終止。

三、雙日志聯動:因果閉環,根因100%鎖定

把兩段日志結合,故障的完整因果鏈瞬間清晰,不再有任何歧義:

完整故障流程

1.主板上電,CPU啟動,運行最底層DDR自檢;

2.DDR核心供電VDD_DDR失效/ DDR CH0虛焊/斷線,導致DDR顆粒完全不工作;

3.自檢程序識別不到DDR,拋出unknown device與pd/nu vdd ddr錯誤;

4.系統繼續運行U-Boot SPL,SPL默認將棧、運行內存指向外部DDR;

5.CPU訪問未初始化、無供電、無硬件響應的非法DDR地址,觸發數據中止異常;

6.SPL崩潰、跑飛、打印無效棧與寄存器,最終強制復位,循環卡死。

終極結論

先有DDR硬件致命故障,后有SPL軟件崩潰。

?SPL的異常日志,是故障結果;

?DDR自檢的報錯日志,是故障根源。

本次故障與U-Boot配置、編譯、鏡像燒錄、軟件參數無關,純硬件電路問題,也是RK平臺量產階段最高發的故障類型。

四、優先級排查方案:從最高概率到最低,一步定位

結合瑞芯微平臺量產經驗,此類故障按以下順序排查,95%的問題在前兩步即可解決。

第一步:測量DDR供電(第一優先級,概率60%+)

日志直接打印pd/nu vdd ddr,說明供電是首要懷疑對象。

使用萬用表實測DDR三大關鍵電源:

?VDD_DDR(核心供電):標準1.1V/1.2V,出現0V、電壓偏低、紋波過大,直接判定電源故障;

?VDDQ_DDR(IO供電):標準1.8V(LPDDR為低電壓),IO斷電會直接導致總線通信失效;

?PMIC/DC-DC電源芯片:檢查是否發燙、使能腳無電平、電感虛焊、濾波電容短路。

只要供電異常,修復電源后故障立即消失,無需排查其他。

第二步:檢查DDR CH0焊接與硬件通路(概率35%)

日志明確指向ch0 soldering abnormality,BGA封裝的DDR顆粒虛焊、冷焊、連錫是量產重災區:

1.目視檢查DDR顆粒是否鼓包、掉件、周邊阻容脫落;

2.熱風槍重焊DDR,優先重新植球處理;

3.萬用表打值CH0通道DQ/CA/時鐘線,排查短路、斷線;

4.替換同型號完好DDR顆粒,排除芯片本身損壞。

第三步:軟件參數兜底(概率<5%,僅硬件完好后驗證)

只有硬件完全正常,才需要檢查軟件配置:

1.確認DDR型號(DDR3/DDR4/LPDDR4X)與設備樹、SPL配置匹配;

2.使用瑞芯微官方工具重新生成DDR參數(ddrbin);

3.恢復原廠默認U-Boot配置,不做自定義時序修改。

五、實戰總結:嵌入式啟動故障的3條鐵律

通過本次排障,我們可以總結出適用于全平臺的嵌入式啟動故障判斷原則,尤其適合RK/全志/STM32等ARM平臺:

1.只要SPL崩潰、棧無效、數據中止,優先懷疑DDR,而非軟件

U-Boot SPL的核心工作就是初始化DDR,絕大多數崩潰都來自內存訪問非法,軟件BUG概率遠低于硬件。

2.底層硬件自檢日志> U-Boot日志,優先級更高、更可信

DDR PHY、時鐘、電源自檢程序,運行優先級遠高于U-Boot,它的報錯是硬件底層直讀結果,比系統日志更準確。

3.“unknown device +供電報錯+通道異常”,直接判定硬件死穴

只要出現DDR無法識別、供電掉電、通道焊接提示,100%是硬件問題,不要再浪費時間調試軟件、重新編譯、反復燒錄鏡像。

嵌入式開發中,80%的啟動卡死,都源于最基礎的電源與焊接問題。很多時候,復雜的異常日志背后,往往是最簡單的硬件故障。

讀懂底層日志,理清因果邏輯,先硬件后軟件,先供電后信號,才能少走彎路,高效排障。

如果你也在做RK平臺開發,遇到U-Boot崩潰、DDR訓練失敗、啟動不上電,不妨對照本文的日志與排查思路,快速定位你的硬件問題。

-

嵌入式

+關注

關注

5202文章

20516瀏覽量

335053 -

DDR

+關注

關注

11文章

756瀏覽量

69236 -

Linux

+關注

關注

88文章

11778瀏覽量

219198

發布評論請先 登錄

分布式日志追蹤ID實戰

深度解析SPL階段A/B分區啟動:spl_ab.c代碼全拆解

ucgui listbox顯示不全 只有兩行

HarmonyOS 崩潰服務能力全新上線!幫你高效解決崩潰問題

如何跳過SPL中的ddr訓練?

iMotions為生物識別平臺啟動新型在線用戶數據收集方案

VoIP?網絡排障新思路:從日志到 IOTA?分析

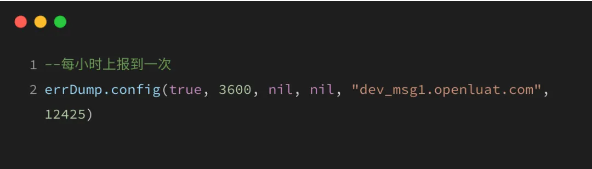

遠程日志errDump調試功能實戰教程:案例驅動的故障排查!

RK?平臺?DDR?測試終極指南:標準化步驟?+?全場景適配方案

Linux內核日志玩明白了嗎?printk調試神器全解析

實戰排障|RK平臺啟動卡死、SPL崩潰,兩行日志直接定位DDR硬件死穴!

實戰排障|RK平臺啟動卡死、SPL崩潰,兩行日志直接定位DDR硬件死穴!

評論