CDCP1803:高性能1:3 LVPECL時(shí)鐘緩沖器的設(shè)計(jì)指南

在電子設(shè)計(jì)領(lǐng)域,時(shí)鐘信號的精確分配至關(guān)重要,它直接影響著整個(gè)系統(tǒng)的性能和穩(wěn)定性。TI公司的CDCP1803時(shí)鐘驅(qū)動(dòng)器,作為一款專為時(shí)鐘分配優(yōu)化的器件,以其出色的特性和靈活的配置,成為眾多工程師的首選。本文將深入剖析CDCP1803的技術(shù)細(xì)節(jié)、應(yīng)用要點(diǎn)以及設(shè)計(jì)注意事項(xiàng),幫助工程師們更好地利用這款器件。

文件下載:cdcp1803.pdf

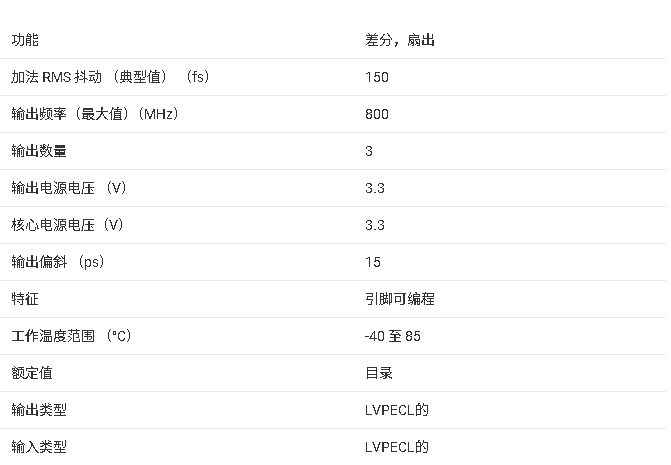

一、關(guān)鍵特性速覽

1. 信號分配與輸出

CDCP1803能夠?qū)⒁宦凡罘謺r(shí)鐘輸入信號分配到三路LVPECL差分時(shí)鐘輸出,并且為其中兩路LVPECL輸出提供可編程的分頻功能。這一特性使得它在不同時(shí)鐘頻率需求的系統(tǒng)中具有很強(qiáng)的適應(yīng)性。

2. 低輸出偏斜

其典型輸出偏斜僅為15ps,確保了時(shí)鐘信號在分配過程中的同步性,減少了因信號延遲差異而導(dǎo)致的系統(tǒng)誤差。

3. 寬工作電壓范圍

工作電壓范圍為3V - 3.6V,能夠適應(yīng)多種電源環(huán)境,增加了器件的通用性。

4. 高速信號處理

支持高達(dá)800MHz的LVPECL信號速率,滿足高速系統(tǒng)的時(shí)鐘需求。

5. 廣泛的信號兼容性

差分輸入級具有較寬的共模范圍,能夠接受LVDS、HSTL、CML、VML、SSTL - 2等多種差分信號,以及LVTTL/LVCMOS單端信號,方便與不同類型的信號源連接。

6. 偏置電壓輸出

提供VBB偏置電壓輸出,可作為單端輸入信號的共模電壓參考,簡化了單端驅(qū)動(dòng)應(yīng)用的設(shè)計(jì)。

二、引腳功能詳解

1. 使能引腳(EN)

用于同時(shí)啟用或禁用所有輸出。當(dāng)EN = 1時(shí),輸出根據(jù)S[2:0]的設(shè)置開啟;當(dāng)EN = 0時(shí),輸出Y[2:0]處于高阻抗?fàn)顟B(tài)。

2. 差分輸入引腳(IN, IN)

差分輸入時(shí)鐘,輸入級靈敏度高且共模范圍寬。建議在輸入前對PCB傳輸線進(jìn)行端接,如使用100Ω跨接輸入。也可以使用單端信號驅(qū)動(dòng),此時(shí)互補(bǔ)輸入應(yīng)連接到VBB。

3. 模式選擇引腳(S[2:0])

用于選擇不同的工作模式,定義了Y[2:0]的輸出配置。

4. 偏置電壓輸出引腳(VBB)

輸出電壓為VDD – 1.3V,可用于為單端輸入信號的未使用互補(bǔ)輸入IN提供偏置。驅(qū)動(dòng)負(fù)載時(shí),輸出電流限制在約1.5mA。

5. 電源引腳

VDDPECL為PECL輸入和內(nèi)部邏輯提供電源,VDD[2:0]為輸出Y[2:0]提供PECL輸出電源電壓。每個(gè)輸出可以通過將相應(yīng)的VDDx拉至GND來禁用。

三、工作模式配置

CDCP1803通過三個(gè)控制端子(S0, S1, S2)和一個(gè)使能端子(EN)來選擇不同的輸出模式。具體的模式配置可以參考文檔中的表1,工程師們可以根據(jù)實(shí)際需求靈活設(shè)置這些引腳,以實(shí)現(xiàn)不同的輸出分頻和開關(guān)控制。

四、電氣特性分析

1. 輸入特性

輸入頻率范圍為0 - 800MHz,輸入電壓擺幅在500 - 1300mV之間,輸入阻抗為300kΩ,輸入電容為1pF。這些特性確保了器件能夠準(zhǔn)確地接收各種類型的時(shí)鐘信號。

2. 輸出特性

輸出頻率最高可達(dá)800MHz,輸出電壓擺幅在500mV以上,輸出偏斜典型值為15ps,上升和下降時(shí)間在200 - 350ps之間。這些參數(shù)保證了輸出時(shí)鐘信號的質(zhì)量和穩(wěn)定性。

3. 抖動(dòng)特性

在不同的頻率范圍和分頻模式下,器件的附加相位抖動(dòng)較小,例如在12kHz - 20MHz、fout = 250MHz - 800MHz、1分頻模式下,抖動(dòng)典型值為0.15ps rms。

五、熱設(shè)計(jì)要點(diǎn)

CDCP1803采用24引腳QFN封裝,為了確保良好的散熱性能,PCB設(shè)計(jì)時(shí)需要特別注意。建議使用四層JEDEC測試板,并在PCB中設(shè)置四個(gè)直徑為22mil的熱過孔,將封裝的散熱焊盤與PCB有效連接,以保證良好的散熱效果。通過合理的熱設(shè)計(jì),可以降低器件的結(jié)溫,提高其可靠性和穩(wěn)定性。

六、應(yīng)用設(shè)計(jì)建議

1. 輸入終端匹配

對于LVPECL輸入,推薦使用100Ω電阻跨接輸入端子進(jìn)行端接,或者使用2 × 50Ω電阻,中心抽頭連接電容以抑制奇模噪聲和補(bǔ)償傳輸線失配。VBB輸出也可以連接到中心抽頭,為輸入信號提供偏置。

2. 單端信號驅(qū)動(dòng)

當(dāng)使用單端信號驅(qū)動(dòng)時(shí),輸入信號連接到一個(gè)輸入,互補(bǔ)輸入應(yīng)正確偏置到輸入信號的中心電壓。對于LVCMOS信號,可以使用簡單的電壓分壓器實(shí)現(xiàn)。更好的方法是對輸入信號進(jìn)行交流耦合,然后使用VBB參考輸出重新偏置信號。

3. 復(fù)位和控制端子切換

在設(shè)備使能(EN = 0 → 1)時(shí),輸出驅(qū)動(dòng)會經(jīng)歷一個(gè)短暫的高信號狀態(tài),然后進(jìn)入低狀態(tài)。在啟用單個(gè)輸出級時(shí),輸出狀態(tài)會在第一個(gè)正時(shí)鐘過渡后變得有效。

七、總結(jié)

CDCP1803是一款功能強(qiáng)大、性能出色的時(shí)鐘緩沖器,具有廣泛的信號兼容性、低輸出偏斜和高速信號處理能力。通過合理的引腳配置、電氣特性分析和熱設(shè)計(jì),工程師們可以充分發(fā)揮其優(yōu)勢,滿足各種復(fù)雜系統(tǒng)的時(shí)鐘分配需求。在實(shí)際應(yīng)用中,還需要根據(jù)具體的設(shè)計(jì)要求和系統(tǒng)環(huán)境,靈活調(diào)整設(shè)計(jì)方案,確保系統(tǒng)的穩(wěn)定性和可靠性。你在使用CDCP1803的過程中遇到過哪些問題呢?歡迎在評論區(qū)分享你的經(jīng)驗(yàn)和見解。

-

時(shí)鐘緩沖器

+關(guān)注

關(guān)注

2文章

270瀏覽量

51910 -

設(shè)計(jì)指南

+關(guān)注

關(guān)注

0文章

254瀏覽量

8932

發(fā)布評論請先 登錄

DAC3482用CDCE62005做時(shí)鐘發(fā)生器,產(chǎn)生的FIFO-OSTR又經(jīng)過了時(shí)鐘緩沖器CDCP1803,CDCP1803的作用是什么?

DAC3482從時(shí)鐘發(fā)生器出來的FIFO_OSTR信號連入時(shí)鐘緩沖器CDCP1803后才輸出到DA中,時(shí)鐘緩沖器起什么作用?

1:3 LVPECL時(shí)鐘緩沖器CDCP1803數(shù)據(jù)表

CDCLVP2108 16路LVPECL輸出高性能時(shí)鐘緩沖器數(shù)據(jù)表

CDCLVP2102四路LVPECL輸出高性能時(shí)鐘緩沖器數(shù)據(jù)表

16路LVPECL輸出、高性能時(shí)鐘緩沖器CDCLVP1216數(shù)據(jù)表

CDCLVP2106 12路LVPECL輸出高性能時(shí)鐘緩沖器數(shù)據(jù)表

CDCLVP1204四路LVPECL輸出高性能時(shí)鐘緩沖器數(shù)據(jù)表

CDCLVP1102雙路LVPECL輸出高性能時(shí)鐘緩沖器數(shù)據(jù)表

HACP1204QN型低抖動(dòng)LVPECL時(shí)鐘緩沖器

?CDCP1803 1:3 LVPECL時(shí)鐘緩沖器技術(shù)文檔總結(jié)

CDCP1803:高性能1:3 LVPECL時(shí)鐘緩沖器的設(shè)計(jì)指南

CDCP1803:高性能1:3 LVPECL時(shí)鐘緩沖器的設(shè)計(jì)指南

評論