當儲能系統在瞬時大電流輸出與長壽命之間舉棋難定,你是否也在尋求更精準的放電與均衡方案?在多只串聯超級電容的高壓架構中,靈活可編程的FPGA控制平臺正為恒流放電和電壓均衡帶來可靠解法。

一、背景與挑戰

- 串聯差異:同一型號超級電容在容量、內阻、漏電流等性能上存在散差,易引發過放隱患。

- 過放風險:單體電壓失控不僅影響整體效率,還會縮短壽命。

- 恒流精度:實際應用要求電流波動控制在±2%以內。

- 模式切換:系統需在充電、放電、均壓與恒流等狀態間無縫轉換。

二、FPGA控制的三大優勢

- 多通道并行與高速PWM

? 同時輸出5kHz均壓逆變與20kHz升壓斬波PWM信號,實現兩路并行運作。

? 自動插入死區時間,保護MOSFET,提升可靠性。

- 納秒級實時采樣與PI閉環

? AD模塊周期性獲取超級電容組與直流母線電壓,FPGA在納秒級完成PI運算,電流穩定可控。

? 根據Vdc與Vc上限/下限,靈活切換恒流或恒壓模式。

- 可編程與模塊化拓展

? 基于EP2C80 FPGA,邏輯單元可重構,支持后續SOC管理、電流共享等功能升級。

? 模塊化信號接口(S1~S4、Buck/Boost)簡化布線,縮短迭代周期。

三、恒流放電原理概覽

- 雙向Buck/Boost拓撲

? 放電時工作于Boost模式,將超級電容能量推至母線,保持母線電壓恒定。

? FPGA讀取母線電壓與電流,通過PI調節Boost占空比,實現目標電流放電。

- 恒流/恒壓切換策略

? Vc>Vcmax時,僅允許Boost放電;Vc< Vcmin時,自動封鎖放電信號。

? Vdc高于Vdcmax→Buck充電;低于Vdcmin→Boost放電;二者之間→待機。

- 靈活采樣與算法下發

? FPGA中斷觸發ADC采樣,串口實時下發PI參數,現場標定無需更換硬件。

四、均壓電路與FPGA協同

- 逆變—變壓器均壓

? FPGA驅動H橋生成50%占空比方波,經降壓變壓器為單體并聯供電。

? 只有電壓低于平均值的單體被二極管反向導通充電,實現定向均壓。

- 升壓斬波工藝

? 總電壓Vc加上二極管及MOSFET導通壓降后形成Vi,FPGA輸出20kHz PWM保持系統穩定。

- 高效同步控制

? 同時管理H橋與Boost占空比,動態調節均壓速度;死區與軟啟邏輯確保平滑過渡。

五、系統架構與驗證

- 硬件平臺

? FPGA控制板:Altera EP2C80 208C8N;MOSFET:5×IRF640,驅動TR2103。

? 降壓變壓器、Boost模塊、電壓采樣及保護電路。

- 軟件流程

? 采樣→模式判定→PI計算→PWM輸出→反饋,四路判斷模塊精準切換。

- 測試數據

? 4只電容初始2.7V/1.0V,70s內均壓至1.81V;

? 恒流放電波動≤±1.5%,10萬次循環后性能穩定。

在我們的實驗室測試中,FPGA憑借高速并行處理與精細閉環控制,實現了多模式切換和串聯均壓兩大關鍵目標。未來,隨著FPGA算力提升與算法優化,該平臺將在新能源汽車、智能電網等需要高功率瞬時輸出的場景中發揮更大價值。喜歡這篇文章,別忘了點贊、收藏并在評論區分享你的測試心得!

-

超級電容器

+關注

關注

19文章

566瀏覽量

30383 -

恒流

+關注

關注

1文章

221瀏覽量

32263

發布評論請先 登錄

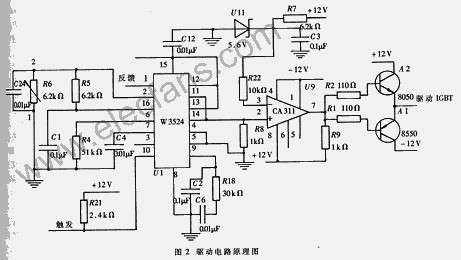

超級電容器恒功率放電系統中IGBT驅動的設計

基于FPGA的超級電容均壓及充放電設計方案

基于新型電子負載恒流放電設備的研究

89C51在蓄電池恒流放電中的應用

89C51在蓄電池恒流放電中的應用

新穎的自動恒流放電系統的設計

安泰測試:同惠TH8204可編程直流負載如何實現恒流放電?

超級電容恒流放電怎么實現

超級電容恒流放電怎么實現

評論