PCM1789:高性能立體聲 DAC 的技術剖析與應用指南

在音頻處理領域,數字到模擬轉換器(DAC)扮演著至關重要的角色。今天我們要深入探討的是德州儀器(Texas Instruments)的 PCM1789,一款專為消費音頻應用設計的高性能立體聲 DAC。

文件下載:pcm1789.pdf

一、產品概述

PCM1789 是一款單芯片、24 位立體聲音頻 DAC,具有差分輸出。它采用增強型多級 ΔΣ 調制器,支持 8 kHz 至 192 kHz 的采樣率,以及 16、20、24 和 32 位寬度的數字音頻輸入。該芯片適用于多種音頻設備,如藍光播放器、DVD 播放器、AV 接收器、家庭影院和汽車音頻系統等。

二、關鍵特性

2.1 高性能 DAC

- 出色的音頻指標:在 (f_{S}=48 kHz) 時,總諧波失真加噪聲(THD + N)低至 -94 dB,信噪比(SNR)高達 113 dB,動態范圍達 113 dB,能提供高質量的音頻輸出。

- 寬采樣率范圍:支持 8 kHz 至 192 kHz 的采樣率,可滿足不同音頻源的需求。

- 系統時鐘靈活:系統時鐘支持 128 (f{S})、192 (f{S})、256 (f{S})、384 (f{S})、512 (f{S})、768 (f{S}) 和 1152 (f_{S}) 等多種倍數,方便與不同的時鐘源配合使用。

2.2 靈活的音頻接口

- 多種數據格式:支持 I2S、左對齊、右對齊和 DSP 等多種音頻接口格式,數據長度可選 16、20、24 或 32 位,能適應不同的音頻系統架構。

2.3 多樣的控制方式

- 軟件控制:可通過三線 SPI 或兩線 I2C 兼容的串行接口進行軟件控制,實現音頻接口格式選擇、數字衰減、軟靜音、數字去加重等多種功能。

- 硬件控制:支持硬件控制模式,通過兩個控制引腳提供兩個用戶可編程功能。

2.4 其他特性

- 模擬靜音功能:通過時鐘停止檢測實現模擬靜音,可有效減少噪聲干擾。

- 外部復位引腳:方便進行系統復位操作。

- 寬溫度范圍:工作溫度范圍為 -40°C 至 85°C,能適應不同的工作環境。

三、引腳配置與功能

PCM1789 采用 24 引腳 TSSOP 封裝,各引腳具有特定的功能。例如,LRCK 為音頻數據字時鐘輸入,BCK 為音頻數據位時鐘輸入,DIN 為音頻數據輸入,RST 為復位和掉電控制輸入等。在設計 PCB 時,需要根據引腳功能進行合理的布局和連接,以確保芯片的正常工作。

四、電氣特性

4.1 絕對最大額定值

了解芯片的絕對最大額定值非常重要,它規定了芯片在正常工作時所能承受的最大電壓、電流和溫度等參數。例如,模擬電源電壓 VCC1 和 VCC2 的范圍為 -0.3 V 至 6.5 V,數字電源電壓 VDD 的范圍為 -0.3 V 至 4.0 V 等。在設計電源電路時,必須確保電源電壓在這些額定值范圍內,否則可能會損壞芯片。

4.2 推薦工作條件

為了獲得最佳的性能,芯片需要在推薦的工作條件下運行。例如,模擬電源電壓 VCC 推薦為 4.5 V 至 5.5 V,數字電源電壓 VDD 推薦為 3.0 V 至 3.6 V,采樣頻率 LRCK 范圍為 8 kHz 至 192 kHz 等。

4.3 音頻性能指標

芯片的音頻性能指標直接影響音頻輸出的質量。如前面提到的 THD + N、SNR 和動態范圍等指標,以及通道分離度、增益誤差等參數,都需要在設計過程中進行關注和優化。

五、詳細功能描述

5.1 模擬輸出

PCM1789 的模擬輸出為差分電壓輸出,滿量程輸出電壓為 (1.6 × VCC1) (VPP)。內部輸出放大器帶有 RC 連續時間濾波器,可減少帶外噪聲能量,但通常還需要外部低通濾波器來進一步降低帶外噪聲。

5.2 電壓參考 VCOM

VCOM 引腳提供共模電壓輸出,可通過去耦電容連接到模擬地,也可用于偏置外部高阻抗電路。

5.3 系統時鐘輸入

系統時鐘輸入 SCKI 是芯片正常工作的關鍵。它必須是采樣頻率 (f{S}) 的整數倍,具體倍數支持 128 (f{S})、192 (f_{S}) 等多種選擇。在設計時鐘電路時,需要確保時鐘信號的穩定性和準確性。

5.4 復位操作

芯片具有內部上電復位電路和外部復位電路。上電時,當 VDD 超過 2.2 V 時,內部復位自動觸發,經過 3846 個 SCKI 時鐘周期后釋放。外部復位通過 RST 引腳實現,低電平有效,可使芯片進入復位和掉電狀態。

5.5 ZERO 標志

ZERO1 和 ZERO2 為零檢測標志引腳,可通過控制寄存器 22 中的 AZRO 位選擇不同的組合方式。當指定通道的輸入數據連續 1024 個采樣周期為 '0' 時,相應的 ZERO 標志位被置為高電平。

5.6 AMUTE 控制

AMUTEI 為模擬靜音控制輸入引腳,低電平有效,可使 DAC 輸出與數字輸入斷開,并將輸出強制為中心電平(0.5 VCC1)。AMUTEO 為模擬靜音狀態輸出引腳,低電平表示模擬靜音控制電路處于激活狀態。

5.7 串行控制接口

- SPI 控制:芯片支持 SPI 兼容的串行端口,通過 MD/SDA/DEMP、MC/SCL/FMT 和 MS/ADR0/RSV 三個引腳進行控制。控制數據字為 16 位,可實現單寫和多寫操作。

- I2C 控制:支持 I2C 兼容的串行總線和數據傳輸協議,作為從設備工作。具有 7 位從地址,可通過 MS/ADR0/RSV 和 ADR5/ADR1/RSV 兩個引腳進行選擇。

六、應用與實現

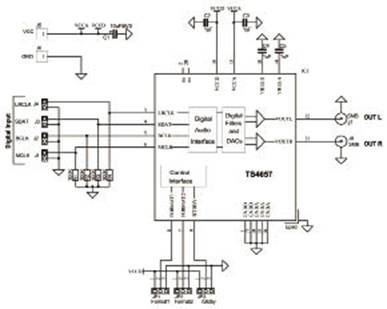

6.1 連接圖

基本連接圖中需要包含必要的電源旁路和去耦組件。推薦使用德州儀器的 PLL170X 來生成系統時鐘輸入 SCKI,同時為音頻信號處理器提供時鐘。在 SCKI、LRCK、BCK 和 DIN 信號線上使用 22 Ω 至 100 Ω 的串聯電阻,可減少電磁干擾(EMI)。

6.2 電源與接地

芯片需要 +5 V 的模擬電源和 +3.3 V 的數字電源。為了獲得最佳性能,建議使用線性穩壓器(如 REG1015/33、REG102 - 5/33 或 REG103 - 5/33)為電源供電。同時,需要使用五個電容進行電源旁路,其中 10 - μF 的電容為鋁電解電容,3 個 1 - μF 的電容為陶瓷電容,且這些電容應盡量靠近芯片封裝。

6.3 低通濾波器與差分轉單端轉換器

由于 ΔΣ DAC 會產生帶外噪聲,因此需要使用低通濾波器來提高轉換器的性能。推薦使用二階巴特沃斯濾波器作為外部差分轉單端轉換器,如 NE5532A、OPA2134 或 OPA2353 等高性能音頻運放可用于這些濾波器電路。

6.4 典型應用設計

在典型應用中,需要考慮控制方式(硬件、I2C 或 SPI)、音頻輸入(PCM 串行數據、TDM 或 DSP)、音頻輸出((1.6 × VCC1) (Vpp) 模擬音頻偏置到 (0.5 × VCC1) V)和主時鐘(如 PLL170X 系列)等設計要求。

七、布局建議

7.1 布局準則

- 使用接地平面:推薦使用接地平面,并通過分割或切割電路板將模擬和數字部分隔離,以減少相互干擾。

- 合理安排引腳方向:將數字 I/O 引腳朝向接地平面分割處,以便與數字音頻接口和控制信號進行短而直接的連接。

- 分離電源:為數字和模擬部分分別提供獨立的電源,防止數字電源的開關噪聲影響模擬電源,從而保證芯片的動態性能。

7.2 布局示例

典型的 PCB 布局示例展示了如何將數字和模擬部分進行合理的劃分,以及如何連接芯片與其他電路組件。

八、總結

PCM1789 是一款功能強大、性能出色的立體聲 DAC,具有豐富的特性和靈活的控制方式。在音頻設計中,通過合理選擇和應用該芯片,結合正確的電路設計、布局和電源管理,可以實現高質量的音頻輸出。希望本文能為電子工程師在使用 PCM1789 進行音頻設計時提供有價值的參考。大家在實際應用中遇到過哪些問題呢?歡迎在評論區分享交流。

-

音頻設計

+關注

關注

0文章

82瀏覽量

11578 -

PCM1789

+關注

關注

1文章

2瀏覽量

7007

發布評論請先 登錄

PCM1789:高性能立體聲 DAC 的技術剖析與應用指南

PCM1789:高性能立體聲 DAC 的技術剖析與應用指南

評論