引言

在嵌入式系統開發與測試中,穩定、精確的測試信號生成是一項常見且關鍵的需求。傳統方法依賴于CPU實時計算并搬運數據,這會持續占用處理器資源,增加系統功耗,并可能影響主程序的實時性。為解決這一問題,本文介紹一種利用瑞薩RA2L1微控制器(MCU)的DAC、DTC和AGT三個外設模塊協同工作的解決方案。該方案能夠以極低的CPU參與度,高效生成正弦波、三角波等多種標準波形,為需要模擬信號輸出的應用提供了一種高性能、低功耗的設計范例。

核心模塊

DTC(數據傳輸控制器)模塊

DTC(Data Transfer Controller)模塊根據傳輸信息進行數據傳輸,需要先在SRAM區域存儲傳輸信息。DTC被激活時,會讀取與向量號相關聯的DTC向量,從DTC向量中引用的傳輸信息存儲地址讀取傳輸信息并進行數據傳輸。

傳輸模式包括普通傳輸模式(Normal transfer mode)、重復傳輸模式(Repeat transfer mode)和塊傳輸模式(Block transfer mode)。DTC在DTC傳送源寄存器(SAR)中指定傳輸源地址,在DTC傳送目標寄存器(DAR)中指定傳輸目的地址。在數據傳輸后,這些寄存器的值可以獨立地增減或保持不變。

AGT(低功耗異步通用定時器)模塊

AGT(Low Power Asynchronous General Purpose Timer)模塊是一個靈活的16位定時器,可在低功耗模式下運行。在本設計中,它被配置為周期定時模式,用于產生固定時間間隔的中斷。這些中斷信號作為“觸發源”,定期激活DTC,從而精確控制DAC輸出每個數據點的時間間隔,決定了最終輸出波形的頻率。

DAC(數模轉換器)模塊

RA2L1提供一個帶輸出放大器的12位數模轉換器(DAC12),由AVCC0和AVSS0提供模擬電源及模擬參考電壓源,輸出引腳為DA0。DAC12的D/A數據寄存器0(DADR0)適用于存儲數模轉換數據的16位讀/寫寄存器,啟動模擬輸出后,DADR0中的數值會被轉換并輸出到模擬輸出引腳(DA0)中。

系統設計方案

系統架構

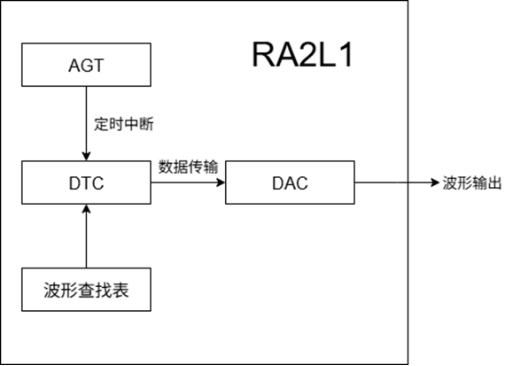

圖1.系統架構

DAC模塊:負責最終的數模轉換與電壓輸出。

AGT模塊:作為系統的“節拍器”,產生固定周期的中斷來觸發數據傳輸。

DTC模塊:作為“數據搬運工”,在每次AGT中斷時,自動將LUT中的下一個數據點送至DAC。

波形查找表

波形查找表機制

兩種波形的數據都預先計算并存儲在查找表(LUT)中。系統運行時,DTC模塊按固定時間間隔依次讀取表中數據并傳輸到DAC寄存器,實現波形的周期性輸出。這種方式避免了實時計算,大幅降低CPU負載。

正弦波查找表

使用余弦函數計算一個完整周期(T=input_spp)的采樣點數據。通過cos(2πi/input_spp)計算每個采樣點的瞬時值(i=0,1,???,input_spp-1)。由于余弦函數輸出范圍是[-1,1],需要加1后乘以DAC中間值((DAC_MID_VAL),將其映射到DAC的有效輸出范圍(0~4095)。采樣點數越多,生成的波形越平滑。

正弦波查找表函數

左右滑動查看完整內容

voidgenerate_sin(void) { /* Calculate look up table for sin function */ for(int i=0; i< input_spp; ++i) ? ? { ? ? ? ? look_up_table[i] = (uint16_t)?

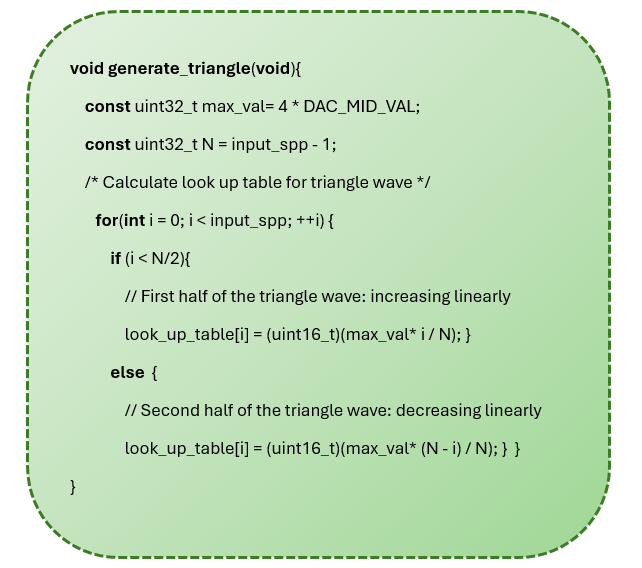

三角波查找表

采用分段線性計算方式。前半周期線性遞增,從0上升到最大值;后半周期線性遞減,從最大值下降到0,形成對稱的三角波形。計算公式基于當前采樣點位置與總采樣點數的比例關系,通過簡單的線性插值即可得到每個點的輸出值。

三角波查找表函數

軟件流程

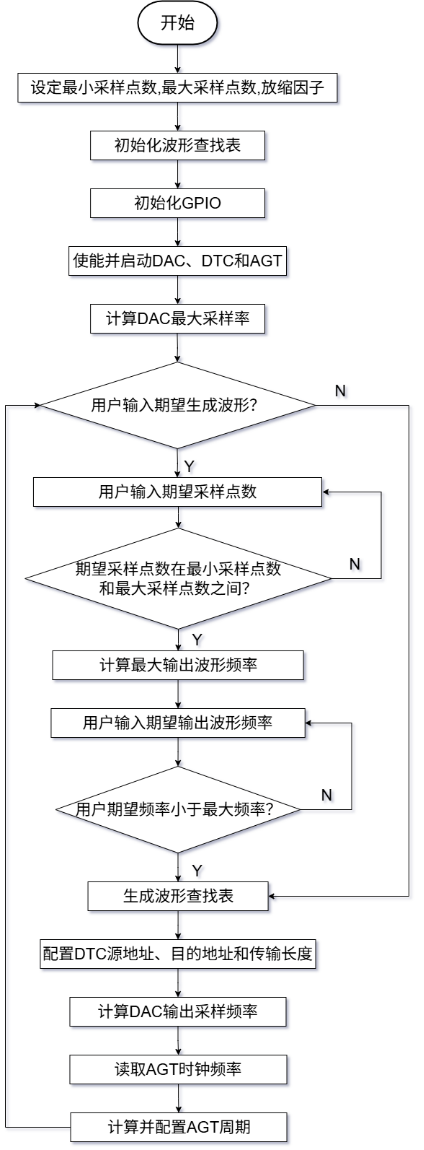

圖2. 主流程

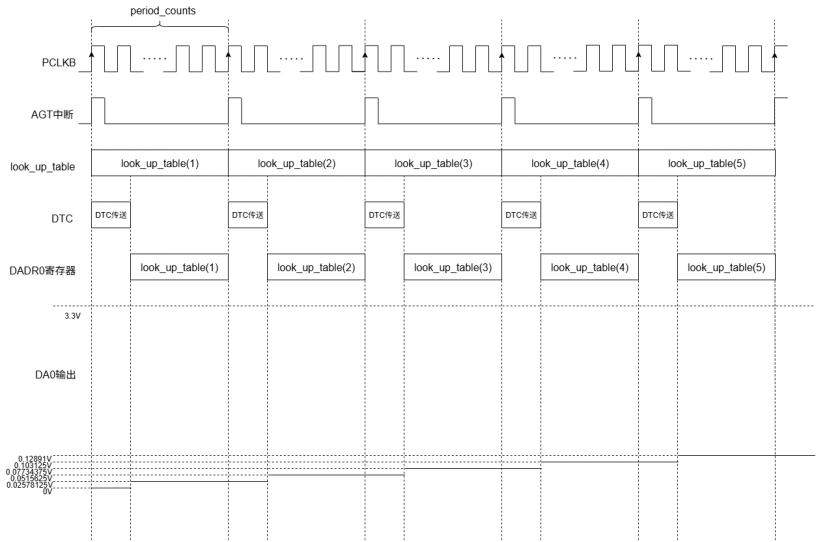

系統時序

圖3.系統時序圖

開發環境

表1 開發環境

| 項目 | 內容 |

| 所用微控制器 | RA2L1(R7FA2L1AB2DFM) |

| 工作頻率 | HOCO:48MHz,PCLKB:24MHz |

| 工作電壓 | 3.3V(工作電壓范圍1.6V~5.5V) |

| 開發板 | CPK-RA2L1 MCU評估板(LQFP64) |

| 集成開發環境 |

e2studio v2025-07(瑞薩電子開發) FSP v6.0.0 LLVM for ARM v18.1.3 |

| BSP文件 | Renesas.RA_board_ra2l1_cpk.3.7.0.pack |

RA2L1 - 48MHz Arm Cortex-M23超低功耗通用微控制器 | Renesas瑞薩電子

https://www.renesas.cn/zh/products/ra2l1?queryID=0135065201ac0d335ce3d718259fb7b4

CPK-RA2L1 - RA2L1 MCU群組中國本地評估板 | Renesas瑞薩電子

https://www.renesas.cn/zh/design-resources/boards-kits/cpk-ra2l1?queryID=7488f1b4dfae70a40b8d81382c878554

e2studio | Renesas瑞薩電子

https://www.renesas.cn/zh/software-tool/e2-studio?queryID=c68ed897f8fb82511bedafe733272066

RA可擴展性強的配置軟件包(FSP) | Renesas瑞薩電子

https://www.renesas.cn/zh/software-tool/ra-flexible-software-package-fsp?queryID=a5545772de53314f3a65441b56a71922

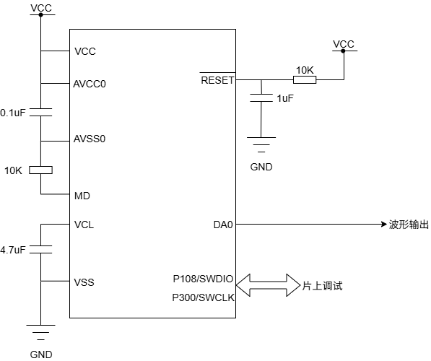

硬件配置

圖4.硬件配置示例

參考例程

為便于讀者快速上手,本文提供了一個完整的波形生成參考例程。該例程實現了正弦波和三角波的生成與切換功能,讀者可以在此基礎上進行測試、二次開發和功能擴展。

dac_cpkcor_ra2l1_ep.zip

https://e.gitee.com/recn-mcu-ae/repos/recn-mcu-ae/dac_cpkcor_ra2l1_ep/sources

gitee下載鏈接

https://e.gitee.com/recn-mcu-ae/repos/recn-mcu-ae/dac_cpkcor_ra2l1_ep/sources

例程操作說明

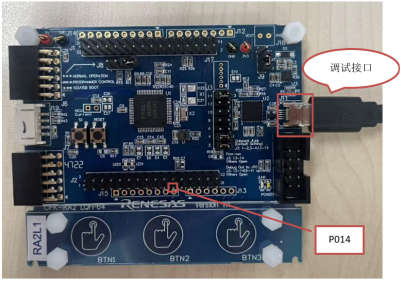

硬件準備

參考例程使用的是瑞薩中國本地推廣板CPK-RA2L1 MCU評估板(LQFP64),如圖5所示。開發板調試接口為J11,波形輸出端口(P014)從J2連接器的Pin 21引出(見圖5中紅框)。

圖5.CPK-RA2L1 MCU評估板(LQFP64)

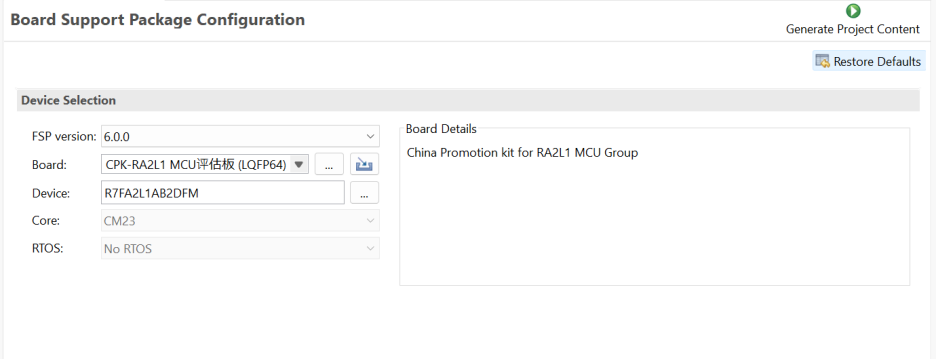

工程配置

由于例程中使用的開發板為CPK開發板,因此在首次使用時需要導入BSP文件,導入方法見《向FSP中添加CPK評估板的BSP》。導入BSP文件后可選擇CPK-RA2L1評估版,請確認configuration.xml中的BSP信息與圖6一致。

向FSP中添加CPK評估板的BSP

https://www.renesas.cn/zh/document/gde/fsp-cpk-bsp?r=1596841

圖6.參考例程中BSP信息

編譯與燒錄:

確認BSP信息無誤后即可對工程進行編譯,燒錄到開發板中并運行程序。

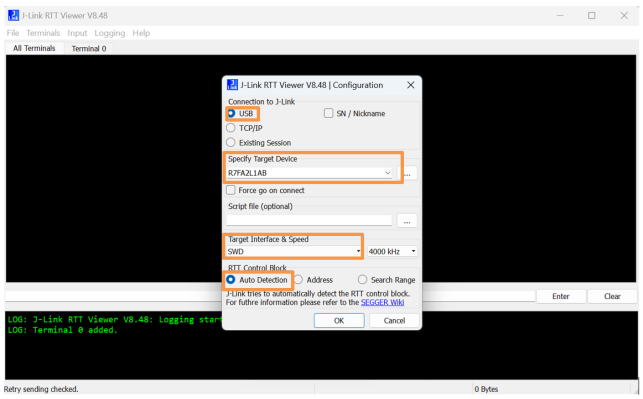

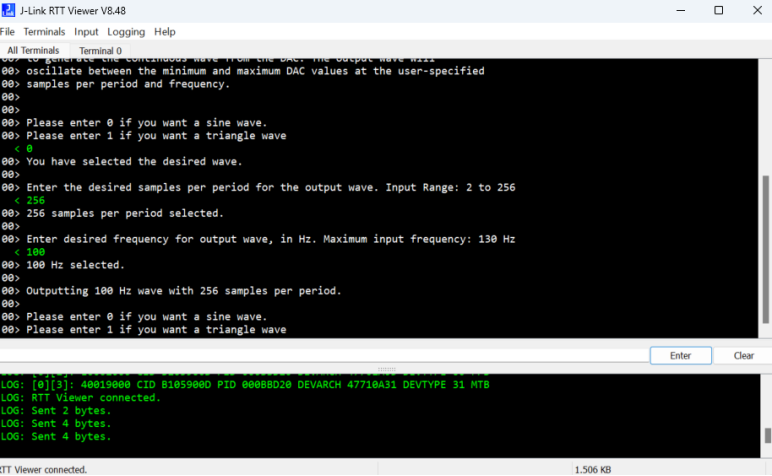

交互控制

打開J-Link RTT Viewer,選擇USB連接方式,將“Specify Target Device”設定為“R7FA2L1AB”,“RTT Control Block”選擇為“Auto Detection”,點擊“OK”后即可連接到開發板。

圖7.J-Link RTT Viewer配置信息

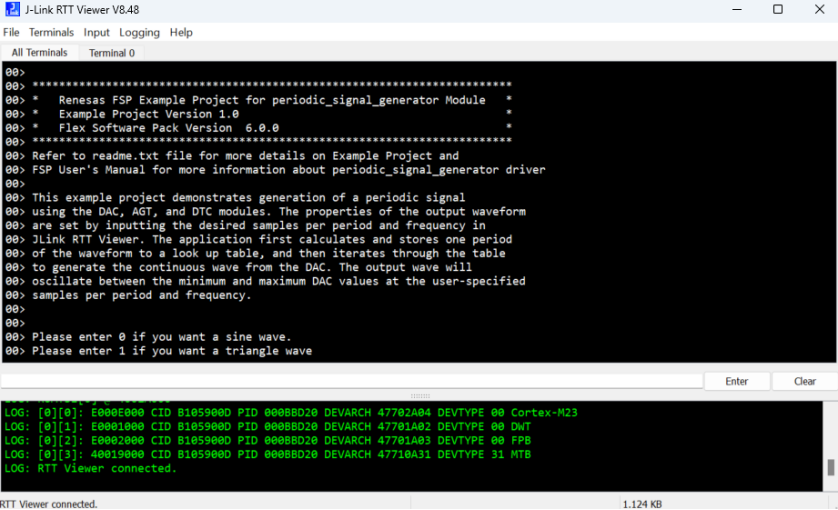

成功連接到開發板后可看到如圖8的工程信息,包括工程版本、FSP版本、例程說明等等。

圖8.J-Link RTT Viewer工程信息顯示

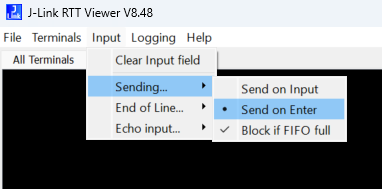

如圖9所示,用戶需要對J-Link RTT Viewer中發送數據的方式進行以下設置。

圖9.J-Link RTT Viewer輸入設置

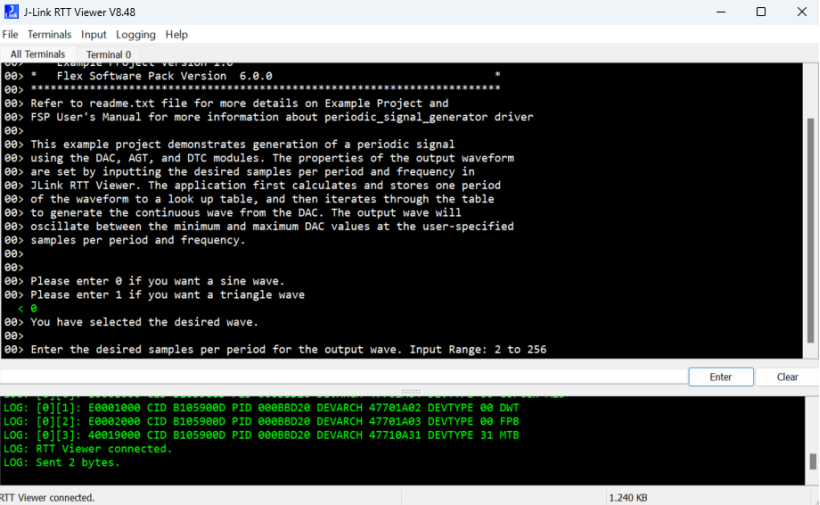

參照圖8中的提示,用戶輸入“0”可以選擇生成正弦波,輸入“1”可以選擇生成三角波,首先輸入“0”選擇正弦波輸出,如圖10所示。

圖10.選擇正弦波輸出

根據圖10中的信息,下一步需要輸入期望采樣點數,注意輸入值需要在2到256之間。

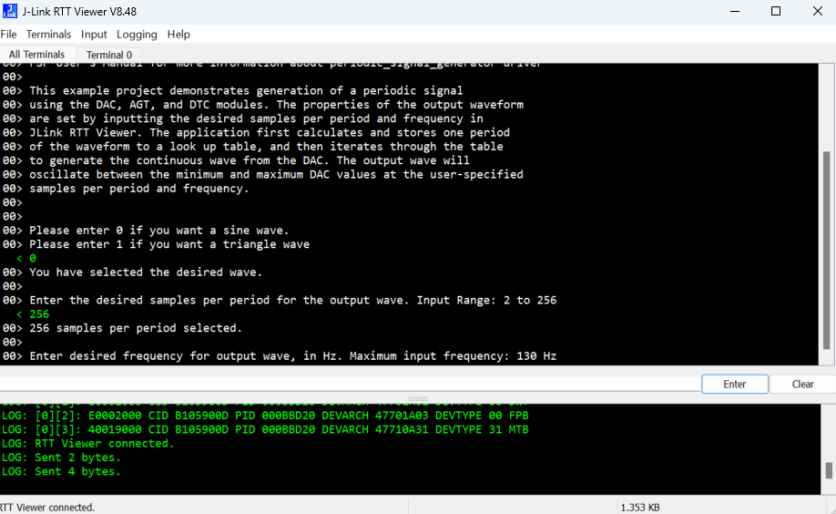

圖11.輸入期望采樣點數

最后需要輸入期望輸出波形頻率,注意波形頻率的最大值已根據期望采樣點數計算得出,因此輸入的期望頻率需要小于最大波形頻率。

圖12.輸入期望頻率

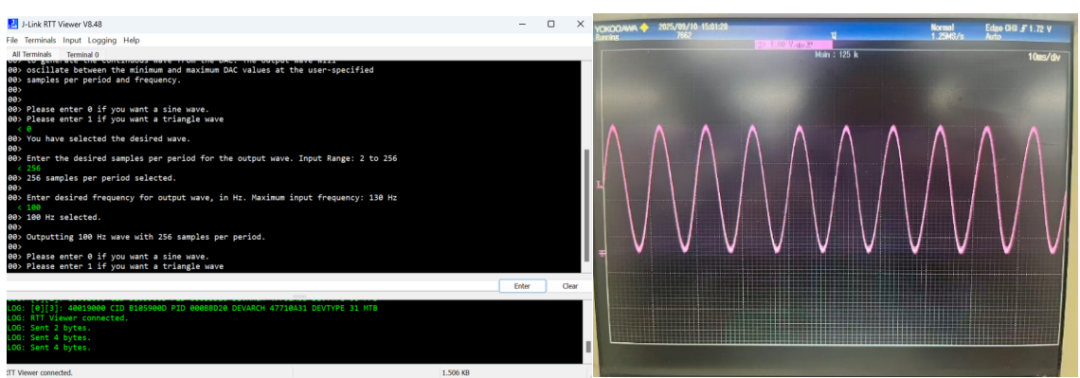

波形觀測

圖13為輸入“0”后生成采樣點為256,頻率為100Hz的正弦波輸出結果。

圖13.正弦波輸出結果

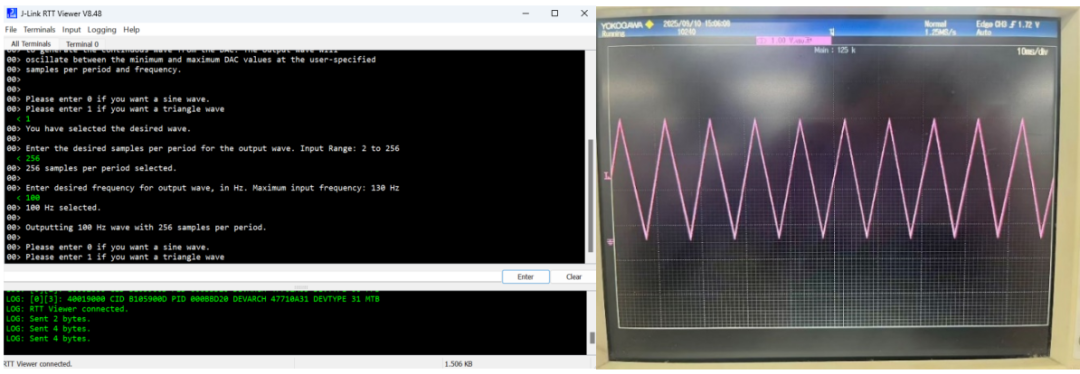

圖14為輸入“1”后生成采樣點為256,頻率為100Hz的三角波輸出結果。

圖14.三角波輸出結果

代碼說明

常量一覽

例程中所用常量見表2。

表2 常量說明

| 常量名稱 | 數值 | 說明 |

| SPP_MIN_VAL | 2 | 最小采樣點數 |

| SPP_MAX_VAL | 256 | 最大采樣點數 |

| DAC_MID_VAL | 2047.5 | 波形放縮系數 |

| DADR0 | 0x4005E000 |

DADR0 寄存器地址 |

|

DAC_MAX_ CONVERSION_PERIOD |

30 | DAC最大采樣周期 |

變量一覽

例程中所用變量見表3。

表3 變量說明

| 類型 | 變量名稱 | 內容 |

| uint16_t |

look_up_table [SPP_MAX_VAL] |

波形查找表 |

| uint16_t | input_spp | 用戶期望采樣點數 |

| uint32_t | input_freq | 用戶期望輸出波形頻率 |

| uint32_t | wave_output | 用戶期望輸出波形類型 |

| double | sample_freq | DAC采樣頻率 |

| uint32_t | freq_max_val | 最大輸出頻率 |

| double | dac_max_samp_rate | DAC最大采樣率 |

函數一覽

例程中所用函數見表4。

表4 函數說明

| 類型 | 內容 |

| R_FSP_VersionGet() | 獲取FSP版本 |

| R_IOPORT_PinCfg() | 配置引腳設置 |

| R_DAC_Open() | 初始化DAC |

| R_DAC_Start() | 開啟數模轉換輸出 |

| R_DTC_Open() | 啟用DTC |

| R_DTC_Enable() | 啟用傳輸 |

| R_AGT_Open() | 初始化AGT |

| R_AGT_Start() | 啟動定時器 |

| R_DTC_Reconfigure() | 配置DTC |

| R_FSP_SystemClockHzGet() | 獲取系統時鐘頻率 |

| R_AGT_PeriodSet() | 更新AGT周期 |

| generate_sin() | 生成正弦波波形查找表 |

| generate_triangle() | 成三角波波形查找表 |

結語

本文詳細闡述了基于RA2L1 MCU的硬件協同波形生成方案。通過巧妙運用AGT定時觸發、DTC自動搬運、DAC轉換輸出三者形成的“硬件流水線”,成功將CPU從頻繁的數據搬運任務中解放出來,實現了極低的處理器占用與功耗。預存波形查找表的方法不僅保證了高精度輸出,也預留了強大的擴展能力,可輕松支持方波、鋸齒波或任意自定義波形。

該設計理念突出了利用MCU豐富外設實現功能卸載、優化系統效率的嵌入式設計思想。讀者可基于提供的參考例程,快速進行原型驗證,并靈活調整采樣率、輸出頻率及波形種類,以滿足各類嵌入式應用中對模擬信號生成的需求。

-

微控制器

+關注

關注

48文章

8322瀏覽量

163921 -

mcu

+關注

關注

147文章

18855瀏覽量

394912 -

瑞薩

+關注

關注

37文章

22473瀏覽量

90260 -

定時器

+關注

關注

23文章

3367瀏覽量

122724 -

波形

+關注

關注

3文章

406瀏覽量

33010

原文標題:基于瑞薩RA2L1的波形生成系統設計——DTC、AGT與DAC的協同應用

文章出處:【微信號:瑞薩嵌入式小百科,微信公眾號:瑞薩嵌入式小百科】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

瑞薩RA2L1 MCU e2 studio和FSP的使用指南

基于瑞薩RA2L1 MCU的波形生成系統設計

基于瑞薩RA2L1 MCU的波形生成系統設計

評論