隨著多核片上系統 (SoC) 的復雜性不斷增加,SoC 調試變得越來越具有挑戰性。這些系統的軟件調試和優化工作正在不斷升級,從而增加了開發時間、工作量和成本。現在迫切需要更高效、更具可擴展性的調試方法來幫助工程師快速發現并解決硬件和實時軟件問題。

Tessent UltraSight-V 是用于 RISC-V 調試和跟蹤的完整端到端解決方案,其設計符合官方 RISC-V E-Trace 規范。該嵌入式 IP 和軟件解決方案提供全面、高效的調試和跟蹤功能,這些功能可與行業標準工具集成,幫助嵌入式軟件工程師開發高性能嵌入式軟件。

Tessent UltraSight-V 是 Tessent 嵌入式分析產品系列的一部分,采用了高效的非侵入式技術,例如基于高效跟蹤 (E-Trace) 標準的高度壓縮編碼處理器跟蹤、日志記錄、高速接口(USB 2.0) 和 DMA,以實現快速代碼上傳。該解決方案極大限度限度地減少了調試延遲,加快了 SoC 項目的進程,從而使您能夠在市場截止日期前完成上市過程。

RISC-V 處理器的高度壓縮跟蹤解決方案

復雜系統容易出現不理想的軟件行為。Tessent UltraSight-V 的增強型跟蹤編碼器 (ETE) 提供了一種實時監控 CPU 程序執行的機制。它可對指令執行過程(可選地為數據內存訪問過程)進行編碼。它還能夠以高度壓縮的格式輸出跟蹤,從而大幅節省了帶寬,在大型復雜系統中尤為如此。設備執行可以完全離線重建。非侵入式 ETE 的工作延遲極小,因此不會影響性能。

篩選跟蹤可以幫助您進一步調查問題。增強型跟蹤編碼器支持 E-Trace 規范中的所有強制和選配功能。它還可以提供周期精確的跟蹤,從而為軟件性能優化提供見解。

RISC-V 處理器的完整調試和跟蹤解決方案

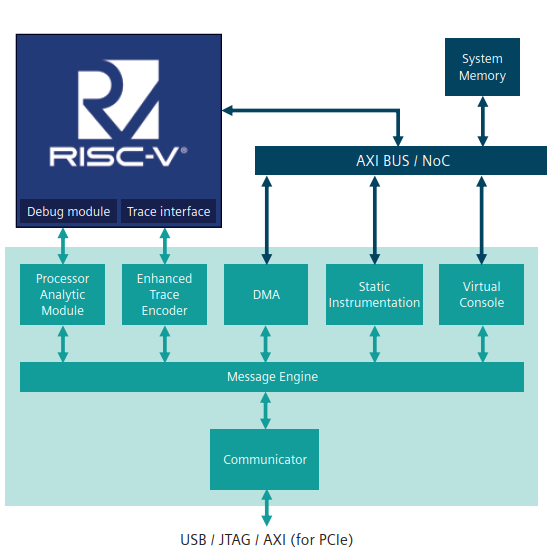

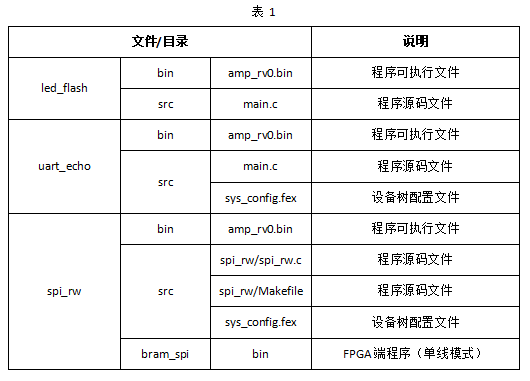

Tessent UltraSight-V 包括一組 IP 模塊和主機軟件,它們對軟件應用程序在系統中的行為方式具有廣泛可見性。處理器分析模塊提供運行控制功能。借助直接內存訪問 IP 模塊可將代碼上傳到 SoC,其速度為正常 GDB 加載速度的 70-100 倍。借助靜態儀器 IP 模塊,可通過數量僅為原來二十分之一的指令完成帶時間戳的 printf 風格調試。虛擬控制臺模塊于在目標上運行的軟件和調試主機之間提供了一個雙向通信通道。它取代了傳統的基于 UART 的通信,無需額外的物理端口。可擴展的專用基礎設施可確保實現非侵入式監控。該基礎設施可通過 USB、JTAG 或 PCIe 接口訪問(見圖1)。UltraSight-V 中的主機軟件與 GDB、OpenOCD 和 VS Code 等常見 IDE 集成(見圖2)。

▲ 圖 1

▲ 圖 2

總結

綜上所述,Tessent UltraSight-V 是面向 RISC-V 處理器的全面調試和跟蹤解決方案,它結合了嵌入式 IP 和軟件,能夠實現高效的調試和跟蹤,同時還與行業標準工具集成,為高性能嵌入式軟件的開發提供支持。

要點包括:

它是 RISC-V 調試和跟蹤的完整解決方案。

它的設計符合官方 RISC-V 跟蹤規范。

它是由嵌入式 IP 和軟件組成的端到端解決方案。

它提供了全面、高效的調試和跟蹤功能。

它與行業標準工具集成。

它使得嵌入式軟件工程師能夠開發高性能嵌入式軟件。

Tessent UltraSight-V 的功能體現了西門子在 RISC-V 調試和跟蹤解決方案方面的深厚專業知識和領先地位。

如需了解 Tessent UltraSight-V 和西門子 EDA 的其他嵌入式分析解決方案的詳細信息,請點擊此處查閱。

-

嵌入式

+關注

關注

5198文章

20446瀏覽量

334011 -

cpu

+關注

關注

68文章

11278瀏覽量

224960 -

RISC-V

+關注

關注

48文章

2886瀏覽量

52992

原文標題:利用 Tessent UltraSight-V 加速 RISC-V 開發

文章出處:【微信號:Mentor明導,微信公眾號:西門子EDA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

新思科技ARC-V處理器驅動RISC-V市場無限機遇

為什么RISC-V是嵌入式應用的最佳選擇

西門子推出Tessent IJTAG Pro

大灣區RISC-V生態全景展示:RISC-V生態發展論壇、開發者Workshop和生態應用專區

國產!全志T113-i 雙核Cortex-A7@1.2GHz 工業開發板—RISC-V案例開發手冊(上)

明晚開播 |開源芯片系列講座第28期:高性能RISC-V微處理器芯片

直播預約 |開源芯片系列講座第28期:高性能RISC-V微處理器芯片

西門子EDA即將亮相2025 RISC-V中國峰會

RISC-V和ARM有何區別?

西門子再收購EDA公司 西門子宣布收購Excellicon公司 時序約束工具開發商

西門子EDA Tessent UltraSight-V助力RISC-V處理器開發

西門子EDA Tessent UltraSight-V助力RISC-V處理器開發

評論