如果我們直接控制RA6M5的兩個GPIO引腳,分別用作SCL及SDA,按照上述信號的時序要求,直接像控制LED燈那樣控制引腳的輸出(若是接收數據時則讀取SDA電平),就可以實現I2C通訊。同樣,假如我們按照USART的要求去控制引腳,也能實現USART通訊。所以只要遵守協議,就是標準的通訊,不管您如何實現它,不管是ST生產的控制器還是ATMEL生產的存儲器,都能按通訊標準交互。

由于直接控制GPIO引腳電平產生通訊時序時,需要由CPU控制每個時刻的引腳狀態,所以稱之為“軟件模擬協議”方式。

相對地,還有“硬件協議”方式,RA6M5的I2C片上外設專門負責實現I2C通訊協議,只要配置好該外設,它就會自動根據協議要求產生通訊信號,收發數據并緩存起來,CPU只要檢測該外設的狀態和訪問數據寄存器,就能完成數據收發。這種由硬件外設處理I2C協議的方式減輕了CPU的工作,且使軟件設計更加簡單。

21.2.1.瑞薩RA6M5的I2C外設簡介

瑞薩RA6M5的I2C外設可用作通訊的主機及從機,支持100Kbit/s和400Kbit/s和1Mbit/s的速率,支持7位、10位設備地址,支持DMA數據傳輸,并具有數據校驗功能。它的I2C外設還支持SMBus2.0協議,SMBus協議與I2C類似,主要應用于筆記本電腦的電池管理中。

表1:瑞薩RA6M5的IIC支持頻率

21.2.1.1.通訊引腳

I2C的所有硬件架構都是根據圖中左側SCL線和SDA線展開的(其中的SMBA線用于SMBUS的警告信號,I2C通訊沒有使用)。RA6M5芯片有多個I2C外設,它們的I2C通訊信號引出到不同的GPIO引腳上,使用時必須配置到這些指定的引腳,見表22?1。

關于GPIO引腳的復用功能,可查閱《RA6M5GroupUser_sManual》,以它為準。

表22?1:RA6M5的I2C引腳(整理自《RA6M5GroupUser_sManual》)

21.2.2.瑞薩RA6M5的I2C功能框圖

注:

我們這里主要介紹的是瑞薩的fsp庫的使用,所以在這里寄存器我們在這里做一些簡單的介紹。

21.2.3. 時鐘控制邏輯

下面將介紹時鐘的控制流程

21.2.3.1. IIC起始信號與重啟信號

當ICCR2中的RS位被設置為1時,IIC會發出一個重啟條件請求。當ICCR2的BBSY標志位為1(總線繁忙狀態),ICCR2的MST位為1(主模式)時IIC發出重啟條件。 發出重啟條件:

釋放SDAn線路。

確保ICBRL中設置的SCLn線路的低電平周期已過。

釋放SCLn線(低電平到高電平)。

在SCLn線上檢測高電平,并確保ICBRL中設置的時間和重啟條件設置時間經過。

將SDAn線拉低(從高電平到低電平)。

確保ICBRH中設置的時間和重啟條件保持時間。

驅動SCLn線低電平(高電平到低電平)。

檢測SCLn線上的一個低水平,確保ICBRL中設置的SCLn線的低水平周期已經過去

21.2.3.2. IIC循環發送

初始化IIC。

讀取ICCR2中的BBSY標志,檢查總線是否打開,然后設置ICCR2中的ST位為1(啟動條件發出請求)。收到請求后,IIC發出啟動條件。與此同時,BBSY位和START為被設置為1,ST位自動設置為0。如果檢測到啟動條件,并且SDA輸出狀態的內部電平和SDAn線路上的電平在ST位為1時匹配,IIC就會識別出,由于ST位已經成功完成了請求,啟動條件已經成功發出。ICCR2的MST和TRS位自動設置為1,IIC處于主發送模式。當TRS位設置為1時,ICSR2中的TDRE標志也會自動設置為1。

檢查ICSR2中的TDRE標志位是否為1,然后將傳輸值(從地址和R/W#位)寫入ICDRT。傳輸數據寫入ICDRT后,TDRE標志位自動設置為0,數據從ICDRT傳輸到ICDRS后,TDRE標志位再次設置為1。字節后包含從地址和當發送了R/W#位時,TRS位的值會根據發送的R/W#位的值自動更新,選擇主發送或主接收模式。如果R/W#為0,則IIC繼續主傳輸模式。如果此時ICSR2.NACKF標志位為1,表示從設備沒有識別到該地址,或者通信出現錯誤,并向ICCR2.SP位寫入1發出停止條件。如果要傳輸10位地址格式的數據,首先將11110b和從地址的高兩位和W寫入ICDRT作為第一個地址傳輸。然后將從地址低8位寫入ICDRT作為第二個地址傳輸。

確認ICSR2的TDRE標志位為1后,將傳輸數據寫入ICDRT寄存器。IIC自動保持SCLn線路處于低位,直到傳輸數據就緒,發出重啟條件或停止條件。

當所有要傳輸的數據字節寫入ICDRT寄存器后,等待ICSR2中的TEND標志位的值返回1。確認ICSR2的START標志位為1后,將ICSR2的START標志位設置為0。

設置ICCR2中的RS位為1(重啟條件問題請求)。在接收到請求時,IIC發出一個重啟條件。

檢查ICSR2中的START標志位為1后,將傳輸值(從地址和R/W#位)寫入ICDRT。

21.3. EEPROM簡介

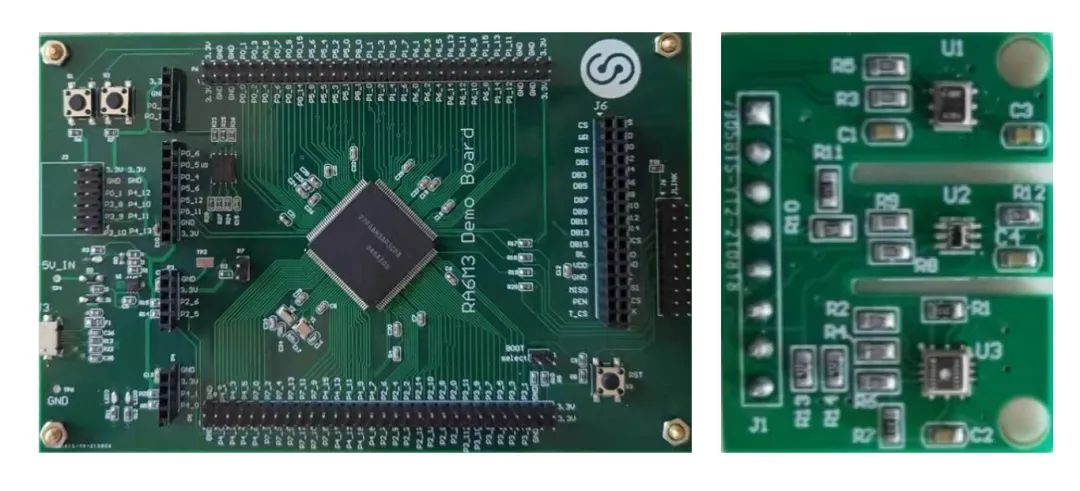

EEPROM是一種掉電后數據不丟失的存儲器,常用來存儲一些配置信息,以便系統重新上電的時候加載。 EEPROM芯片最常用的通訊方式就是I^2^C協議,本小節以EEPROM的讀寫實驗為例子給大家講解RA6M5的I^2^C使用方法。 實驗中RA6M5的I2C外設采用主機模式,分別用作主發送器和主接收器,通過查詢事件的方式來確保正常通訊。

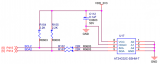

本實驗板中的EEPROM芯片(型號:AT24C02)的SCL及SDA引腳連接到了瑞薩RA6M5對應的I2C引腳中,結合上拉電阻,構成了I2C通訊總線,它們通過I2C總線交互。EEPROM芯片的設備地址一共有7位,其中高4位固定為:1010 b,低3位則由A0/A1/A2信號線的電平決定,見圖22_12,圖中的R/W是讀寫方向位,與地址無關。

圖 22?12 EEPROM設備地址(摘自《AT24C02》規格書)

按照我們此處的連接,A0/A1/A2均為0,所以EEPROM的7位設備地址是:1010 000b ,即0x50。由于I2C通訊時常常是地址跟讀寫方向連在一起構成一個8位數,且當R/W位為0時,表示寫方向,所以加上7位地址,其值為“0xA0”,常稱該值為I2C設備的“寫地址”;當R/W位為1時,表示讀方向,加上7位地址,其值為“0xA1”,常稱該值為“讀地址”。

EEPROM芯片中還有一個WP引腳,具有寫保護功能,當該引腳電平為高時,禁止寫入數據,當引腳為低電平時,可寫入數據,我們直接接地,不使用寫保護功能。

關于EEPROM的更多信息,可參考其數據手冊《AT24C02》來了解。若您使用的實驗板EEPROM的型號、設備地址或控制引腳不一樣,只需根據我們的工程修改即可,程序的控制原理相同。

-

瑞薩

+關注

關注

37文章

22497瀏覽量

90972 -

I2C

+關注

關注

28文章

1556瀏覽量

131369 -

引腳

+關注

關注

16文章

2112瀏覽量

55804 -

GPIO

+關注

關注

16文章

1330瀏覽量

56293

原文標題:I2C的數據、地址傳輸和響應及瑞薩RA6M5的I2C特性及架構——瑞薩RA系列FSP庫開發實戰指南(65)

文章出處:【微信號:瑞薩嵌入式小百科,微信公眾號:瑞薩嵌入式小百科】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

瑞薩RA系列FSP庫開發實戰指南之瑞薩RA6M5的I2C特性及架構

瑞薩RA系列FSP庫開發實戰指南之瑞薩RA6M5的I2C特性及架構

評論