DRV8376-Q1:三相集成FET電機驅動器的卓越之選

在電機驅動領域,一款性能卓越、功能豐富的驅動器對于系統的高效運行至關重要。今天,我們就來深入探討德州儀器(TI)推出的DRV8376-Q1三相集成FET電機驅動器,看看它是如何在眾多產品中脫穎而出的。

文件下載:drv8376-q1.pdf

一、產品概述

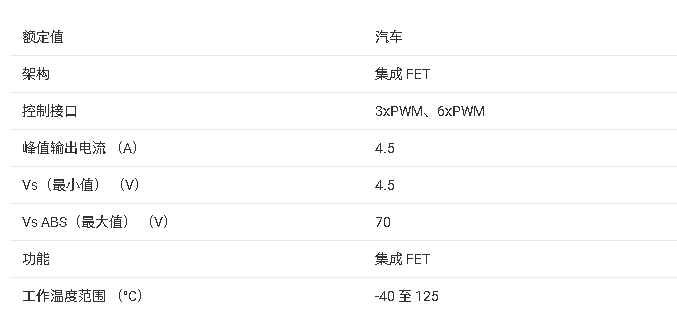

DRV8376-Q1專為驅動4.5V至65V的無刷直流(BLDC)電機而設計,采用VQFN表面貼裝封裝,尺寸僅為6mm × 5mm,集成度高,能有效減少系統組件數量、成本和復雜度。它集成了三個半橋MOSFET、柵極驅動器、電荷泵、電流感測放大器和用于外部負載的線性穩壓器,還具備多種保護功能,為電機驅動系統提供了可靠的保障。

二、產品特性亮點

(一)高性能驅動能力

- 寬電壓支持:支持48V系統,工作電壓范圍為4.5V至65V(絕對最大70V),能適應多種不同的電源環境。

- 高PWM頻率:支持高達100kHz的PWM頻率,可實現更精確的電機控制。

- 低導通電阻:在 (T{A}=25^{circ} C) 時,MOSFET導通電阻 (R{DS(ON)}) 僅為400mΩ(高側 + 低側),能有效降低功率損耗。

- 高輸出電流:具備4.5A的峰值輸出電流能力,可滿足大多數電機的驅動需求。

(二)先進的控制與保護特性

- 主動去磁功能:通過主動去磁技術,減少二極管導通損耗,降低功率損耗。

- 逐周期電流限制:可限制相電流,保護電機和驅動器免受過流損壞。

- 低噪聲與快速響應:超低死區時間 (<200 ~ns) 和傳播延遲 (<100 ~ns) ,降低了可聽噪聲,同時提高了電機控制的便捷性和響應速度。

- 低功耗睡眠模式:在 (V{VM}=24 ~V) 、 (T{A}=25^{circ} C) 時,典型電流僅為1.5μA,有效節省能源。

- 多種控制接口:提供6x PWM和3x PWM控制接口,還支持SPI和硬件接口兩種配置方式,滿足不同應用的需求。

- 內置電流感測:無需外部電流感測電阻,簡化了電路設計。

- 豐富的保護功能:集成了電源欠壓鎖定(UVLO)、電荷泵欠壓(CPUV)、過流保護(OCP)、熱警告和關斷(OTW/OTSD)等多種保護功能,通過nFAULT引腳指示故障狀態,并可通過SPI進行可選的故障診斷。

三、產品詳細解析

(一)輸出級

DRV8376-Q1采用三相橋配置的集成NMOS FET,導通電阻僅400mΩ。通過倍壓電荷泵為高側NMOS FET提供合適的柵極偏置電壓,支持100%占空比,內部線性穩壓器為低側MOSFET提供柵極偏置電壓。

(二)控制模式

| 該系列產品提供四種不同的控制模式,以支持各種換相和控制方法。具體模式如下表所示: | MODE Type | MODE_SR Pin (Hardware Variant) | PWM_MODE Bits (SPI Variant) | SR Bits (SPI Variant) | PWM MODE | ASR and AAR Mode |

|---|---|---|---|---|---|---|

| Mode 1 | Connected to AGND | PWM_MODE = 00b | EN_ASR = 0, EN_AAR = 0 | 6x Mode | ASR and AAR Disabled | |

| Mode 2 | Hi-Z | PWM_MODE = 01b | EN_ASR = 1, EN_AAR = 0 | 6x Mode | ASR Enabled and AAR Disabled | |

| Mode 3 | Connected to GVDD with R MODE | PWM_MODE = 10b | EN_ASR = 0, EN_AAR = 0 | 3x Mode | ASR and AAR Disabled | |

| Mode 4 | Connected to GVDD | PWM_MODE = 11b | EN_ASR = 1, EN_AAR = 0 | 3x Mode | ASR Enabled and AAR Disabled |

(三)接口模式

- SPI接口:支持串行通信總線,外部控制器可通過SCLK、SDI、SDO和nSCS引腳與DRV8376-Q1進行數據收發,實現設備設置配置和詳細故障信息讀取。

- 硬件接口:將四個SPI引腳轉換為四個可通過電阻配置的輸入引腳(GAIN、SLEW、MODE_SR和OCP),無需SPI總線,通過簡單的上拉或下拉電阻即可配置常用設備參數,通用故障信息仍可通過nFAULT引腳獲取。

(四)線性穩壓器與電荷泵

- AVDD和GVDD線性穩壓器:集成3.3V和5V線性穩壓器,可為外部電路提供電源,最大可提供30mA的電流輸出。使用時需在相應引腳連接合適的陶瓷電容,以確保穩定的輸出。

- 電荷泵:為高側NMOS FET提供高于VM電源的柵極驅動電壓,支持寬工作電壓范圍和100%占空比。在nSLEEP引腳為低電平或過熱關斷時,電荷泵會關閉。

(五)電流感測放大器

集成三個高性能低側電流感測放大器,用于監測每個半橋支路的電流。放大器增益可通過SPI或硬件接口進行調整,輸出電壓與低側FET電流成正比。

(六)主動去磁功能

通過智能整流功能(主動去磁),減少二極管導通損耗,降低功率損耗。可分為自動同步整流(ASR)模式和自動異步整流(AAR)模式,根據電流方向自動控制MOSFET的導通和關斷。

(七)逐周期電流限制

利用電流感測放大器輸出與ILIMIT引腳電壓進行比較,實現逐周期電流限制。可通過配置ILIMIT引腳電壓調整電流限制閾值,在100% PWM占空比輸入時,可使用內置PWM時鐘確保高側FET正常工作。

(八)保護功能

| 具備多種保護功能,可有效保護設備、電機和系統免受各種故障的影響。不同故障的響應和恢復機制如下表所示: | FAULT | CONDITION | CONFIGURATION | REPORT | H-BRIDGE | LOGIC | RECOVERY |

|---|---|---|---|---|---|---|---|

| VM undervoltage (RESET) | V VM < V UVLO | - | - | Hi-Z | Disabled | Automatic: V VM > V UVLO_R CLR_FLT, nSLEEP Reset Pulse (RESET bit) | |

| GVDD undervoltage (RESET) | V GVDD < V GVDD_UV | - | - | Hi-Z | Disabled | Automatic: V GVDD > V GVDD_UV_R CLR_FLT, nSLEEP Reset Pulse (RESET bit) | |

| AVDD undervoltage (RESET) | V AVDD < V AVDD_UV | - | - | Hi-Z | Disabled | Automatic: V AVDD > V AVDD_UV_R CLR_FLT, nSLEEP Reset Pulse (RESET bit) | |

| Charge pump undervoltage (VCP_UV) | V CP < V CPUV | - | nFAULT | Hi-Z | Active | Automatic: V VCP > V CPUV CLR_FLT, nSLEEP Reset Pulse (VCP_UV bit) | |

| OverVoltage Protection (OVP) | V VM > V OVP | OVP_MODE = 0b | None | Active | Active | No action (OVP Disabled) | |

| OVP_MODE = 1b | FAULT | Hi-Z | Active | Automatic: V VM < V OVP CLR_FLT, nSLEEP Reset Pulse (OVP bit) | |||

| Overcurrent Protection (OCP) | I PHASE > I OCP | OCP_MODE = 00b | nFAULT | Hi-Z | Active | Latched: CLR_FLT, nSLEEP Reset Pulse (OCP bits) | |

| OCP_MODE = 01b | nFAULT | Hi-Z | Active | Retry: t RETRY CLR_FLT, nSLEEP Reset Pulse (OCP bits) | |||

| OCP_MODE = 10b | nFAULT | Active | Active | Report only: CLR_FLT, nSLEEP Reset Pulse (OCP bits) | |||

| OCP_MODE = 11b | None | Active | Active | No action | |||

| ILIMIT | V ILIMIT > V SO | ILIMFLT_MODE = 0b | None | ILIMIT Mode | Active | Automatic: High side on the next rising edge of INHx Low side on the next rising edge of INLx | |

| ILIMFLT_MODE = 1b | nFAULT | ILIMIT Mode | Active | Automatic: High side on the next rising edge of INHx Low side on the next rising edge of INLx | |||

| SPI Error (SPI_FLT) | SCLK, Parity and ADDR fault | SPIFLT_MODE = 0b | None | Active | Active | No action | |

| SPIFLT_MODE = 1b | nFAULT | Active | Active | Report only: CLR_FLT, nSLEEP Reset Pulse (SPI_FLT bit) | |||

| OTP Error (OTP_ERR) | OTP reading is erroneous | - | nFAULT | Hi-Z | Active | Latched: Power Cycle, CLR_FLT | |

| Thermal warning (OTW) | T J > T OTW | OTW_MODE = 0b | None | Active | Active | No action | |

| OTW_MODE = 1b | nFAULT | Active | Active | Automatic: T J < T OTW – T OTW_HYS CLR_FLT, nSLEEP Pulse (OTW bit) | |||

| Thermal shutdown (OTSD) | T J > T TSD | - | nFAULT | Hi-Z | Active | Automatic: T J < T TSD – T TSD_HYS |

四、應用與實現

(一)典型應用

DRV8376-Q1可廣泛應用于無刷直流(BLDC)電機模塊、HVAC電機、辦公自動化機器、工廠自動化和機器人、無線天線電機、無人機等領域。

(二)設計要點

- 電源供應:合理選擇電源電壓和電容,確保電源穩定。建議使用適當的本地大容量電容,以滿足電機系統的高電流需求,同時注意電容的電壓額定值應高于工作電壓。

- 電流限制設置:通過ILIMIT引腳設置逐周期電流限制,可使用數字 - 模擬轉換器或電阻分壓器來設置ILIMIT引腳電壓。在設置電流限制時,需根據實際應用需求和電流感測放大器的參數進行計算。

- 布局設計:遵循布局指南,將大容量電容放置在靠近電機驅動器的位置,以減少高電流路徑的距離;使用盡可能寬的金屬走線和多個過孔連接PCB層,以降低電感;將小值電容(如電荷泵、GVDD、AVDD和VREF電容)放置在靠近設備引腳的位置;對PGND和AGND進行分區接地,以減少噪聲耦合和EMI干擾;將設備的散熱墊焊接到PCB頂層接地平面,并使用多個過孔連接到大面積底層接地平面,以提高散熱性能。

- 熱管理:注意設備的功率損耗和熱性能,避免設備因過熱而進入熱關斷狀態。可通過合理的PCB設計和散熱措施(如散熱片)來降低設備溫度。

五、總結

DRV8376-Q1三相集成FET電機驅動器憑借其高性能、豐富的功能和靈活的配置方式,為電機驅動系統提供了優秀的解決方案。無論是在性能要求較高的工業應用中,還是在對功耗和尺寸有嚴格要求的消費電子領域,DRV8376-Q1都能展現出卓越的表現。作為電子工程師,在設計電機驅動系統時,不妨考慮這款出色的驅動器,相信它會為你的設計帶來意想不到的效果。

你在使用DRV8376-Q1或其他電機驅動器的過程中,遇到過哪些有趣的問題或挑戰呢?歡迎在評論區分享你的經驗和見解。

-

電機驅動器

+關注

關注

16文章

869瀏覽量

66607 -

無刷直流電機

+關注

關注

61文章

744瀏覽量

49295

發布評論請先 登錄

DRV8376-Q1:三相集成FET電機驅動器的卓越之選

DRV8376-Q1:三相集成FET電機驅動器的卓越之選

評論