1 I2C簡(jiǎn)介

I2C(Inter-Integrated Circuit)是一種由飛利浦半導(dǎo)體(現(xiàn)為恩智浦半導(dǎo)體)在1980年代初開發(fā)的同步、串行、半雙工的總線型通信協(xié)議。主要用于近距離(同一塊印刷電路板(PCB)上的集成電路(IC)之間)、低速(注:標(biāo)準(zhǔn)模式100K,快速模式400K,高速模式3.4M)的芯片之間的通信。

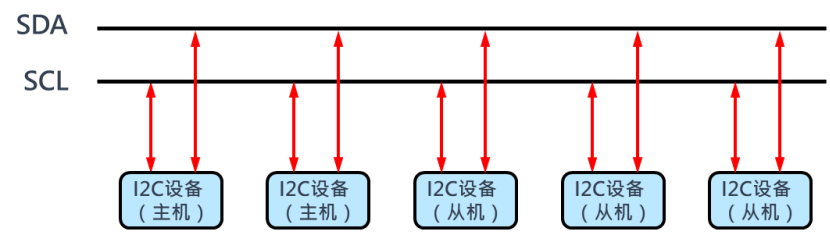

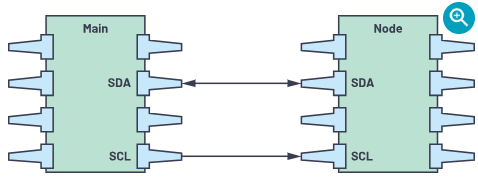

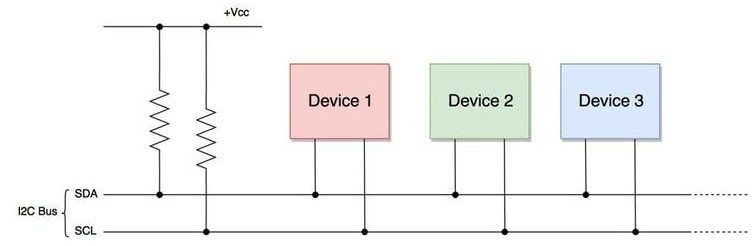

I2C總線有兩根信號(hào)線,一根數(shù)據(jù)線SDA用于收發(fā)數(shù)據(jù),一根時(shí)鐘線SCL用于通信雙方時(shí)鐘的同步。I2C總線是一種多主機(jī)總線,連接在I2C總線上的器件分為主機(jī)和從機(jī),主機(jī)有權(quán)發(fā)起和結(jié)束一次通信,而從機(jī)只能被主機(jī)呼叫。每個(gè)連接到I2C總線上的器件都有一個(gè)唯一的地址(7-bit)。主機(jī)通過I2C設(shè)備的地址來選擇從機(jī)。

2 I2C的三態(tài)門電路

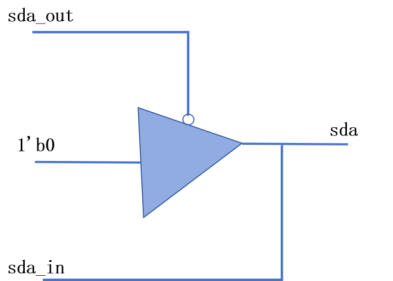

信息雙向傳輸(方向?yàn)閕nout)的時(shí)候需要使用三態(tài)門電路。FPGA內(nèi)部三態(tài)門結(jié)構(gòu):

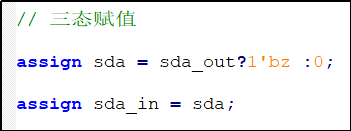

當(dāng)sda_out為1時(shí),sda被設(shè)置為高阻態(tài)(1'bz),即此時(shí)sda由外部設(shè)備(或上拉電阻)控制。當(dāng)sda_out為0時(shí),sda被驅(qū)動(dòng)為0。這種設(shè)計(jì)符合I2C協(xié)議的開漏輸出特性:I2C設(shè)備只能將數(shù)據(jù)線拉低(輸出0)或釋放(輸出高阻,由上拉電阻拉高)。因此,這個(gè)三態(tài)設(shè)置實(shí)現(xiàn)了I2C數(shù)據(jù)線的雙向通信:既可以輸出數(shù)據(jù)(拉低),也可以輸入數(shù)據(jù)(釋放總線并讀取)。具體的Verilog實(shí)現(xiàn)如下:

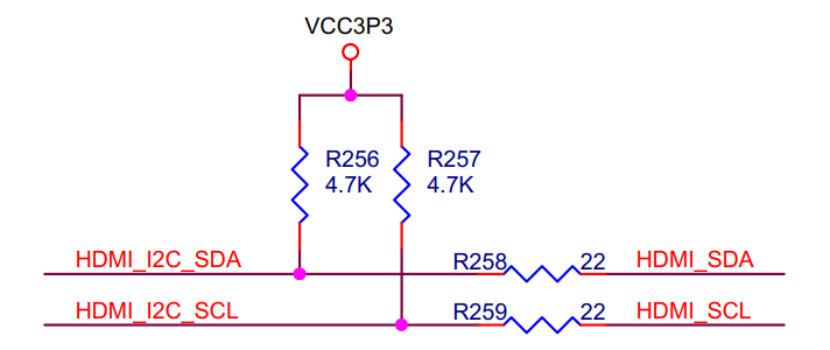

所以FPGA和外設(shè)之間要有個(gè)上拉電阻,如下是DE10-Nano的相關(guān)電路圖:

3 I2C協(xié)議的開始與結(jié)束信號(hào)

開始條件為當(dāng)SCLK(時(shí)鐘腳)保持在高電平時(shí), SDIN(數(shù)據(jù)腳)從高到低,接著會(huì)開始進(jìn)行地址與數(shù)據(jù)傳輸;停止的條件是被定義成在 SCLK 在高電平時(shí), SDIN 有一個(gè)低到高轉(zhuǎn)換:

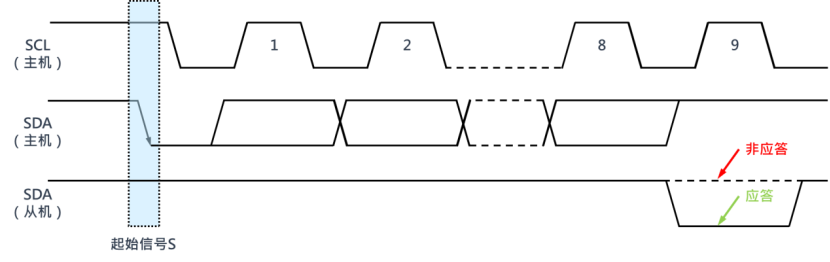

4 I2C協(xié)議的字節(jié)傳送與應(yīng)答

I2C總線通信時(shí)每個(gè)字節(jié)為8位長(zhǎng)度,數(shù)據(jù)傳送時(shí),先傳送最高位,后傳送低位,發(fā)送器發(fā)送完一個(gè)字節(jié)數(shù)據(jù)后,接收器必須發(fā)送1位應(yīng)答位(應(yīng)答:低電平"0";非應(yīng)答:沒接收到數(shù)據(jù)或者接收器不想應(yīng)答,就保持高電平"1")來回應(yīng)發(fā)送器,即一幀共有9位。

5 I2C協(xié)議的同步信號(hào)

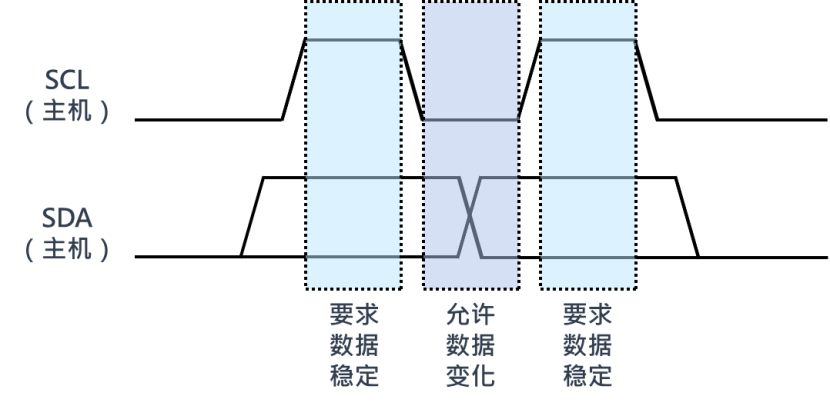

I2C總線在進(jìn)行數(shù)據(jù)傳送時(shí):

時(shí)鐘線SCL為低電平時(shí),發(fā)送器向數(shù)據(jù)線上發(fā)送1-bit數(shù)據(jù),在此期間數(shù)據(jù)線上的信號(hào)允許變化;

時(shí)鐘線SCL為高電平時(shí),接收器從數(shù)據(jù)線上讀取1-bit數(shù)據(jù),在此期間數(shù)據(jù)線上的信號(hào)不允許發(fā)生變化,必須保持穩(wěn)定。

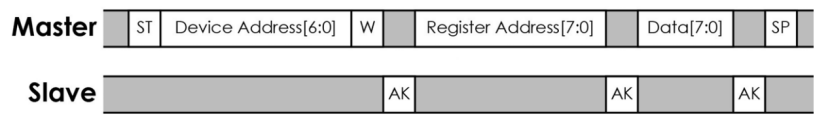

6 I2C協(xié)議的寫操作

主機(jī)先產(chǎn)生一個(gè)起始信號(hào)ST,再由主機(jī)發(fā)送出欲控制的器件地址Device Address[6:0],再加上 1 位的 W/R 讀寫位(設(shè)定為 0)。從機(jī)收到主機(jī)發(fā)送出8 位信號(hào)后,會(huì)回應(yīng)一個(gè) ACK 信號(hào);接著送出寄存器地址Register Address[7:0](有的寄存器地址是16位,則可分兩次發(fā)送),從機(jī)收到主機(jī)發(fā)送出8 位信號(hào)后,會(huì)回應(yīng)一個(gè) ACK 信號(hào);接著送出 8 位數(shù)據(jù) Data[7:0],從機(jī)收到主機(jī)發(fā)送出8 位信號(hào)后,會(huì)回應(yīng)一個(gè)ACK 信號(hào)。傳輸完成后,會(huì)從主機(jī)送出停止信號(hào)SP。則完成了將數(shù)據(jù) Data[7:0] 寫入 Device Address[6:0] 設(shè)備中的 Register Address[7:0] 寄存器中:

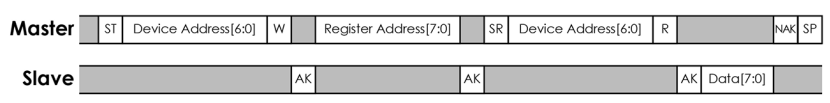

7 I2C協(xié)議的讀操作

主機(jī)先產(chǎn)生一個(gè)起始信號(hào)ST,再由主機(jī)發(fā)送出欲控制的器件地址Device Address[6:0],再加上 1 位的 W/R 讀寫位(設(shè)定為 0)。從機(jī)收到主機(jī)發(fā)送出8 位信號(hào)后,會(huì)回應(yīng)一個(gè) ACK 信號(hào);接著送出寄存器地址Register Address[7:0],從機(jī)收到主機(jī)發(fā)送出8 位信號(hào)后,會(huì)回應(yīng)一個(gè) ACK 信號(hào);接著主機(jī)重新送出開始信號(hào)SR(restart),再由主機(jī)發(fā)送出欲控制的器件地址DeviceAddress[6:0],再加上 1 位的 W/R 讀寫位(設(shè)定為 1)。從機(jī)收到主機(jī)發(fā)送出8 位信號(hào)后,會(huì)回應(yīng) 一個(gè) ACK 信號(hào)。接著讀取 8 位數(shù)據(jù) Data[7:0],主機(jī)收到8 位信號(hào)后發(fā)送一個(gè)NACK給從機(jī),通知從機(jī)主機(jī)不再需要更多的數(shù)據(jù),最后從主機(jī)送出停止信號(hào)SP:

-

FPGA

+關(guān)注

關(guān)注

1663文章

22486瀏覽量

638634 -

通信協(xié)議

+關(guān)注

關(guān)注

28文章

1094瀏覽量

42315 -

接收器

+關(guān)注

關(guān)注

15文章

2651瀏覽量

77459 -

I2C總線

+關(guān)注

關(guān)注

8文章

422瀏覽量

63481

原文標(biāo)題:4-DE10-Nano的HDMI方塊移動(dòng)案例——I2C通信協(xié)議

文章出處:【微信號(hào):友晶FPGA,微信公眾號(hào):友晶FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

i2c通信協(xié)議

I2C通信協(xié)議簡(jiǎn)介

I2C總線通信協(xié)議的相關(guān)資料下載

SPI、I2C、UART串行總線協(xié)議

I2C通信協(xié)議應(yīng)該如何學(xué)習(xí)

i2c和spi通信協(xié)議的概念與區(qū)別 I2C/SPI總線通信協(xié)議你搞懂沒有

I2C通信協(xié)議:了解I2C Primer、 PMBus和SMBus

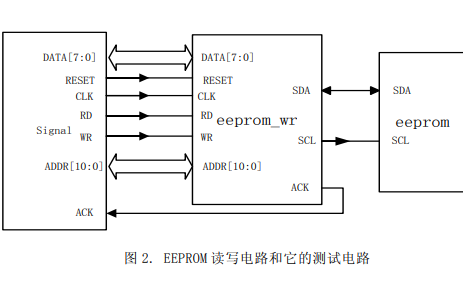

基于FPGA的I2C通信協(xié)議設(shè)計(jì)

基于FPGA的I2C通信協(xié)議設(shè)計(jì)

評(píng)論