1.引言

嵌入式微處理器應用系統(tǒng)是一種面向應用、功能定制、資源受限、響應要求高、性能穩(wěn)定、無自舉開發(fā)能力,由硬件和軟件兩部分構成的專用計算機系統(tǒng),其在日常生活中、工業(yè)生產(chǎn)中、國防領域中都得到了廣泛的應用。但是嵌入式微處理器系統(tǒng)往往工作環(huán)境比較復雜,一般情況下都存在自然因素或人為因素產(chǎn)生的電磁干擾,各種干擾通過一定的途徑進入系統(tǒng)或測量通道,對系統(tǒng)產(chǎn)生一定的干擾,而且隨著系統(tǒng)軟件規(guī)模的增加,系統(tǒng)運行不穩(wěn)定的現(xiàn)象愈來愈嚴重,因此,可靠性已成為衡量嵌入式微處理器系統(tǒng)性能優(yōu)劣的一個重要因素。

在某系統(tǒng)工程設計中,由于需要測量和監(jiān)控的數(shù)據(jù)點數(shù)量眾多,對此,我們大量采用了微處理器分機監(jiān)控電路進行數(shù)據(jù)的采集和數(shù)據(jù)通信。本文主要對如何提高系統(tǒng)的可靠性進行了分析論證,并在此基礎上闡述了提高各分機工作穩(wěn)定性所采取的具體措施。

2.系統(tǒng)組成與工作要求

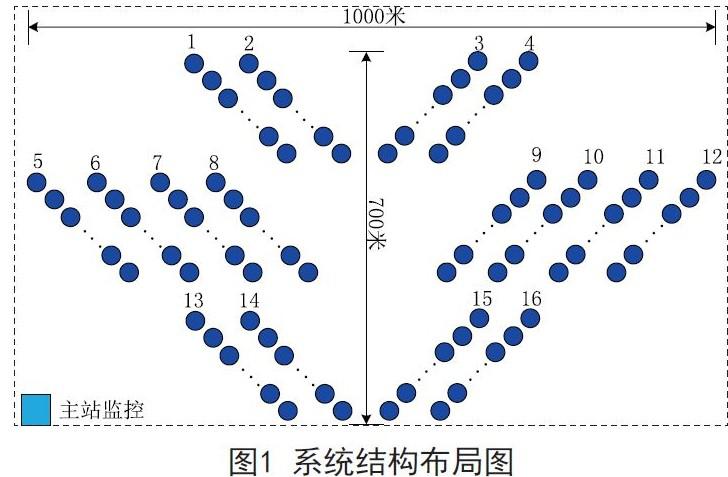

系統(tǒng)的監(jiān)測點分散在直徑約一千米的近似圓形范圍內,呈放射狀。監(jiān)測點總共劃分為16組,每組378個子節(jié)點,總數(shù)量有六千多個,主站監(jiān)控通過通信網(wǎng)絡對所有子節(jié)點進行統(tǒng)一管理,系統(tǒng)結構見圖1.

每個子節(jié)點需要進行7路模擬電壓的采集計算、1路模擬電壓控制輸出、3路開關量的控制。主站監(jiān)控每3秒完成一次對所有子節(jié)點的巡檢,收集所有的測量數(shù)據(jù)和發(fā)送控制參量。

由于監(jiān)測點存在強微波能量輻射,并且工作區(qū)域位于我國西北地區(qū),晝夜環(huán)境溫差較大。同時,系統(tǒng)要求除去每月一天的停機維護外,其余時間均正常加電工作,子節(jié)點監(jiān)控電路允許有3%的失效率。

這些外在的環(huán)境因素和工作時長對系統(tǒng)的工作穩(wěn)定性提出了非常嚴格的要求,這也使得系統(tǒng)的關鍵部分-微處理器電路的可靠性面臨著極為嚴峻的考驗。因此,在系統(tǒng)的初期研制開發(fā)的過程中,必須重視可靠性分析和設計,否則整個系統(tǒng)將無法正常工作,不能實現(xiàn)目標設計功能。

3.系統(tǒng)可靠性分析與設計

從功能上劃分來看,系統(tǒng)由子節(jié)點分機監(jiān)控電路、通信網(wǎng)絡、電源供給網(wǎng)絡、主站監(jiān)控四部分組成,從對系統(tǒng)任務功能的影響來看,它們均與系統(tǒng)功能直接相關。它們的任一部分失效,就會導致整個系統(tǒng)失效,因此稱它們?yōu)橄到y(tǒng)的主要分機。針對系統(tǒng)工作的地理位置、外在電磁環(huán)境特點、目前現(xiàn)有商業(yè)技術的成熟度,以及系統(tǒng)的總體性能要求,系統(tǒng)的可靠性模型建立為串聯(lián)模型,可靠性指標的分配采用綜合因子評定法確定加權因子,為使系統(tǒng)分配的可靠性指標合理可行,我們主要考慮了各分機系統(tǒng)的重要因子、復雜因子、維修因子、技術成熟因子、環(huán)境因子、元器件質量因子、軟件應用程度因子等因素。根據(jù)這七個主要影響可靠性的因素,利用可靠性分析軟件IETM反復進行MTBF參數(shù)的計算與分配,最終獲得了一個最佳平衡點數(shù)據(jù)。

系統(tǒng)的靠性設計遵循以下設計準則:

a.簡化設計:盡量簡化系統(tǒng)配置,減少硬件和軟件的數(shù)量和規(guī)模。

b.繼承性和優(yōu)化設計:最大限度并合理地采用已經(jīng)驗證或成熟的硬件、軟件技術;支持對提高產(chǎn)品可靠性有利的技術進步,但新技術必須經(jīng)過驗證。

c.元器件選用:選用滿足工程質量等級的元器件,努力減少器件型號、規(guī)格和生產(chǎn)廠,進行老煉篩選。

d.冗余和容錯設計:采用充分、合理的硬件和軟件的冗余和容錯設計;盡力消除單點故障;對技術上確難消除的單點故障必須通過設計降低其失效率,使之達到可接受的程度。

e.耐環(huán)境設計:實施硬件的環(huán)境影響分析和環(huán)境防護設計。

f.余量和降額設計:按標準和規(guī)范的要求開展非電子產(chǎn)品的安全裕度設計,元器件降額使用,電路容差的分析和設計。

g.采用有效的設計技術和方法,提高軟件程序的健壯性,選擇易于編寫、校正和修改的程序結構,采用模塊化程序設計方法。

4.系統(tǒng)的硬件/軟件抗干擾設計

作為系統(tǒng)的關鍵主體部分-微處理器電路,其抗干擾設計是一項綜合性設計,采取硬件措施雖然可有效提高監(jiān)控控制系統(tǒng)的抗干擾能力,但過多的硬件本身就降低了系統(tǒng)的可靠性,尤其是有源器件。因而電路的設計要“軟”、“硬”兼施,提高系統(tǒng)的防護和容錯能力,從而提高分機監(jiān)控系統(tǒng)的可靠性。

4.1 硬件方面

按照設計要求和目的,主要從以下幾個方面來提高系統(tǒng)硬件的可靠性。

1)元器件的選用上:一是根據(jù)整機的具體布局、及整機在最高溫度下元器件工作的正常性,來考慮選用合適的元器件。

二是系統(tǒng)一定要采用質量高、性能穩(wěn)定、應用成熟的元器件。三是結合系統(tǒng)的使用年限、所處位置、頻率范圍、所處的干擾脈沖強弱等因素等,選擇在性能、可靠性較高,具有特殊要求的元器件。四是在選擇CPU和外圍器件尤其是速度較慢的外設芯片時,要考慮兩者的速度匹配問題及元器件的品級(如民用級、工業(yè)級還是軍品級),在軟件編程時應特別注意速度匹配問題。

2)印制板設計上:從減小輻射干擾的角度出發(fā),選用多層板。內層分別做電源層、接地層。對信號形成均勻的接地面,加大信號線和接地面間的分布電容,抑制其向空間輻射的內力,供電層和地層最好緊鄰,以增大電源與地之間的分布電容。電源線、地線、印制板走線對高頻信號應保持低阻抗。

3 )設計良好的接地系統(tǒng)。接地不良時,將形成明顯的干擾。防止地線干擾主要三種形式:一是堅持一點接和多點接地的應用原則。在低頻電路中,電線和元器件之間的電感干擾并不多,多采用一點接地;在高頻電路中,布線和元器間的電感干擾以及分布電容會造成各地線之間的偶合,應采用多點接地。二是采用數(shù)字地與模擬地的連接原則。芯片數(shù)字邏輯接地端和模擬信號的接地端應分別接地,在一個芯片上有兩種不同的接地端也應分別接地,然后匯總。

4)電源的抗干擾措施。電源在向系統(tǒng)供電時,也將其噪聲耦合到系統(tǒng)電源上。

為了抑制電網(wǎng)電壓的波動,可在交流電源輸入端加上電源濾波器,讓電源頻率附近的頻率成分通過而使高于此頻率的成分很大衰減,防止由于干擾所產(chǎn)生的電容效應進入到系統(tǒng)內部。二是系統(tǒng)內部通常需要不同的幾種直流電源,為減少公共阻抗的相互偶合和單個電路故障的有效保護,應采用高質量的集成穩(wěn)壓電路進行單獨供電。此外,還應當采用直流開關電流,保證獨立電壓輸出,對直流電流起著較好的初、次級隔離作用。

4.2 軟件方面

1)開機自檢技術

系統(tǒng)在加電在開啟后,首先應對系統(tǒng)內部的軟件逐一的進行狀態(tài)檢測,如內部RAM,SFR及EPROM,I/O芯片等進行故障檢查和診斷,并能給出故障部位,當各項檢查正常后,程序才可以繼續(xù)執(zhí)行。設置自檢程序是提高測控系統(tǒng)可靠性的有效方法之一。

2)指令冗余技術

當系統(tǒng)受到干擾出現(xiàn)錯誤時,程序會在地址空間內出錯,破壞程序計數(shù)器PC的狀態(tài)。程序若“跑飛”到三字節(jié)指令,出錯率將會更大。所以,應采用指令冗余技術,即在系統(tǒng)內的關鍵地方人為插入一些單字節(jié)的空操作指令,通常是在雙字節(jié)指令和三字節(jié)指令后插入兩個字節(jié)上的NOP空指令。插入后,即使“亂飛”程序飛到操作數(shù)上,由于空操作指令NOP的存在,也根本地避免了后面的指令被當作操作數(shù)執(zhí)行,程序將會自動地納入到正軌上來。

此外,對程序流向起重要作用的指令如RET,RETI,LCALL,LJMP,JC等,在其之前插入兩條NOP指令也可將出錯程序納入正軌。

3)軟件陷阱技術

如果“跑飛”程序進入到非程序區(qū),那么,上文所述的指令冗余技術便起不到任何作用,此時,可通過設置軟件陷阱來攔截“跑飛”程序并將其引向指定位置,再進行處理。軟件陷阱通常裝在下面四種地方:一是未使用的中斷向量區(qū);二是未使用的大片ROM區(qū);三是表格,為了不破壞其連續(xù)性,一般把軟件陷阱安排在表格的最后;四是程序區(qū),軟件陷阱一般安排在程序的斷點處,如LJMP,RET等。

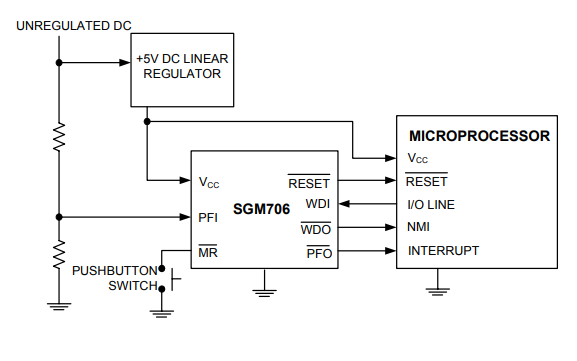

4)軟件“看門狗”技術

如果失控的程序進行死循環(huán),通常使用“看門狗”技術使其脫離死循環(huán)。系統(tǒng)通過不間接地檢測程序循環(huán)運行時間,若發(fā)現(xiàn)程序循環(huán)運行超過最大的循環(huán)運行時間,則會認定系統(tǒng)陷入“死循環(huán)”.“看門狗”技術可使程序返回到程序的入口地址,使系統(tǒng)重新納入到正常運行軌道,它可由軟件實現(xiàn),也可由硬件實現(xiàn)。任務切分的時候應充分考慮到任務的執(zhí)行最大時間應該小于看門狗結束時間。

5)采用μC/OS-II嵌入式操作系統(tǒng)

μC/OS-II自1992年發(fā)布以來,已經(jīng)被移植到幾乎所有嵌入式應用類CPU上,該操作系統(tǒng)是經(jīng)過很多實際應用驗證并改進的,其內核穩(wěn)定可靠,因此,只要分機處理器硬件不出現(xiàn)故障,則操作系統(tǒng)程序就可以保證正常運行,其它子任務程序在操作系統(tǒng)的統(tǒng)一調度下,也可以實現(xiàn)穩(wěn)定的運行。因此相比沒有操作系統(tǒng)的單循環(huán)式的前后臺程序,采用了嵌入式操作系統(tǒng)的分機監(jiān)控,其軟件程序的穩(wěn)定性有著質的改變。

5.系統(tǒng)通信方式與構成

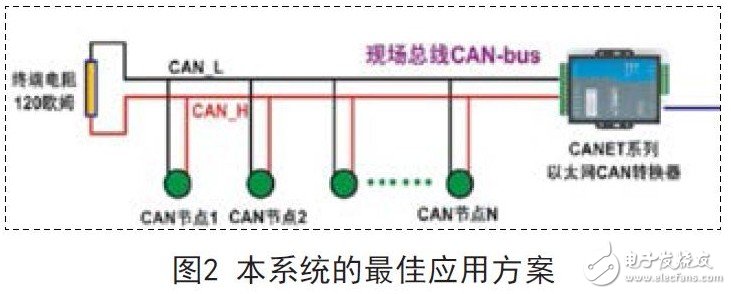

通信網(wǎng)絡負責子節(jié)點與主站監(jiān)控之間的數(shù)據(jù)交互,如果通信網(wǎng)絡不能正常的工作,即使分機監(jiān)控可靠性再高,系統(tǒng)也無法實現(xiàn)既定功能。面對數(shù)量眾多的測量節(jié)點,如果采用常規(guī)的點對點式通信進行數(shù)據(jù)傳輸,將導致大量的硬件接口在主站監(jiān)控點集中匯總,其規(guī)模是非常龐大且復雜的,這將大大降低系統(tǒng)工作可靠性,也增加了后續(xù)維護工作的難度。針對分機監(jiān)控系統(tǒng)特點,這里采用現(xiàn)場總線(CAN)通信網(wǎng)絡。其特點是可以在一對傳輸線上掛接多個通信節(jié)點,可大大減少硬件接口的數(shù)量,降低通信網(wǎng)絡的硬件結構復雜程度是本系統(tǒng)的最佳應用方案,見圖2.

主站與各節(jié)點之間通過31個以太網(wǎng)-CAN轉換模塊進行數(shù)據(jù)通信,每個模塊有2組CAN總線,可掛接200個分機監(jiān)控子節(jié)點。為了保證傳輸數(shù)據(jù)不會被干擾,信號傳輸介質全部采用光纖,子節(jié)點以及以太網(wǎng)-CAN轉換模塊首先通過電光轉換器件把電信號轉為光信號,再通過光纜進行長距離傳輸。由于光纖采用非金屬介質材料,它不會與其它信號產(chǎn)生感應耦合,使光纖對外部電磁干擾有完全的免疫力,可實現(xiàn)高可靠性通信。同時,因為光信號被完善地限制在光纖結構中,任何泄漏的輻射都被外包材料所吸收,故能提供高度的數(shù)據(jù)保密性。

6.結束語

綜上所述,微處理器應用系統(tǒng)的可靠性在很大程度上都取系統(tǒng)內的抗干擾技術應用。其可靠性設計是一個綜合性、經(jīng)驗性較強的問題,是應用系統(tǒng)能否成功應用的關鍵。嚴格意義上來說,系統(tǒng)的硬件抗干擾是主動的,而軟件抗干擾只是一個補充。可見,只有結合微處理器系統(tǒng)實際特點,分析干擾源,采用硬件與軟件相結合的方法,不斷地完善系統(tǒng)監(jiān)控程序,才能夠在保證微處理器的有效性、控制精度、控制功能的基礎上,大力提高系統(tǒng)的抗干擾性能,確保應用系統(tǒng)的可靠運行。

-

嵌入式

+關注

關注

5198文章

20449瀏覽量

334079 -

監(jiān)控

+關注

關注

6文章

2382瀏覽量

59427 -

微處理器

+關注

關注

11文章

2431瀏覽量

85852

發(fā)布評論請先 登錄

基于微處理器的低壓監(jiān)控應用電路

低功耗微處理器監(jiān)控器SP813M電子資料

低功耗微處理器監(jiān)控器SP708電子資料

低功耗微處理器監(jiān)控器SP706電子資料

低功耗微處理器監(jiān)控電路MAX16021相關資料分享

低功耗微處理器監(jiān)控電路MAX16020相關資料分享

低功耗微處理器監(jiān)控電路MAX16016相關資料推薦

高可靠性掉電保護電路設計

SGM706微處理器監(jiān)控電路的數(shù)據(jù)手冊免費下載

如何提高微處理器分機監(jiān)控電路系統(tǒng)的可靠性

如何提高微處理器分機監(jiān)控電路系統(tǒng)的可靠性

評論