高性能 ISO/IEC 14443 A/B 前端 MFRC631 詳細解析

引言

在當今的電子設備領域,近場通信(NFC)技術的應用愈發廣泛,從移動支付到門禁系統,NFC 為我們的生活帶來了極大的便利。NXP 推出的 MFRC631 作為一款高性能的 ISO/IEC 14443 A/B 前端芯片,在 NFC 應用中發揮著重要作用。本文將對 MFRC631 進行全面解析,涵蓋其基本特性、功能模塊、寄存器配置以及應用設計等方面,希望能為電子工程師們在實際設計中提供有價值的參考。

文件下載:MFRC63102HN,151.pdf

一、MFRC631 概述

MFRC631 是一款經濟高效的 NFC 前端芯片,專為支付應用設計。它支持多種操作模式,包括 ISO/IEC 14443 類型 A 和 MIFARE Classic 通信模式的讀寫操作,以及 ISO/IEC 14443B 模式的讀寫操作。其內部發射器能夠驅動與 ISO/IEC 14443A 和 MIFARE Classic IC 卡及應答器通信的讀寫器天線,無需額外的有源電路。數字模塊則管理完整的 ISO/IEC 14443A 幀和錯誤檢測功能(奇偶校驗和 CRC)。

MFRC631 支持多種 MIFARE 產品,如 MIFARE Classic(1 kB 和 4 kB 內存)、MIFARE Ultralight、MIFARE Ultralight C、MIFARE Plus 和 MIFARE DESFire 等,并且支持 MIFARE 產品系列高達 848 kbit/s 的雙向傳輸速度。此外,它還支持 ISO/IEC 14443B 讀寫器通信方案的第 2 層和第 3 層(除防沖突功能外),防沖突功能需在主機控制器的固件以及上層實現。

二、特性與優勢

2.1 高性能多協議支持

MFRC631 集成了 NXP ISO/IEC14443 - A 和 Innovatron ISO/IEC14443 - B 知識產權許可,支持高達 848 kbit/s 的傳輸速度,能滿足多種應用場景的需求。它不僅支持 ISO/IEC 14443 類型 A、MIFARE Classic 和 ISO/IEC 14443 B 模式,還能通過硬件實現 MIFARE Classic 產品的加密讀寫操作,增強了數據傳輸的安全性。

2.2 低功耗設計

具備低功耗卡檢測功能,可有效降低設備的功耗。同時,它還支持多種靈活高效的節能模式,包括硬關機、待機和低功耗卡檢測模式,有助于延長設備的電池續航時間。

2.3 豐富的接口支持

支持多種主機接口,如 SPI(最高 10 Mbit/s)、I2C - bus 接口(快速模式最高 400 kBd,快速模式 + 最高 1000 kBd)和 RS232 串行 UART(最高 1228.8 kBd,電壓電平取決于引腳電源),方便與不同的主機設備進行連接。此外,還提供了單獨的 I2C - bus 接口用于連接安全訪問模塊(SAM),增強了系統的安全性。

2.4 其他優勢

- 集成 PLL 從 27.12 MHz RF 石英晶體派生系統時鐘,節省了成本。

- 具有 512 字節的 FIFO 緩沖區,可實現最高的事務處理性能。

- 提供 3 V 至 5.5 V(MFRC63102)或 2.5 V 至 5.5 V(MFRC63103)的電源供應范圍,適應不同的電源環境。

- 多達 8 個自由可編程輸入/輸出引腳,增加了設計的靈活性。

三、功能模塊詳解

3.1 中斷控制器

中斷控制器負責處理中斷請求的啟用和禁用,所有中斷都可以通過固件進行配置。固件還可以觸發中斷或清除待處理的中斷請求。芯片實現了兩個 8 位中斷寄存器 IRQ0 和 IRQ1,以及兩個 8 位中斷使能寄存器 IRQ0En 和 IRQ1En。通過設置中斷控制器寄存器中的位 7,可以設置和清除位 0 至 6。

MFRC631 通過在寄存器 Status1Reg 中設置位 IRQ 來指示某些事件,并且如果激活,還會通過引腳 IRQ 發出信號。引腳 IRQ 上的信號可用于利用主機的中斷處理功能來中斷主機,從而實現高效的主機軟件。

3.2 定時器模塊

3.2.1 定時器概述

MFRC631 實現了五個定時器,其中四個定時器(Timer0 至 Timer3)的輸入時鐘可以通過寄存器 T(x)Control 配置為 13.56 MHz、212 kHz(從 27.12 MHz 石英派生)或第五個定時器(Timer4)的下溢事件。每個定時器都實現了一個 16 位寬的計數器寄存器,定時器的重載值在寄存器 T(x)ReloadHi 和 T(x)ReloadLo 中定義。第五個定時器 Timer4 連接到內部 LFO(低頻振蕩器)作為輸入時鐘源,可用于喚醒系統。

3.2.2 定時器模式

- 超時計數器和看門狗計數器:通過設置寄存器 T(x)ReloadValue 并啟動定時器計數,當定時器下溢時,如果在配置的時間間隔內事件未發生,定時器單元將生成中斷請求,通知主機事件未發生。

- 喚醒定時器:Timer4 可在預定義的時間后喚醒系統。在低功耗卡檢測模式下,可設置 T4Control.T4AutoWakeUp 和 T4Control.T4AutoRestart 來激活 Timer4 并自動將系統置于待機狀態。如果檢測到卡,主機通信可以啟動;如果未檢測到卡且 T4Control.T4AutoWakeUp 未設置,MFRC631 將保持全功率運行。

- 秒表:可以測量配置的開始和停止事件之間的時間間隔。通過設置寄存器 T(x)ReloadValueHi 和 T(x)ReloadLo,定時器開始遞減計數,當配置的停止事件發生時,定時器停止計數,主機可以根據定時器間隔計算經過的時間。

- 可編程單次定時器:主機配置中斷和定時器,啟動定時器并等待引腳 IRQ 上的中斷事件。在配置的時間后,中斷請求將被觸發。

- 周期性觸發器:如果設置了位 T(x)Control.T(x)AutoRestart 并激活中斷,在每個定時器周期結束后,將周期性地發出中斷請求。

3.3 非接觸式接口單元

3.3.1 ISO/IEC14443 類型 A 和 MIFARE Classic 通信模式

在該模式下,讀寫器到卡的通信采用 100% ASK、Miller 編碼,傳輸速度為 106 kbit/s 至 848 kbit/s;卡到讀寫器的通信采用子載波負載調制、Manchester 編碼或 BPSK,傳輸速度同樣為 106 kbit/s 至 848 kbit/s。內部 CRC 協處理器根據 ISO/IEC 14443 A 第 3 部分計算 CRC 值,并根據傳輸速度內部處理奇偶校驗生成。

3.3.2 ISO/IEC14443B 功能

讀寫器到卡的通信采用 NRZ、Miller 編碼,傳輸速度為 106 kbit/s 至 848 kbit/s;卡到讀寫器的通信采用子載波負載調制、BPSK 編碼,傳輸速度為 106 kbit/s 至 848 kbit/s。MFRC631 連接到主機后,可管理完整的 ISO/IEC 14443 B 協議。

3.4 主機接口

3.4.1 主機接口配置

MFRC631 支持多種主機接口類型,包括 SPI、I2C、I2CL 和串行 UART。在上電或從掉電恢復后,它會自動重置接口并檢查當前的主機接口類型。通過控制引腳的邏輯電平組合來識別主機接口。

3.4.2 SPI 接口

作為 SPI 通信的從設備,SPI 時鐘 SCK 由主設備生成。數據從主設備到從設備通過 MOSI 線傳輸,從 MFRC631 到主設備通過 MISO 線傳輸。支持高達 10 Mbit/s 的數據速度,NSS 信號用于啟用或禁用 SPI 接口。讀寫數據時,遵循特定的字節順序和地址字節格式。

3.4.3 RS232 接口

內部 UART 接口與 RS232 串行接口兼容,電壓電平在 VSS 和 PVDD 之間。可通過設置寄存器 SerialSpeedReg 中的 BR_T0 和 BR_T1 位來選擇不同的傳輸速度,默認傳輸速度為 115.2 kbit/s。讀寫數據時,遵循特定的幀格式。

3.4.4 I2C - bus 接口

實現了與 NXP Semiconductors I2C 接口規范兼容的接口,支持標準模式、快速模式和快速模式 +。在數據傳輸過程中,遵循特定的數據有效性、起始和停止條件、字節格式和應答規則。支持 7 位尋址,設備地址的高 5 位由 NXP 保留,低 2 位可由用戶自由配置。

3.4.5 SAM 接口

MFRC631 實現了專用的 I2C 或 SPI 接口,可方便地將 MIFARE SAM 集成到應用中。SAM 可作為加密協處理器,與微控制器和讀寫器 IC 進行通信,有效降低協議開銷,提高交易時間性能。

3.4.6 邊界掃描接口

提供符合 IEEE 1149.1 的邊界掃描接口,可通過測試單元對引腳功能進行覆蓋,實現無需物理測試探針的互連測試。支持多種邊界掃描命令,方便對芯片進行測試和編程。

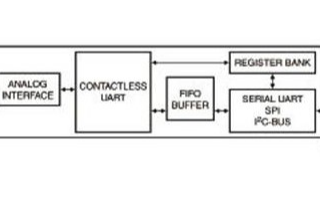

3.5 緩沖區

MFRC631 實現了一個 512 × 8 位的 FIFO 緩沖區,用于緩沖主機和內部狀態機之間的輸入和輸出數據流。可通過寄存器配置 FIFO 的大小(255 字節或 512 字節),并通過相關寄存器獲取 FIFO 的狀態信息,如長度、幾乎滿或幾乎空的警告等。還可以通過設置 FIFOFlush 位清除 FIFO 緩沖區。

3.6 模擬接口和非接觸式 UART

3.6.1 概述

集成的非接觸式 UART 支持外部主機在線處理協議要求的幀和錯誤檢查,最高傳輸速度可達 848 kbit/s。外部電路可連接到通信接口引腳 SIGIN 和 SIGOUT 進行數據調制和解調。

3.6.2 TX 發射器

引腳 TX1 和 TX2 輸出的信號是經包絡信號調制的 13.56 MHz 載波,可直接驅動天線。可通過寄存器 DrvMode 配置信號,通過 TxAmp 設置調制指數。為避免過沖,提供了過沖保護功能,通過兩個定時器 overshoot_t1 和 overshoot_t2 實現。還可通過位生成器對數據流進行編碼。

3.6.3 接收器電路

采用多功能正交接收器架構,具有完全差分信號輸入(RXP 和 RXN)。可配置為實現各種 13.56 MHz 協議的最佳接收性能,接收過程包括多個步驟,如正交解調等。支持單端和差分模式,單端模式下接收靈敏度會降低。

3.6.4 有源天線概念

通過配置相關寄存器,可將 MFRC631 的模擬部分和數字部分分離,實現有源天線概念。外部有源天線電路可連接到 MFRC631 的數字電路,提高系統的靈活性和性能。

3.6.5 符號生成器

用于創建各種協議符號,如 ISO14443 協議中的 SOF 或 EOF 符號。可通過符號定義寄存器和模式寄存器配置符號,每個符號由一組寄存器定義,包括位時鐘和子載波頻率、脈沖類型/長度和包絡類型等。

3.7 內存

3.7.1 內存概述

MFRC631 實現了三種不同的內存:EEPROM、FIFO 和寄存器。上電時,通過自動將 EEPROM 區域的內容復制到寄存器來初始化寄存器。可通過執行 LoadProtocol 命令將 EEPROM 中的默認協議設置復制到寄存器,改變 MFRC631 的行為。讀寫 EEPROM 部分 2 可用于存儲用戶數據或預定義的寄存器設置。FIFO 用作輸入/輸出緩沖區,可提高系統性能。

3.7.2 EEPROM 內存組織

EEPROM 大小為 8 kB,按頁組織,每頁 64 字節。不同的內存區域有不同的用途,如產品信息和配置、寄存器重置、MIFARE Classic 密鑰存儲和寄存器設置協議區域等。

3.7.3 EEPROM 初始化內容 LoadProtocol

EEPROM 在生產時進行初始化,其內容可用于將 MFRC631 的某些寄存器重置為默認設置。通過執行 LoadProtocol 命令,可將 EEPROM 中的寄存器設置復制到相應的寄存器。

3.8 時鐘生成

3.8.1 晶體振蕩器

晶體振蕩器為 MFRC631 提供時鐘,作為載波生成、正交混頻器 I 和 Q 時鐘生成以及同步系統的編碼器和解碼器的時間基準。為獲得最佳性能,建議使用內部振蕩器緩沖器和推薦的電路,以確保時鐘頻率的穩定性和低抖動。

3.8.2 IntegerN PLL 時鐘線

MFRC631 可通過 CLKOUT 引腳提供頻率可配置的時鐘(1 MHz 至 24 MHz),時鐘源為 27.12 MHz 晶體振蕩器。通過兩個分頻器確定輸出頻率,可根據需要配置不同的頻率和分頻比。

3.8.3 低頻振蕩器(LFO)

實現了低頻振蕩器(LFO),Timer4 可配置為使用 LFO 生成的時鐘作為輸入時鐘,用于喚醒系統。LFO 在芯片生產時進行了校準,運行頻率為 16 kHz。如果需要更高的精度,可通過數字狀態機對 LFO 進行微調。

3.9 電源管理

3.9.1 供電概念

MFRC631 由 VDD(電源電壓)、PVDD(焊盤電源)和 TVDD(發射器電源)供電,三者相互獨立。建議使用阻塞電容對這些電源進行緩沖,以提高電源的穩定性。

3.9.2 功率降低模式

- 硬關機:通過將引腳 PDOWN 置為高電平,可實現硬關機,關閉內部 1.8 V 電壓調節器和振蕩器,將輸出引腳切換到高阻抗狀態。

- 待機模式:通過設置寄存器 Command 中的 PowerDown 位為 1 進入待機模式,此時內部電流源關閉,電壓參考和電壓調節器進入待機狀態。退出待機模式時,需清除該位并遵循特定的操作步驟。

- 調制器關閉模式:通過設置寄存器 Control 中的 ModemOff 位為 1,可關閉天線發射器和接收器。

3.9.3 低功耗卡檢測(LPCD)

LPCD 是一種節能模式,分為待機和檢測兩個階段。通過喚醒計數器(WUC)控制待機時間,在檢測階段檢測 I 和 Q 通道的值,并與寄存器中的閾值進行比較。如果超過閾值,將觸發 LPCDIRQ 中斷。

3.9.4 復位和啟動時間

在 PDOWN 引腳施加 10 μs 的高電平可啟動內部復位程序。復位完成且振蕩器進入穩定工作狀態后,芯片即可使用,典型的啟動時間為 2.5 ms。

3.10 命令集

3.10.1 概述

MFRC631 的行為由狀態機控制,通過向命令寄存器寫入命令代碼來執行命令。命令的參數和數據通過 FIFO 緩沖區進行交換。每個命令可通過向命令寄存器寫入新的命令代碼來停止。

3.10.2 命令集概述

提供了多種命令,如空閑命令、低功耗卡檢測命令、加載密鑰命令、MIFARE Classic 認證命令、接收命令、發送命令、收發命令、EEPROM 讀寫命令、加載寄存器命令、加載協議命令等。

3.10.3 命令功能

不同的命令具有不同的功能和執行條件,如空閑命令用于取消當前命令執行,LPCD 命令用于低功耗卡檢測,MFAuthent 命令用于 MIFARE Classic 認證等。在執行命令時,需要根據命令的要求設置相應的參數和寄存器。

四、寄存器配置

4.1 寄存器位行為

根據寄存器的功能,其訪問條件有所不同。主要分為讀/寫(r/w)、動態(dy)、只讀(r)、只寫(w)和保留(RFU)等類型。

4.2 MFRC631 寄存器概述

提供了多個可由主機修改的寄存器,涵蓋了命令控制、主機控制、FIFO 控制、中斷控制、非接觸式接口配置、定時器配置、發射器配置、CRC 配置等多個方面。

4.3 命令配置

通過命令寄存器控制命令的執行,可設置命令的啟動和停止,以及接收器和發射器電路的電源狀態。

4.4 SAM 配置寄存器

HostCtrl 寄存器用于控制接口訪問權限,可設置寄存器的可修改性、總線控制權和 SAM 接口的選擇。

4.5 FIFO 配置寄存器

包括

-

MFRC631

+關注

關注

0文章

3瀏覽量

7107

發布評論請先 登錄

MFRC52202HN1的特性和優勢

CI523兼容FM17550/SKY1311 支持 ISO/IEC 14443 A/B/Mifare 更高速率 通信

ISO/IEC14443標準包括哪幾個部分

如何使用安裝CLRC663plus的CLEV6630B對MFRC630 plus進行評估?

ISO/IEC14443-4 標準協議

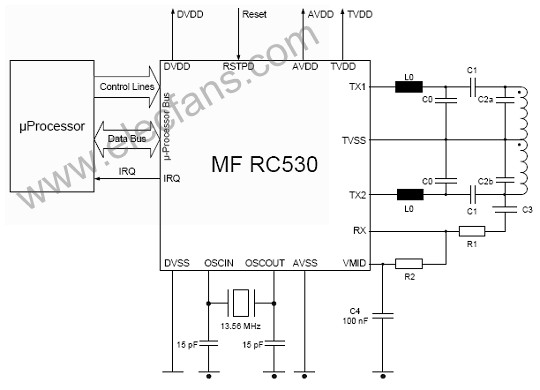

基于MFRC530設計的ISO14443A無接觸讀卡技術

基于ISO14443A協議的RFID模擬前端設計

ISO/IEC_FCD_14443-1

ISO/IEC_FCD_14443-2

ISO/IEC_CD_14443-4

MFRC523性能標準ISO/IEC 14443的A/B的前端產品數據表

高集成讀寫器MFRC523的主要特性及功能分析

高性能 ISO/IEC 14443 A/B 前端 MFRC631 詳細解析

高性能 ISO/IEC 14443 A/B 前端 MFRC631 詳細解析

評論