福晞2025

為方便用戶了解和熟悉「福晞軟件」,我們就軟件的調(diào)試工具進行詳細的講解和說明,以幫助用戶實現(xiàn)高效地開發(fā)和調(diào)試。

福晞軟件提供了一套完整的芯片在線調(diào)試工具,用戶可以通過這一系列的調(diào)試工具,在線觀察芯片內(nèi)部信號的變化。

本工具集提供了多種添加 Debugware IP 的方式,在完整運行福晞流程生成碼流,并成功下載后,通過 Real Time Debug 工具可選擇不同 LA Core,設置不同采樣頻率,不同觸發(fā)條件。最后通過 Waveform 可以方便查看采樣波形。

圖 1-1清晰地描述了整個調(diào)試過程中不同工具的功能以及工具之間的相互依賴關(guān)系。

圖 1-1 福晞軟件調(diào)試流程

福晞軟件在線調(diào)試主要分為以下4個步驟:

(1) 工程添加 Debugware IP;

(2) 運行綜合,布局&布線,生成碼流和下載;

(3) 設置觸發(fā)條件;

(4) 查看波形。

在步驟(1)中,福晞軟件提供了兩種方式幫助用戶在工程中添加 Debugware IP: Debugware UI 手動例化 Debugware IP 和借助 Debug Insert 工具自動添加 Debugware IP。

近期,我們將詳細介紹上述相關(guān)步驟。

添加 Debugware IP

手動例化 Debugware IP

本節(jié)主要描述 Debugware IP 的手動例化使用方法。該 IP 核是一種嵌入式邏輯分析儀(Embedded Logic Analyzer),用于幫助設計人員觀察 FPGA 內(nèi)部信號跳變。采樣信號波形存儲 EMB 中,成功觸發(fā)后可通過 JTAG 接口回讀數(shù)據(jù)。用戶可根據(jù)預設條件獲取對應的波形圖。

Debugware IP 支持以下功能:

動態(tài)配置觸發(fā)條件

支持實時捕獲

支持多種觸發(fā)類型與條件:

(1) 算術(shù)運算

a. 等于(equal)

b. 不等于(not equal)

(2) 邊沿檢測

a. 上升沿(rise)

b. 下降沿(fall)

支持最多 4 個 LA 核

多 LA 核協(xié)同管理

支持多 EMB 擴展,以增加采樣數(shù)據(jù)的位寬與深度

注意

確保設計滿足時序要求;

確保 Debugware IP 實際使用的 EMB 數(shù)量不要超過當前器件可使用 EMB 總數(shù)。

Debugware IP 支持器件:

HME-M7,HME-M5,HME-HR3,HME-HR2,HME-H1,HME-H3,HME-H3P,HME-H7,HME-P0,HME-P1,HME-P2,HME-P3

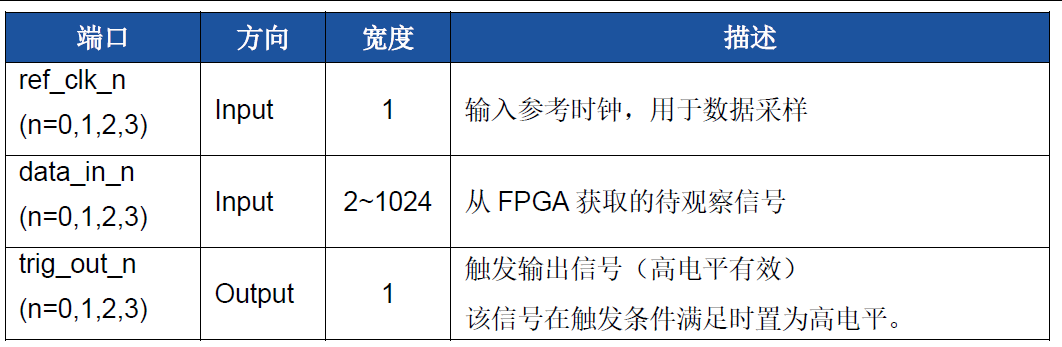

Debugware IP 端口介紹

表 2-1 Debugware IP 端口介紹

Debugware IP 框圖

Debugware IP 由三部分組成:

TAP,LA Manager 和 LA Core,如圖2-1所示。

TAP:JTAG 控制器的調(diào)試接口封裝邏輯(為 JTAG 協(xié)議提供硬件適配層)。

LA Manager:Debugware IP 的中央控制單元,擔任 TAP 模塊與 LA 核之間的橋接樞紐,有且只有一個(1個 LA Manager 可同時控制最多4個 LA 核)。

LA Core:Debugware IP 的執(zhí)行單元;包含兩大核心模塊:觸發(fā)生成模塊(Trigger Generator)和存儲模塊(Storage Module)。

圖 2-1 Debugware IP UI 介紹

Debugware IP 使用介紹

用戶可通過 Debugware 按以下步驟生成 Debugware IP:

步驟 1

按照圖 2-2所示,從Wizard Manager中選擇Debugware(v2.1a)啟動 Debugware IP UI。

圖 2-2 選擇 Debugware IP

步驟 2

用戶可按照圖 2-3,圖 2-4和圖 2-5所示,配置Debugware IP。

圖 2-3 輸入模塊名稱

圖 2-4選擇 LA Core 的數(shù)量(最大值為4)

圖 2-5配置存儲參數(shù)

Trigger Model:設置觸發(fā)模式,可選項為:Single 和 Multiple;選擇 Single 時,Debugware 不支持多窗口觸發(fā)方式;選擇 Multiple 時,支持多窗口觸發(fā)模式。但 Multiple 模式下,窗口個數(shù)設為1時,不等價于 Single 模式。Multiple 模式使用的資源數(shù)量比 Single 模式多。

Data Width:設置 Debugware 使用的 EMB 的數(shù)據(jù)位寬,數(shù)據(jù)位寬的值應該大于等于您要實際觀察信號的數(shù)量;

Memory Depth:設置 Debugware 使用 EMB 的深度,該值大小決定觸發(fā)時采樣的周期數(shù)。

Input DFF Level:設置待觀測信號的打拍個數(shù),范圍0~6。說明:改善增加 Debugware IP 對用戶邏輯性能的影響,值越大影響越小,推薦值為2。

步驟 3

點擊Finish生成 IP RTL 源代碼文件,該文件會被自動加到工程中。然后,您需要在工程中手動例化 Debugware IP。并將需要觀察信號接到 IP 的 data_in_n(n=0,1,2,3) 端口。

生成 IP 源文件時,UI 同時生成以圖 2-3中 Module Name 命名的 *.adf 文件。該文件記錄了 IP 使用的 LA Core 的配置信息:Core 使用的 Clock 名稱、觸發(fā)條件和 IP 使用的存儲信息。在下文第4部分觸發(fā)中,Real Time Debug 工具會加載 adf 文件中的初始觸發(fā)條件。同時,adf 文件會記錄用戶自定義的觸發(fā)條件。

運行流程

所有修改完成后,可依次運行綜合、布局&布線和生成碼流步驟,生成 *.acf 文件。

關(guān)閉調(diào)試

當完成當前調(diào)試過程后,您需要手動在工程源代碼中刪除 Debugware IP 的例化代碼,重新運行流程生成新的 *.acf 文件。

自動添加 Debugware IP

除了上述介紹的手動例化 Debugware IP的方式,福晞軟件還提供了 Debug Insert 工具。Debug Insert 是一款基于福晞綜合網(wǎng)表 *.amv 文件進行調(diào)試的工具。因此,在使用 Debug Insert 工具之前,您需要提前運行綜合,確保生成 *.amv 網(wǎng)表文件。

該工具在正確設置 LA Core 個數(shù)和選擇待觀察的信號后,會自動生成 *.dxc 約束文件。接下來,福晞運行流程時,福晞流程讀取約束文件中 LA Core 的信息,在 *.amv 網(wǎng)表中自動添加 Debugware IP。

因此,該工具可以幫助用戶在工程中自動添加 Debugware IP,這避免了用戶手動修改 RTL 源代碼,簡化了 IP 添加的過程,在一定程度上提高了用戶調(diào)試效率。

啟動 Debug Insert 工具

依次選擇Tools -> Debug Insert;

在Flow Navigator 窗口中, 依次選擇Synthesize->Open Synthesized Design->Debug Insert;

在Project或者Hierarchy窗口中,新建 *.dxc 文件,雙擊 *.dxc 文件打開工具,如圖 2-7。

圖 2-7 Debug Insert 界面

設置 LA Core

在Core Setting頁面,設置 LA Core參數(shù):

Trigger Model:設置觸發(fā)模式,可選項為:Single 和 Multiple;選擇 Single 時,Debugware 不支持多窗口觸發(fā)方式;選擇 Multiple 時,支持多窗口觸發(fā)模式。但 Multiple 模式下,窗口個數(shù)設為1時,不等價于 Single 模式。Multiple 模式使用的資源數(shù)量比 Single 模式多。

Core Name:設置 LA Core 的名稱,名稱需要保持唯一。

Memory Depth:設置 Debugware 使用 EMB 的深度,該值大小決定了觸發(fā)時采樣周期數(shù)。

Input DFF Level:設置待觀測信號的打拍個數(shù),范圍0~6。說明:改善增加 Debugware IP 對用戶邏輯性能的影響,值越大影響越小,推薦值為2。

Clock:在LA Core行Clock列對應單元格雙擊,彈出Search Design對話框如圖 2-8,設置要觀察信號所在時鐘域。未設置 Clock 時,該單元格用紅色標記,并顯示N/A,如上圖 2-7 Debug Insert 界面。

圖 2-8 時鐘選擇

另外,可通過工具欄中?或者右鍵菜單“Remove Core”刪除當前選中 LA Core。

注意

Debug Insert 工具無需設置數(shù)據(jù)位寬,工具會根據(jù)實際選擇信號個數(shù)自動確定;

如果綜合網(wǎng)表中沒有有效時鐘,LA Core 將無法選擇時鐘;

在保存時,如果 Clock 顯示為 N/A(未配置),將不能保存。

選擇觀察信號

Debug Insert 工具提供了兩種添加信號的方式:

在 RTL 中使用MARK_DEBUG宏標記觀察信號(wire 或者 reg)。

使用 Debug Insert UI 對話框選擇福晞綜合 amv 網(wǎng)表中信號。

(1)使用MARK_DEBUG宏

在 RTL 源文件,找到對應的 reg 或者 wire 信號,在信號前添加屬性:(* MARK_DEBUG = “YES” *),然后保存 RTL,如圖 2-9所示。

圖 2-9 MARK_DEBUG 宏

運行綜合成功后,打開 Debug Insert,選擇Create a new debug constraint file。Debug Insert 工具會自動加載 RTL中標記的信號。如圖 2-10:

圖 2-10 LA Core 頁面

如圖 2-10所示,工具會自動根據(jù) MARK_DEBUG 標記的信號所屬時鐘域創(chuàng)建 LA Core。每個時鐘域?qū)粋€ LA Core,同時時鐘域內(nèi)的觀察信號也對應添加到 LA Core 對應的被觀察信號頁面。

在被觀察信號頁面,RTL 中標記的信號和 UI 中手動添加的信號使用不同圖標標記:

代表 RTL 標記,

代表 UI 手動添加,

如下圖 2-11所示:

圖 2-11 MARK_DEBUG 宏添加信號

(2)使用Debug Insert UI對話框

點擊 LA Core 名稱對應的頁面,切換到被觀察信號頁面。在本頁面可通過⊕或者右鍵“Add Nets”打開福晞綜合 .amv 網(wǎng)表中所有 Net 信號集合對話框,如圖 2-12。在本對話框中,依次選擇觀察信號,選擇完成后,點擊OK,選擇信號將被添加到被觀察信號頁面。

圖 2-12 可觀察信號集合

Search Design窗口中,可根據(jù)Net Name進行查找。在該窗口中,Net 列表顯示福晞綜合 .amv 網(wǎng)表中所有的信號信息,表格有以下3列:

Net Name:信號的名稱。

Status:顯示該信號是否已經(jīng)被添加到 LA Core 中,如果已經(jīng)添加,

則以

標記。

Driver Module:顯示該信號的驅(qū)動模塊類型。

生成 *.dxc

在完成 LA Core 設置和選擇完被觀察信號后,可通過

Core 頁面

或者右鍵菜單Generate彈出

Summary對話框,顯示所有配置信息。在Summary對話框中(如圖2-13),選擇Generate,生成 *.dxc 文件,Debugware IP文件和 *.adf 文件。

注意

使用 Debug Insert 工具生成的 adf 文件為:fx_insert_debugware_v2_1,不可修改。

圖 2-13 Summary 對話框

生成 *.dxc 文件后,該文件會自動加入工程,并顯示在福晞軟件的Hierarchy窗口和Project窗口,如圖 2-14所示。編輯已存在 dxc 文件,可通過在 Hierarchy 或者 Project 窗口雙擊 .dxc 文件,打開 Debug Insert 工具。

圖 2-14 Hierarchy 和 Project 窗口

運行流程

經(jīng)過前邊三個小節(jié):

設置 LA Core,選擇觀察信號和生成 *.dxc;已經(jīng)生成了

調(diào)試約束文件 *.dxc 和 *.adf 文件。*.dxc 文件記錄了調(diào)試需要的 LA Core 設置以及需要觀察的信號。 Debugware IP 的添加需要重新編譯工程生成新的 *.acf 文件。

在 Console 窗口打印如下 log 信息,說明流程正常啟動,如圖 2-15。

圖 2-15 Debug Insert 流程 log

關(guān)閉調(diào)試

完成調(diào)試流程后,您可以選擇以下任意一種方式關(guān)閉調(diào)試流程:

在圖 2-14Hierarchy或Project窗口中,選中 *.dxc 文件,在右鍵菜單中選擇Remove From Project,移除 *.dxc 文件;

在圖 2-7Debug Insert界面中,將Enable選項取消勾選。

注意

如圖 2-1所示,由于芯片中有且只有一個 JTAG 模塊,因此工程中不能同時使用手動例化 Debugware IP和自動添加 Debugware IP添加 IP。否則,運行流程時,將會報如下錯:

ERROR : [PLACER 01201] : The cell JTAG_DBWV1 only one in device, so can't place u_debug_u_tap_genblk1_u_jtag.

如果 Placer 報上述錯誤,請檢查您工程中是否同時例化了 IP 并添加了處于 Enable 狀態(tài)的 .dxc 文件。

下載

通過前邊介紹的手動例化 Debugware IP或自動添加Debugware IP方式,生成 *acf 碼流文件后,

您可以通過

或者Tools->Downloader打開下載界面,

如圖3-1所示。選擇對應的 acf 文件,點擊Program按鈕下載碼流至芯片。

圖 3-1 Downloader 界面

(未完待續(xù)……)

-

FPGA

+關(guān)注

關(guān)注

1656文章

22317瀏覽量

631100 -

IP

+關(guān)注

關(guān)注

5文章

1850瀏覽量

155039 -

布線

+關(guān)注

關(guān)注

9文章

817瀏覽量

85977 -

調(diào)試工具

+關(guān)注

關(guān)注

1文章

54瀏覽量

12933

原文標題:福晞?軟件調(diào)試工具介紹:工程添加 Debugware IP

文章出處:【微信號:HME-FPGA,微信公眾號:HME京微齊力】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Nuclei Studio 編譯調(diào)試工程

VB TCP/UDP Socket調(diào)試助手軟件 Socket調(diào)試工具軟件

混合串口調(diào)試工具_軟件下載

介紹Lauterbach調(diào)試工具的應用

多核應用調(diào)試工具CodeViser介紹

京微齊力福晞軟件全面提升設計師交互體驗

福晞軟件調(diào)試工具介紹之工程添加Debugware IP

福晞軟件調(diào)試工具介紹之工程添加Debugware IP

評論