嵌入式通信技術(shù)的轉(zhuǎn)型中,MCU+AT架構(gòu)向OpenCPU的轉(zhuǎn)變成為物聯(lián)網(wǎng)時代的關(guān)鍵趨勢,這一轉(zhuǎn)型的必然性源于傳統(tǒng)架構(gòu)在復(fù)雜場景下的性能瓶頸與開發(fā)局限。上篇將從MCU+AT架構(gòu)的技術(shù)原理與應(yīng)用場景切入,分析其在資源利用率、實時響應(yīng)及開發(fā)效率方面的不足,結(jié)合物聯(lián)網(wǎng)終端對高性能、低成本的需求,深度拆解OpenCPU架構(gòu)興起的必然邏輯,為后續(xù)深度拆解提供背景支撐。

引言:從“通信外設(shè)”到“邊緣主機”的時代轉(zhuǎn)折

在物聯(lián)網(wǎng)的早期階段,當(dāng)時的物聯(lián)網(wǎng)叫做“M2M”通信,蜂窩通信模組通常扮演一個外設(shè)的角色,主控MCU負責(zé)業(yè)務(wù)邏輯與外設(shè)驅(qū)動,而蜂窩模組則像一個調(diào)制解調(diào)器,被動地等待主控通過AT指令發(fā)出命令,執(zhí)行諸如撥號、發(fā)送短信、上傳數(shù)據(jù)等通信任務(wù)。

直到今天,這種架構(gòu),依然是物聯(lián)網(wǎng)應(yīng)用的重要架構(gòu)。

這樣的架構(gòu)簡單、通用,但也意味著一種割裂:通信與控制分屬兩個世界。

同時,隨著通信模組的算力提升,系統(tǒng)資源不斷擴展,模組價格不斷下降,以及應(yīng)用需求的爆炸式增長,這種傳統(tǒng)架構(gòu)逐漸暴露出它的瓶頸——穩(wěn)定性檔次上不去,功耗下不來,實時性不夠,維護成本高。

同時,模組也可以不只是“被控制的外設(shè)”,它是能夠成為一個能自己運行邏輯的“主機”的,這就是OpenCPU模式。

MCUA+AT的架構(gòu),以及模組OpenCPU的架構(gòu),這兩種架構(gòu)已經(jīng)并行發(fā)展了至少20年。

在這20年間,前者一直是主流,后者只有少數(shù)公司采用。

但是到了2025年的今天,局面悄然發(fā)生了變化,形勢開始逆轉(zhuǎn)了。

第一章:MCU+AT架構(gòu)的工作機制

在了解OpenCPU的優(yōu)勢之前,我們需要先看清楚傳統(tǒng)MCU+AT架構(gòu)到底是如何工作的。 這不僅是對歷史的回顧,也是對比的基礎(chǔ)。

1.1 基本結(jié)構(gòu)

在MCU+AT模式下,系統(tǒng)通常由兩部分組成:

主控MCU:運行用戶應(yīng)用邏輯(傳感器采集、控制算法、數(shù)據(jù)處理)。

蜂窩模組:負責(zé)網(wǎng)絡(luò)連接、協(xié)議棧處理(TCP/UDP/MQTT/HTTP等)和底層通信。

二者通常通過UART串口相連,主控通過發(fā)送AT指令文本與模組通信。

1.2 典型的通信流程

以傳感器數(shù)據(jù)上傳為例,一個MCU+AT架構(gòu)的執(zhí)行流程大致如下:

MCU從傳感器讀取數(shù)據(jù);

MCU通過UART發(fā)送AT命令A(yù)T+CGATT=1 附著網(wǎng)絡(luò);

模組返回OK;

MCU再發(fā)送:AT+CIPSTART="TCP","server",port建立連接;

模組建立socket并返回CONNECT OK;

MCU發(fā)送AT+CIPSEND并傳輸數(shù)據(jù);

模組發(fā)送確認;

MCU等待SEND OK;

MCU關(guān)閉連接AT+CIPCLOSE;

模組斷開網(wǎng)絡(luò)。

每一步都需要MCU等待響應(yīng),所以MCU通常會維護一個AT指令的狀態(tài)機實現(xiàn)業(yè)務(wù)的完整閉環(huán)。

1.3 優(yōu)點:簡單、兼容、可移植

不可否認,MCU+AT模式的成功在于它的低門檻與標(biāo)準(zhǔn)化:

硬件分工明確:通信邏輯交給模組,應(yīng)用邏輯交給MCU;

開發(fā)門檻低:不需要理解蜂窩協(xié)議棧,只要發(fā)送命令即可;

模塊化生態(tài):不同廠家的模組AT命令體系類似,容易替換;

風(fēng)險可控:如果模組異常,MCU可以通過重啟模組恢復(fù)。

因此在早期的2G/NB-IoT/Cat.1設(shè)備中,這種架構(gòu)的應(yīng)用極其普遍,無論是POS機,還是智能抄表,還是充電樁,都廣泛采用了這種架構(gòu)。

1.4 隱藏的復(fù)雜性:

一個看似簡單的世界,實則暗流涌動

然而,這種“看似輕量”的結(jié)構(gòu),隨著應(yīng)用復(fù)雜度增加,很快就暴露出天生的限制:

1)AT指令本質(zhì)是文本通信

AT命令本是早期撥號調(diào)制解調(diào)器的遺留產(chǎn)物,本質(zhì)上是一種字符串解析機制。 當(dāng)MCU向模組發(fā)送命令時,模組必須做如下幾個步驟:

接收UART數(shù)據(jù);

解析字符串;

匹配命令;

執(zhí)行動作;

格式化輸出字符串返回結(jié)果。

這意味著——每個命令都是一次“解析+應(yīng)答”的高延遲過程。任何丟包、粘包、解析錯誤,都會導(dǎo)致通信異常。

2)多線程與異步?jīng)_突

MCU往往使用輪詢或中斷方式等待模組響應(yīng)。當(dāng)多任務(wù)(如同時上傳、下發(fā)、OTA、心跳)并行時,AT模式幾乎無法保證同步性。

于是會經(jīng)常出現(xiàn)如下的問題:

“串口亂序、命令丟失、狀態(tài)機卡死、模組長時間無響應(yīng)。”

這種情況下,如果把模組重新上電之外,沒有其他更好的處理辦法。

3)調(diào)試?yán)щy

AT模式中,問題可能出現(xiàn)在MCU端(命令未發(fā)出),也可能出現(xiàn)在模組端(命令未解析),也可能出現(xiàn)在網(wǎng)絡(luò)端(連接異常)。

而這些錯誤,在AT的日志上看起來幾乎一樣:或者是“超時”,或者是“ERROR”。

開發(fā)者常常陷入數(shù)小時的抓包與串口分析,但是經(jīng)常難以找到根本原因。

4)功耗管理割裂

蜂窩模組的網(wǎng)絡(luò)狀態(tài)(RRC Active / Idle / PSM,心跳包間隔)對功耗影響巨大,但MCU無法直接獲知模組當(dāng)前狀態(tài)。

因此,MCU很可能會在模組休眠時誤發(fā)命令,這就可能會造成喚醒模組過于頻繁,或者是兩個系統(tǒng)的休眠節(jié)奏不同步,從而很容易就使得整機的功耗翻倍或者好幾倍。

5)升級與維護成本高

MCU與模組是兩套固件,版本不一致或接口更新,往往導(dǎo)致幾個問題:

OTA更新復(fù)雜,系統(tǒng)設(shè)計的時候,就要分別考慮如何升級 MCU固件與模組固件;

調(diào)試與維護成本高;

不同模組固件版本的兼容性問題比較突出。

1.5 真實案例:

一臺共享設(shè)備的“死鎖循環(huán)”

以早期的一個案例為例:

某共享充電寶項目,使用STM32+Air724模組(AT模式),運行半年后現(xiàn)場出現(xiàn)“死機率高”的問題。

現(xiàn)場分析發(fā)現(xiàn)了如下的問題:

MCU周期性發(fā)送心跳;

若網(wǎng)絡(luò)擁塞,模組返回延遲;

MCU未收到響應(yīng),重復(fù)發(fā)送;

模組緩沖區(qū)溢出 → 無響應(yīng);

MCU判斷模組異常 → 重啟模組;

模組重啟2分鐘未附網(wǎng);

MCU再次重啟;

整機進入死循環(huán)。

問題本質(zhì)在于:兩顆芯片的狀態(tài)機不同步,而MCU無法感知模組內(nèi)部狀態(tài)。

還有一個出現(xiàn)的情況是:

MCU對于模組設(shè)置了看門狗機制,超過30秒鐘不回復(fù)指令,就認為模組死機,從而對模組重新上電。

這種機制,平時是沒有問題的,但是在對模組固件進行FOTA升級的時候,在網(wǎng)絡(luò)信號不好的時候,30秒鐘往往還沒升級完畢,這時候?qū)δ=M重新上電,就容易造成模組固件損壞,無法正常工作了。

1.6 結(jié)構(gòu)性矛盾的根源

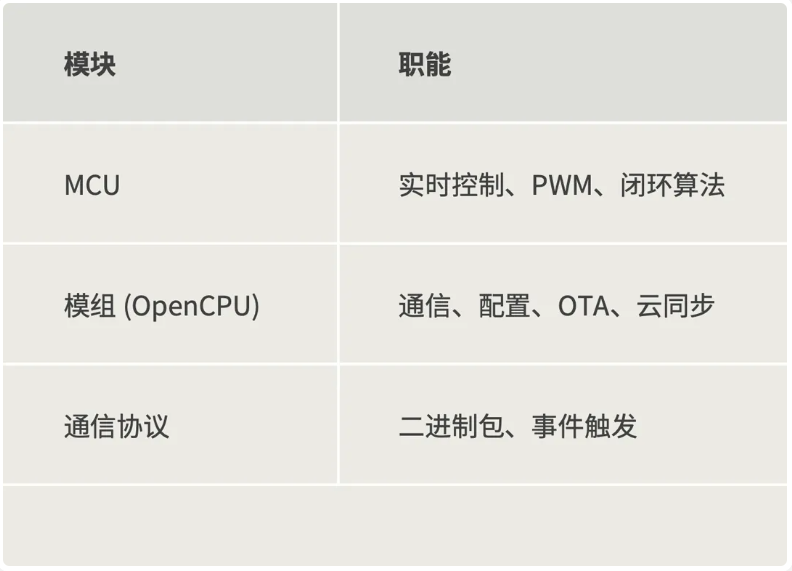

歸根結(jié)底,MCU+AT架構(gòu)存在三個根本性的結(jié)構(gòu)矛盾:

這些問題不是代碼層面的,而是架構(gòu)級問題。 因此,再怎么優(yōu)化串口驅(qū)動、調(diào)整命令時序,也只能臨時縫補,難以徹底解決問題。

1.7 總結(jié)

MCU+AT架構(gòu)是蜂窩物聯(lián)網(wǎng)早期最常見的方式,其核心在于通過AT文本命令實現(xiàn)通信控制。該架構(gòu)的優(yōu)點是簡單、兼容性強、開發(fā)門檻低,缺點是通信效率低、功耗不同步、調(diào)試?yán)щy。

這種架構(gòu)的根本瓶頸在于系統(tǒng)分層不當(dāng):控制與通信被人為分割。

當(dāng)應(yīng)用復(fù)雜化(并發(fā)、多線程、遠程升級)時,MCU+AT的固有缺陷就會明顯的暴露出來。

所以,MCU+AT的架構(gòu)注定只能作為過渡方案,而非未來主流架構(gòu)。

第二章:MCU+AT架構(gòu)的缺陷詳解

在工程實踐中,MCU+AT架構(gòu)的表面簡潔掩蓋了底層復(fù)雜。

許多企業(yè)在項目初期選擇它,是因為“快”“熟”“有例程”,但當(dāng)量產(chǎn)并進入運維階段,問題幾乎不可避免地爆發(fā)出來。

以下七個層面,是這種架構(gòu)最核心、最真實的缺陷,每一條都對應(yīng)著實際項目中最常見的“坑”。

2.1通信層缺陷:串口的“黑洞效應(yīng)”

在MCU+AT模式中,串口(UART)是唯一的通信橋梁。它既傳輸命令,又傳輸數(shù)據(jù),還傳輸狀態(tài)。

但是,UART是一個非結(jié)構(gòu)化的、異步的、無糾錯機制的通道。其設(shè)計初衷是“點對點數(shù)據(jù)流”,而非復(fù)雜的多任務(wù)交互。

于是出現(xiàn)了三大工程痛點:

1)丟包與粘包

MCU發(fā)送命令過快,模組緩沖區(qū)滿;

模組返回數(shù)據(jù)太快,MCU接收中斷丟字節(jié);

在多線程操作下,極易出現(xiàn)字符串邊界錯亂。

2)時序依賴

每個命令必須等待前一個命令返回,否則狀態(tài)機錯亂;

網(wǎng)絡(luò)延遲或服務(wù)器響應(yīng)慢,就可能讓系統(tǒng)“卡死”。

3)調(diào)試難度高

抓取串口日志往往只看到一串字符串:

AT+CIPSTART="TCP","xxx.xxx.xxx",1883

OK

CONNECT OK

AT+CIPSEND

>

任何異常都只能靠“猜”,因為底層TCP/IP狀態(tài)、信號質(zhì)量、網(wǎng)絡(luò)重傳等,MCU一無所知。

2.2協(xié)議層缺陷:命令語言的歷史包袱

AT命令最早源自1980年代Hayes Modem的撥號命令集。那時的任務(wù)是:撥號、掛斷、發(fā)送文本。

今天的物聯(lián)網(wǎng)設(shè)備卻要處理如下多種需求:

JSON編解碼;

MQTT長連接;

HTTPS證書;

Socket異常恢復(fù);

OTA升級;

多線程任務(wù)。

用一套“命令式字符串協(xié)議”去操縱這些復(fù)雜任務(wù),帶來了幾個問題:

命令集龐大(常見超過300條AT);

廠家之間不兼容;

模組版本變動頻繁;

命令的解析成本高,

系統(tǒng)的可靠性低。

工程上最痛苦的是,不同模組廠家的AT行為細節(jié)不同。

即使同一命令A(yù)T+CGATT,其返回格式、超時機制、異常碼都可能不同。

這讓軟件的問題分析的難度極大。

2.3功耗層缺陷:兩套時鐘的錯拍

蜂窩通信模組內(nèi)部有復(fù)雜的功耗狀態(tài)機:

RRC Active → Idle → PSM → Wakeup。

但外部MCU完全看不到這些狀態(tài),只能憑時間估計。

于是會出現(xiàn)兩種常見的錯誤:

MCU在模組未喚醒時發(fā)送命令,導(dǎo)致超時;

模組剛進入低功耗模式,MCU又觸發(fā)通信,導(dǎo)致頻繁喚醒。

結(jié)果會導(dǎo)致系統(tǒng)的總體功耗經(jīng)常翻倍,使得電池壽命大幅度縮短。

2.4穩(wěn)定性缺陷:雙狀態(tài)機的異步地獄

MCU有自己的任務(wù)狀態(tài)機,模組內(nèi)部也有通信狀態(tài)機。

兩者相互獨立,沒有共享內(nèi)存或消息隊列機制。

這就像兩個人隔著電話合作寫程序,一個人說一句,另一個人執(zhí)行一句。

在復(fù)雜邏輯下(例如OTA+MQTT+HTTP同時進行),極易出現(xiàn)如下問題:

命令重疊;

返回混亂;

狀態(tài)丟失;

異常重啟。

2.5成本缺陷:冗余硬件+冗余軟件

MCU+AT架構(gòu)意味著兩套系統(tǒng):一套MCU系統(tǒng),一套蜂窩模組系統(tǒng)。

這兩套系統(tǒng),各自需要分別處理電源管理,晶振和時鐘,固件升級,內(nèi)存管理和調(diào)試日志。

對于量產(chǎn)企業(yè)而言:物料成本至少高出30~50%,PCB占用面積大,測試流程復(fù)雜,供應(yīng)鏈BOM冗長,加工的良率下降。

更致命的是,軟件維護成本提高數(shù)倍。

每次升級,都至少需要兼顧如下事宜:

同步MCU固件;

同步模組固件;

測試兩者兼容性;

重新做OTA測試。

許多企業(yè)因此干脆凍結(jié)版本,寧可一直使用有缺陷的老固件,也不愿意升級更完善的新固件。

2.6調(diào)試與維護缺陷:黑箱中的黑箱

MCU無法直接訪問模組內(nèi)部的協(xié)議棧日志;而模組內(nèi)部的日志格式又與MCU不兼容,無法輸出。

這導(dǎo)致開發(fā)者調(diào)試如同“盲人摸象”:

對于串口通信失敗,網(wǎng)絡(luò)丟包,都缺乏有效的調(diào)試手段。

如果是在OpenCPU模式下,開發(fā)者可直接調(diào)用調(diào)試接口打印底層日志,能通過事件觸發(fā)看到TCP狀態(tài)。

但在MCU+AT模式下,這一切都是黑箱。

所以MCU+AT架構(gòu)的調(diào)試周期常常是:

1天寫邏輯,3天抓日志,5天復(fù)現(xiàn),2周找不到故障的根本原因,調(diào)試效率非常低下。

2.7安全與OTA缺陷:雙固件的雙重隱患

在安全與維護層面,MCU+AT也面臨兩道難題:

1)雙固件升級問題

MCU與模組需要分別升級;

網(wǎng)絡(luò)更新失敗概率加倍;

OTA包大、成本高;

一方更新后另一方不兼容,導(dǎo)致整機磚化。

2)安全漏洞難修補

MCU與模組分屬不同團隊;

通信鏈路暴露在UART層;

加密/認證邏輯分散;

缺乏固件安全機制。

隨著大家對安全的要求提高(TLS1.2、證書認證等),這種割裂架構(gòu)已難以滿足要求。

2.8總結(jié):架構(gòu)性疲勞的不可逆趨勢

MCU+AT模式的每一個問題,都可以靠補丁修一陣子,但沒有任何一種補丁能根治。

因為根因在于:

它把邏輯拆成了兩個物理世界。

通信與控制被強行分離,串口成了“最細的瓶頸”。

在今天這個要求低功耗、高穩(wěn)定、可OTA的IoT時代,它已不再可持續(xù)。

因此,行業(yè)開始轉(zhuǎn)向一種新的方式:

讓模組不再是被控制的外設(shè),而是具備完整運行能力的計算單元——這就是OpenCPU。

第三章:OpenCPU架構(gòu)的原理、運行機制與演進邏輯

能否讓功能日益強大的通信模組自己承擔(dān)所有計算與控制任務(wù),從而開啟一個更高效,讓模組“自己思考”的新時代?

這正是OpenCPU架構(gòu)所實現(xiàn)的革命性跨越。

3.1從“外設(shè)”到“主機”:角色的重定義

要理解OpenCPU的本質(zhì),必須先從角色轉(zhuǎn)變談起。

在MCU+AT模式中,模組只是一個通信外設(shè)(Peripheral)。

而在OpenCPU模式下,模組的地位徹底改變——它不再等待指令,而是直接運行應(yīng)用程序、控制外設(shè)、與云端交互。

換句話說:OpenCPU是讓蜂窩模組“變成計算機”的過程。

這并非一句營銷口號,而是架構(gòu)級的重生。

模組內(nèi)部的主控SoC原本就擁有幾百MHz的主頻、幾MB級的 Flash與RAM,有數(shù)十個對外開放的IO,支持GPIO、UART、 SPI、IIC、CAN、Camera、LCD等外設(shè)。

這些資源完全足以承載一套非常完整的物聯(lián)網(wǎng)的硬件系統(tǒng),無需額外的CPU。

3.2OpenCPU的基本組成

無論是LuatOS、OpenCPU SDK,還是定制平臺,它們在結(jié)構(gòu)上都遵循同樣的三層邏輯:

這種結(jié)構(gòu)的關(guān)鍵在于:通信協(xié)議棧、操作系統(tǒng)、應(yīng)用邏輯,在一個封閉而統(tǒng)一的系統(tǒng)中運行。

這讓模組可以自主完成從“感知 → 計算 → 通信 → 控制”的全過程。

3.3OpenCPU的運行機制

以Air8000+LuatOS為例,其內(nèi)部運行流程如下:

1)系統(tǒng)啟動

上電后,bootloader校驗固件完整性 → 掛載文件系統(tǒng) → 啟動LuatOS運行。

2)任務(wù)調(diào)度

LuatOS內(nèi)核基于事件驅(qū)動架構(gòu),不同功能模塊注冊任務(wù):

網(wǎng)絡(luò)連接任務(wù);

數(shù)據(jù)采集任務(wù);

定時器;

消息訂閱和分發(fā)(sys.publish / sys.subscribe)。

3)網(wǎng)絡(luò)棧啟動

調(diào)用系統(tǒng)API初始化基帶、SIM、PDP上下文:

可通過netdrv.ready()檢查網(wǎng)絡(luò)狀態(tài);

支持TCP、UDP、MQTT、HTTP等協(xié)議。

4)外設(shè)驅(qū)動加載

大家可通過Lua或C接口直接控制外設(shè):

5)業(yè)務(wù)邏輯執(zhí)行

腳本周期性采集數(shù)據(jù) → 打包 → 上報MQTT;

異常時自動重連或觸發(fā)看門狗。

6)遠程管理與OTA

系統(tǒng)支持FOTA(固件或腳本遠程升級);

可通過云端HTTP推送更新包;

OTA過程帶CRC校驗與分區(qū)回滾機制。

3.4關(guān)鍵技術(shù)特征

1)事件驅(qū)動與異步機制

OpenCPU平臺普遍采用事件驅(qū)動模型,而非輪詢或阻塞式結(jié)構(gòu)。

這意味著:各模塊之間通過消息隊列通信。

網(wǎng)絡(luò)、定時器、IO 操作均為異步回調(diào);

系統(tǒng)可同時處理多個事件。

在LuatOS中,一個典型的事件模型如下:

這種機制消除了傳統(tǒng)AT架構(gòu)下的“等待阻塞”,提升并發(fā)與響應(yīng)速度。

2)文件系統(tǒng)與本地存儲

OpenCPU模塊內(nèi)置Flash文件系統(tǒng),可用于:

日志存儲;

數(shù)據(jù)緩存;

OTA分區(qū);

配置文件。

示例(Lua)如下:

這使模組本身具備“邊緣緩存”的能力,可在離線時緩存數(shù)據(jù),在線后批量上報。

3)多線程與任務(wù)調(diào)度

雖然許多模組硬件上是單核,但通過輕量化RTOS(如:LuatOS的協(xié)程系統(tǒng)),可實現(xiàn)偽并發(fā)的多任務(wù)。

系統(tǒng)任務(wù)調(diào)度器負責(zé)管理任務(wù)隊列、優(yōu)先級與超時。

相比MCU+AT模式的單線程串口等待,這種模型極大提升系統(tǒng)吞吐量。

4)功耗管理與喚醒控制

OpenCPU可以直接訪問底層電源管理單元(PMU),根據(jù)網(wǎng)絡(luò)狀態(tài)自動進入休眠模式。

開發(fā)者可靈活設(shè)定休眠條件:

系統(tǒng)內(nèi)部會協(xié)調(diào)RRC狀態(tài)、定時器、外設(shè)活動,避免MCU+AT模式的“錯拍”問題。

5)安全機制

由于所有邏輯運行在模組內(nèi)部,OpenCPU可以統(tǒng)一實現(xiàn):

TLS/DTLS加密;

證書存儲;

安全啟動(Secure Boot);

完整性校驗(CRC/簽名);

OTA簽名驗證。

這讓安全從“外圍補丁”變成“系統(tǒng)內(nèi)建”,可以非常方便的提升系統(tǒng)的安全線,更容易符合現(xiàn)代物聯(lián)網(wǎng)的安全標(biāo)準(zhǔn)。

3.5OpenCPU的演進邏輯

OpenCPU的出現(xiàn)并非偶然,而是三股趨勢共同推動的結(jié)果:

1)硬件趨勢:算力下沉

隨著模組采用更強SoC,算力空余明顯;

過去只夠跑協(xié)議棧,現(xiàn)在足夠跑協(xié)議棧+應(yīng)用的組合。

2)軟件趨勢:RTOS與腳本化成熟

RTOS體積小、調(diào)度高效;

Lua、MicroPython 等腳本語言讓開發(fā)門檻降低。

3)商業(yè)趨勢:成本與周期壓力

市場要求一體化設(shè)計、快速迭代、低BOM;

OpenCPU模式正好滿足這些需求。

3.6LuatOS的代表性意義

系統(tǒng)內(nèi)部會協(xié)調(diào)RRC狀態(tài)、定時器、外設(shè)活動,避免MCU+AT模式的“錯拍”問題。

5)安全機制

由于所有邏輯運行在模組內(nèi)部,OpenCPU可以統(tǒng)一實現(xiàn):

TLS/DTLS加密;

證書存儲;

安全啟動(Secure Boot);

完整性校驗(CRC/簽名);

OTA簽名驗證。

這讓安全從“外圍補丁”變成“系統(tǒng)內(nèi)建”,可以非常方便的提升系統(tǒng)的安全線,更容易符合現(xiàn)代物聯(lián)網(wǎng)的安全標(biāo)準(zhǔn)。

3.5OpenCPU的演進邏輯

OpenCPU的出現(xiàn)并非偶然,而是三股趨勢共同推動的結(jié)果:

1)硬件趨勢:算力下沉

隨著模組采用更強SoC,算力空余明顯;

過去只夠跑協(xié)議棧,現(xiàn)在足夠跑協(xié)議棧+應(yīng)用的組合。

2)軟件趨勢:RTOS與腳本化成熟

RTOS體積小、調(diào)度高效;

Lua、MicroPython 等腳本語言讓開發(fā)門檻降低。

3)商業(yè)趨勢:成本與周期壓力

市場要求一體化設(shè)計、快速迭代、低BOM;

OpenCPU模式正好滿足這些需求。

3.6LuatOS的代表性意義

我們是國內(nèi)最早全力推動OpenCPU模式的公司之一,其LuatOS平臺在Air系列模組上全面替代傳統(tǒng)AT模式。

特征包括:

全異步架構(gòu):事件驅(qū)動、消息分發(fā);

腳本化開發(fā):Lua是C的膠水語言,是速度最快的腳本語言,語法簡單,可快速上手;

API豐富:內(nèi)置了73個核心庫、30多個擴展庫,涵蓋了HTTP、MQTT、Socket、文件系統(tǒng)、Camera、GNSS、音頻、UI、通話、短信、FTP、多網(wǎng)融合等等完善的庫;

硬件抽象層完備:GPIO、I2C、SPI、ADC、PWM、LCD、Camera、CAN都有成熟的支持庫;

OTA完整鏈路:云端推送、分區(qū)升級、CRC校驗。

一句話概括:LuatOS讓模組成為“運行在蜂窩網(wǎng)絡(luò)上的嵌入式計算機”,而不再是“被串口操控的通信外設(shè)”。

3.7總結(jié)

OpenCPU的本質(zhì)——是把通信模組變?yōu)榭蛇\行用戶邏輯的嵌入式主機。

它通過統(tǒng)一的RTOS+SDK,把通信、控制、低功耗、文件系統(tǒng)、微數(shù)據(jù)庫、UI、視覺功能,整合在一個固件系統(tǒng);通過事件驅(qū)動的異步機制,腳本化開發(fā),讓系統(tǒng)更加靈活、實時與穩(wěn)定;同時解決了系統(tǒng)安全、低功耗、OTA等問題。

LuatOS和Air系列硬件的結(jié)合,是OpenCPU模式的代表,并且實現(xiàn)了完整生態(tài),有成熟的開發(fā)者社區(qū)。

- 未完待續(xù),歡迎探討 -

審核編輯 黃宇

-

mcu

+關(guān)注

關(guān)注

147文章

19036瀏覽量

401481 -

嵌入式

+關(guān)注

關(guān)注

5204文章

20562瀏覽量

336008 -

AT

+關(guān)注

關(guān)注

2文章

202瀏覽量

66765 -

OpenCPU

+關(guān)注

關(guān)注

1文章

17瀏覽量

4871

發(fā)布評論請先 登錄

ALINX邀您共聚AMD嵌入式技術(shù)日北京站

什么是嵌入式應(yīng)用開發(fā)?

OpenCPU:取代MCU+AT的技術(shù)必然(完結(jié)篇)

小身材大能量的嵌入式板卡,profinet工業(yè)現(xiàn)場的通信替代好物

嵌入式通信技術(shù)轉(zhuǎn)型:MCU+AT向OpenCPU的必然性深度拆解(下篇)

嵌入式通信技術(shù)升級路徑:MCU+AT至OpenCPU的必然性深度拆解(上篇)

嵌入式和FPGA的區(qū)別

嵌入式需要掌握哪些核心技能?

嵌入式軟件測試與專業(yè)測試工具的必要性深度解析

廣州郵科嵌入式通信電源系統(tǒng):提升通信設(shè)備穩(wěn)定性與效率的關(guān)鍵

嵌入式和單片機,是同一個東西嗎?

Linux嵌入式和單片機嵌入式的區(qū)別?

聚徽智控——從嵌入式到邊緣計算:平板工控電腦的技術(shù)進化論

嵌入式開發(fā):高門檻的系統(tǒng)性工程與 996 的行業(yè)困局

嵌入式通信技術(shù)轉(zhuǎn)型:MCU+AT向OpenCPU的必然性深度拆解(上篇)

嵌入式通信技術(shù)轉(zhuǎn)型:MCU+AT向OpenCPU的必然性深度拆解(上篇)

評論