在半導體行業追求芯片性能與集成度的道路上,熱載流子注入效應(HCI)如同隱形殺手,悄然侵蝕著芯片的可靠性與壽命。隨著集成電路尺寸邁入納米級,這一問題愈發凸顯,成為制約芯片技術發展的關鍵瓶頸。

一、HCI:芯片中的 “能量入侵者”

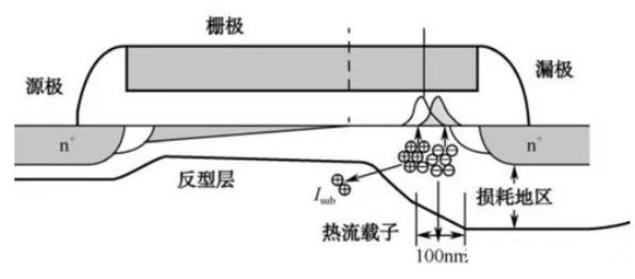

HCI 本質是半導體器件工作時,高能載流子突破材料勢壘侵入絕緣層的物理現象。如圖 1 所示,當芯片中的電子或空穴在電場加速下獲得過高能量,會掙脫束縛撞擊柵氧化層——這一晶體管柵極與溝道間的關鍵絕緣層,最終導致器件性能退化甚至失效。從手機處理器到服務器芯片,HCI 引發的壽命衰減可能造成設備卡頓、功能異常,極端情況下還會引發災難性故障。

(圖1)

二、HCI 的三大 “催生因子”

HCI 的產生并非偶然,而是多重物理機制共同作用的結果,其核心誘因可歸納為三點:

01高電場加速與能量積累

晶體管源極與漏極間的電壓形成強電場,載流子(如電子)在電場中加速。當電場強度超過臨界值(尤其短溝道器件),載流子動能可能突破晶格振動能級(約 3-4 eV),脫離常規輸運路徑,成為 “高能失控粒子”。

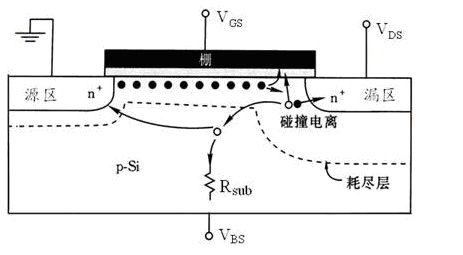

02碰撞電離與能量傳遞

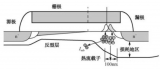

如圖 2 所示,高能載流子與晶格原子或其他載流子碰撞時,會引發 “雪崩效應”—— 一次碰撞產生多個二次載流子,進一步加劇能量分布不均。部分載流子借由量子隧穿效應,直接穿透柵氧化層的勢壘,完成 “注入” 過程。

03材料界面缺陷的放大作用

柵氧化層與硅襯底的界面并非絕對光滑,微觀缺陷(如懸掛鍵、氧空位)會成為載流子的 “陷阱”。如圖 3 所示,高能載流子撞擊缺陷點時,會引發局部電荷積累,加速氧化層老化,最終形成永久性損傷路徑。

(圖2)

[圖 2:HCI 碰撞電離過程示意圖(標注源區、漏區、耗盡層及碰撞電離發生區域)](GS DS 源區 漏區 n 碰撞電離 p-Si 耗盡層 Rsub ? VBS)

(圖3)

[圖 3:柵氧化層缺陷與載流子陷阱示意圖(展示缺陷點對載流子的捕獲及電荷積累過程)](載流子如何注入?氧化層缺陷)

三、HCI 對芯片的三重 “致命打擊”

HCI 對芯片的危害具有累積性與破壞性,具體體現在三個核心性能指標的退化:

01閾值電壓漂移

熱載流子注入柵氧化層后,會在界面處形成固定電荷,改變晶體管的閾值電壓(開啟電壓)。這直接導致電路延遲增加、功耗上升 —— 實驗數據顯示,28nm 工藝芯片在 HCI 影響下,閾值電壓偏移可達 50mV 以上,嚴重影響處理器主頻穩定性。

02跨導退化與驅動能力下降

柵氧化層損傷會降低溝道載流子遷移率,表現為晶體管跨導(增益)下降。例如,40nm 工藝測試中,HCI 應力試驗后 NMOS 跨導退化率達 15%,直接減慢邏輯門開關速度,嚴重時可能引發時序錯誤,導致芯片運算結果偏差。

03壽命指數級衰減

HCI 引發的失效時間(TTF)與電場強度呈指數關系。根據 Black 方程模型,電場強度每降低 10%,器件壽命可延長 10 倍。以 7nm FinFET 工藝為例,當工作電壓從 0.7V 升至 0.75V,HCI 失效時間會從 10 年驟降至不足 2 年,凸顯電壓控制對芯片壽命的關鍵影響。

四、多維度防御:抵御 HCI 的 “三重屏障”

為應對 HCI 威脅,半導體行業已形成材料、結構、系統多維度的解決方案:

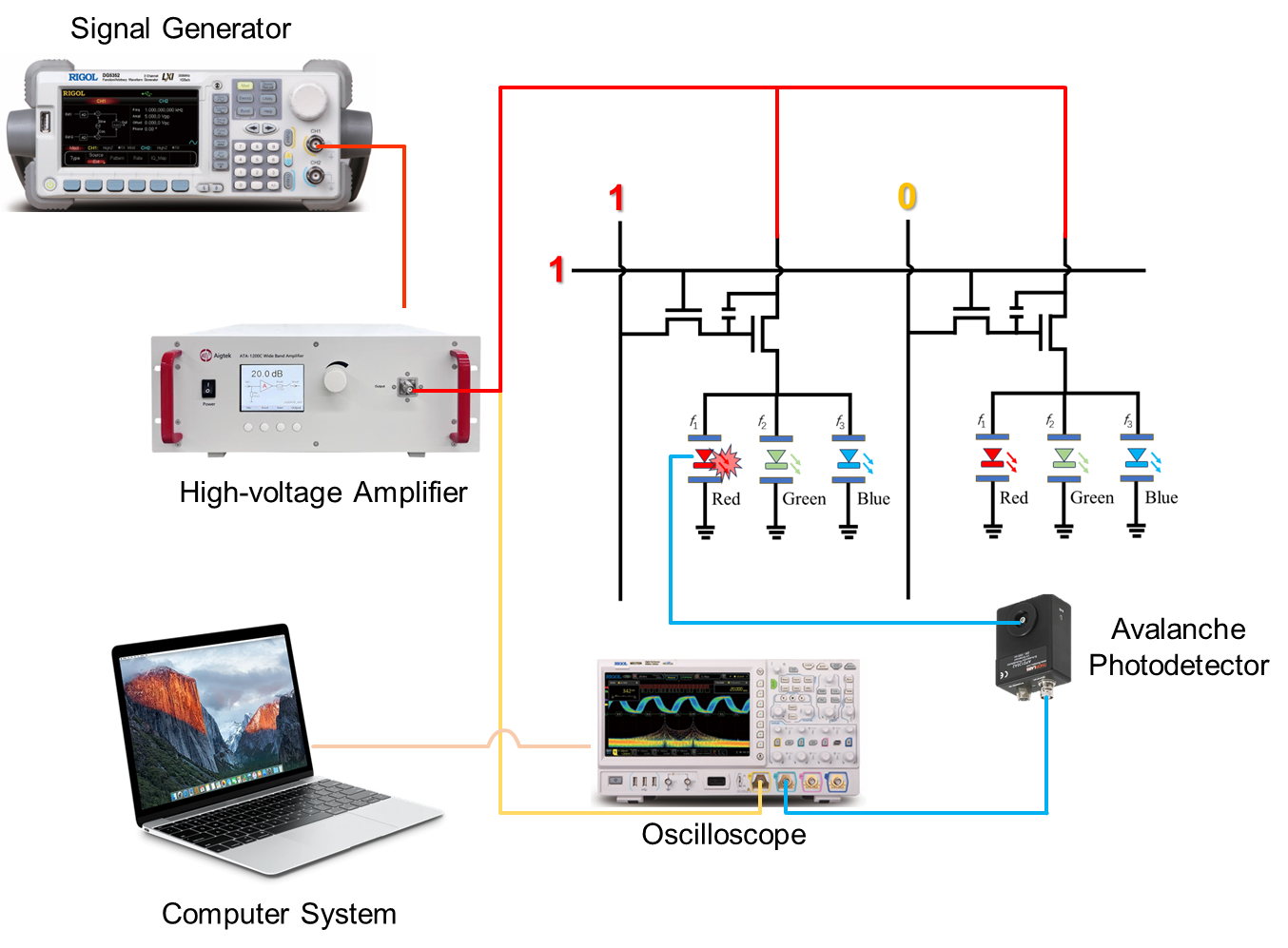

01材料創新:高 K 介質與應變硅

如圖 4 所示,采用高介電常數(High-K)材料(如 HfO?)替代傳統 SiO?,可在相同物理厚度下實現更高電容密度,降低工作電壓;同時,應變硅技術通過拉伸或壓縮晶格提升載流子遷移率,減少高電場需求。Intel 的 22nm Tri-Gate 技術即通過 3D 結構與材料優化,將 HCI 壽命提升 5 倍。

02結構優化:LDD 與 FinFET

輕摻雜漏極(LDD)通過在漏極附近形成梯度摻雜區,分散電場峰值,避免局部電場過強;而 FinFET 等三維結構通過增強柵極對溝道的控制力,將工作電壓降至 0.5V 以下。臺積電 5nm 工藝中,環柵(GAA)結構進一步優化電場分布,使 HCI 漏電流降低 40%。

03系統級防護:電壓調節與壽命模型

動態電壓頻率調節(DVFS)可根據芯片負載實時降低電壓,減少高電場工況;同時,EDA 工具(如 Synopsys 的 PrimeSim HSPICE)集成 HCI 壽命預測模型,在設計階段通過仿真識別 HCI 高危節點,指導布線與電路優化,從源頭降低 HCI 風險。

(圖4)

[圖 4:High-K 材料與應變硅結構對比圖(左為傳統 SiO?結構,右為 High-K + 應變硅結構,標注柵極、氧化層、襯底等關鍵部分)](Metal Metal Gate SiGe Gate SiGe Oxide Oxide Silicon Sillicon Substrate Substrate High Speed (HP/SP) High Voltage (TG) and Low Power Logic (LP/ULP))

在芯片向更小制程、更高性能演進的過程中,HCI 的挑戰仍將持續。唯有不斷突破材料、結構與設計技術,才能有效抵御這一隱形殺手,為芯片的長期穩定運行保駕護航。

季豐電子

季豐電子成立于2008年,是一家聚焦半導體領域,深耕集成電路檢測相關的軟硬件研發及技術服務的賦能型平臺科技公司。公司業務分為四大板塊,分別為基礎實驗室、軟硬件開發、測試封裝和儀器設備,可為芯片設計、晶圓制造、封裝測試、材料裝備等半導體產業鏈和新能源領域公司提供一站式的檢測分析解決方案。

季豐電子通過國家級專精特新“小巨人”、國家高新技術企業、上海市“科技小巨人”、上海市企業技術中心、研發機構、公共服務平臺等企業資質認定,通過了ISO9001、 ISO/IEC17025、CMA、CNAS、IATF16949、ISO/IEC27001、ISO14001、ISO45001、ANSI/ESD S20.20等認證。公司員工超1000人,總部位于上海,在浙江、北京、深圳、成都等地設有子公司。

-

芯片

+關注

關注

463文章

54010瀏覽量

466065 -

集成電路

+關注

關注

5452文章

12572瀏覽量

374547 -

半導體

+關注

關注

339文章

30737瀏覽量

264129

原文標題:技術分享 | 熱載流子注入效應(HCI)深度解析

文章出處:【微信號:zzz9970814,微信公眾號:上海季豐電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

功率放大器在驅動非載流子注入micro-LED上的應用

載流子平衡的低壓高效有機白光器件

光熱電效應的創新研究

MOSFET開態熱載流子效應可靠性

深亞微米pMOS器件的HCI和NBTI耦合效應與物理機制

pMOS器件的熱載流子注入和負偏壓溫度耦合效應

應力誘導載流子存儲效應被提出

功率二極管晶閘管載流子存儲效應和開關特性

8月22日|泰克云上大講堂—半導體可靠性熱載流子效應測試詳解

晶圓切割中深度補償 - 切削熱耦合效應對 TTV 均勻性的影響及抑制

功率放大器驅動:無載流子注入模式下一對多驅動研究的應用探索

熱載流子注入效應深度解析

熱載流子注入效應深度解析

評論