在電子設計領域,高精度、低噪聲的模擬 - 數字轉換器(ADC)一直是工程師們追求的目標。今天,我們就來深入探討一款由德州儀器(TI)推出的高性能四通道20位電流輸入ADC——DDC114。

文件下載:ddc114.pdf

一、產品概述

DDC114是一款高度集成的單芯片解決方案,專為直接測量四個低電平電流而設計。它集電流 - 電壓轉換和A/D轉換功能于一體,能夠直接連接四個低電平電流輸出設備,如光電二極管,并將其輸出數字化。這種設計大大簡化了電路設計,提高了系統的整體性能。

1.1 主要特性

- 高精度:具有真正的積分功能,積分線性度高達±0.01%的讀數±0.5ppm的滿量程范圍(FSR),能夠提供非常精確的測量結果。

- 低噪聲:噪聲僅為5.2ppm的FSR,確保了在低電平信號測量時的高靈敏度和準確性。

- 低功耗:每個通道的功耗僅為13.5mW,非常適合對功耗要求較高的應用場景。

- 可調數據速率:數據速率最高可達3.125kSPS,用戶可以根據實際需求進行調整。

- 可編程滿量程:滿量程范圍可在12pC至350pC之間進行調整,適應不同的應用需求。

- 可級聯串行接口:支持多個設備的級聯,方便構建大規模的測量系統。

1.2 應用領域

DDC114的高性能特性使其在多個領域得到了廣泛應用,包括CT掃描儀數據采集系統(DAS)、光電二極管傳感器、紅外高溫計以及液相/氣相色譜儀等。

二、電氣特性詳解

2.1 模擬輸入范圍

DDC114提供了8個不同的模擬輸入范圍,從12pC到350pC不等,用戶可以根據實際測量需求通過范圍選擇引腳(RANGE0 - RANGE2)進行選擇。這種靈活的輸入范圍設置使得DDC114能夠適應不同強度的電流信號測量。

2.2 動態特性

- 數據速率:在低功耗模式下,最大數據速率為2.5kSPS;在高速模式下,數據速率最高可達3.125kSPS。

- 積分時間:積分時間(TINT)可在50μs至1s之間進行調整,用戶可以根據需要選擇合適的積分時間來平衡測量精度和數據速率。

- 系統時鐘輸入:系統時鐘(CLK)的頻率可以根據不同的工作模式進行調整,以滿足不同的應用需求。

2.3 精度指標

- 噪聲:在低電平輸入(小于1% FSR)時,噪聲為5.2ppm的FSR(均方根值),確保了在微弱信號測量時的高精度。

- 積分線性誤差:典型值為±0.01%的讀數 + 0.5ppm的FSR,最大值為±0.025%的讀數 + 1.0ppm的FSR,保證了測量結果的線性度。

- 分辨率:通過FORMAT引腳可以選擇輸出數據的位數,當FORMAT = 1時,分辨率為20位;當FORMAT = 0時,分辨率為16位。

三、工作原理剖析

3.1 基本結構

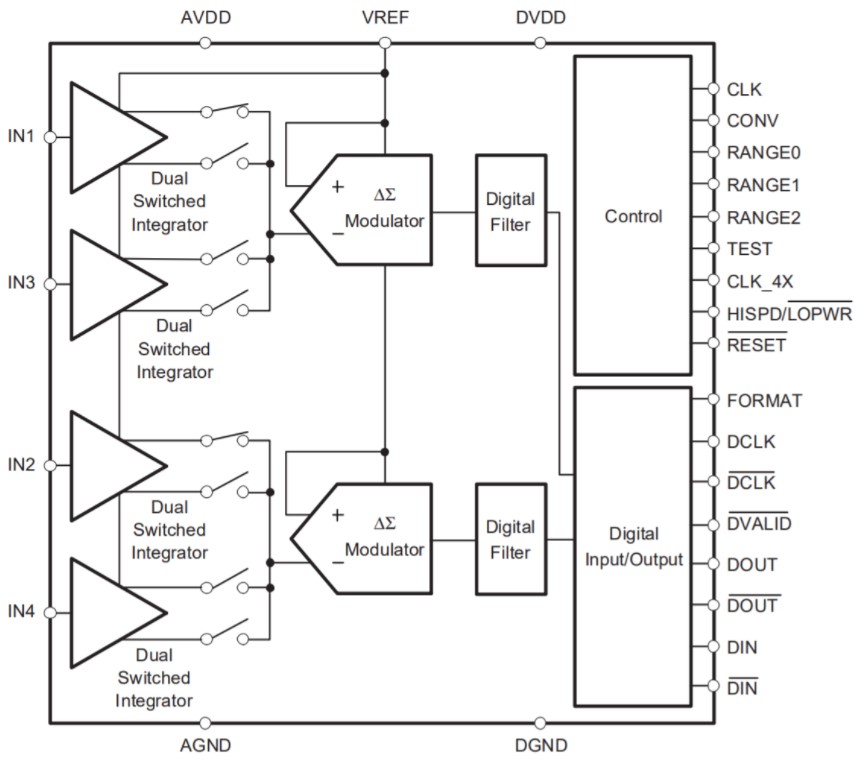

DDC114內部包含四個相同的輸入通道,每個通道都有兩個積分器,實現了電流 - 電壓的連續積分。積分器的輸出通過兩個四輸入多路復用器切換到兩個Delta - Sigma(?Σ)轉換器進行A/D轉換。

3.2 積分循環

前端的模擬積分器由運算放大器、可選的反饋電容網絡(CF)和多個開關組成。通過控制這些開關的狀態,可以實現積分、復位、等待和轉換等不同的狀態。在一個完整的A/D轉換周期中,積分電容會先被充電到參考電壓(VREF),然后開始積分輸入信號,最后將積分結果進行數字化轉換。

3.3 電壓參考

外部電壓參考(VREF)在DDC114的工作中起著至關重要的作用。它不僅用于在積分周期開始前復位積分電容,還在A/D轉換過程中作為參考電壓。為了確保VREF的穩定性和低噪聲,建議使用一個運算放大器對外部參考源進行緩沖。

四、數字接口與操作模式

4.1 數字接口

DDC114通過同步串行接口提供數字結果,包括差分數據時鐘(DCLK和DCLK)、有效數據引腳(DVALID)、差分串行數據輸出引腳(DOUT和DOUT)以及差分串行數據輸入引腳(DIN和DIN)。這種接口設計方便了多個設備的級聯和數據傳輸。

4.2 操作模式

- 低功耗模式:當HISPD/LOPWR = 0時,選擇低功耗模式,每個通道的典型功耗為13.5mW,最大數據速率為2.5kSPS。

- 高速模式:當HISPD/LOPWR = 1時,選擇高速模式,每個通道的典型功耗為18.0mW,最大數據速率為3.125kSPS。

4.3 數據檢索

在連續和非連續模式下,數據都可以在DVALID信號變低后進行檢索。數據通過數據時鐘(DCLK)的下降沿進行移位輸出。為了避免引入噪聲,建議在CONV信號變化期間停止數據檢索操作。

五、布局與電源注意事項

5.1 電源供應

AVDD和DVDD電源應盡可能保持安靜,以減少噪聲對測量結果的影響。可以采用兩種供電方式:一是使用兩個獨立的+5V電源分別為AVDD和DVDD供電,并使用10μF固體鉭電容和0.1μF陶瓷電容進行旁路;二是通過一個小于10Ω的隔離電阻從AVDD電源派生DVDD電源。

5.2 接地設計

建議將模擬地(AGND)和數字地(DGND)連接到印刷電路板(PCB)上的同一個接地平面,以減少接地噪聲。

5.3 屏蔽設計

由于DDC114的輸入阻抗較高,對外部噪聲非常敏感,因此在PCB布局時應采取屏蔽措施。可以在輸入引腳周圍設置一個PCB接地平面,以減少耦合噪聲和泄漏電流的影響。

六、總結與思考

DDC114以其高精度、低噪聲、低功耗和靈活的配置等優點,成為了許多高精度電流測量應用的理想選擇。在實際設計中,工程師們需要根據具體的應用需求,合理選擇工作模式、積分時間和輸入范圍等參數,同時注意電源供應、接地設計和屏蔽措施等方面的問題,以充分發揮DDC114的性能優勢。

大家在使用DDC114的過程中,有沒有遇到過什么問題或者有什么獨特的設計經驗呢?歡迎在評論區分享交流。

-

傳感器

+關注

關注

2577文章

55311瀏覽量

793075 -

adc

+關注

關注

100文章

7796瀏覽量

556658 -

模數轉換器

+關注

關注

26文章

4077瀏覽量

130218 -

低電平

+關注

關注

1文章

238瀏覽量

14020

發布評論請先 登錄

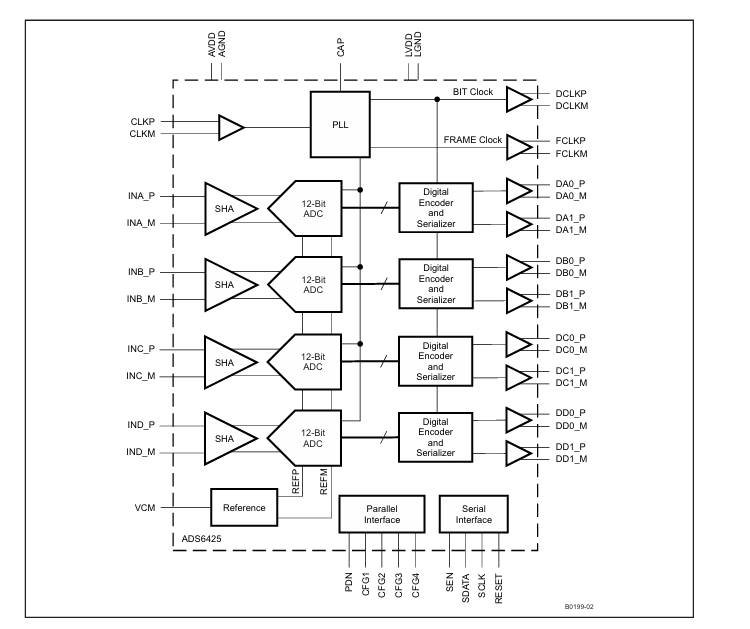

14位125MSPS四通道ADC,通過后端數字求和增強SNR性能

DDC114電流輸入型ADC的驅動設計與實現

請問有人有用過TI的 DDC114嗎?DDC114是怎么應用的?驅動程序是怎樣的?

DDC114 pdf datasheet(四路電流輸入20位

ADS6425高性能12位、125 MSPS四通道ADC數據表

深入解析DDC114:高性能四通道20位電流輸入ADC

深入解析DDC114:高性能四通道20位電流輸入ADC

評論