在電子設計領域,模數轉換器(ADC)是連接模擬世界和數字世界的關鍵橋梁。今天,我們要詳細探討的是德州儀器(Texas Instruments)的ADS8504,一款性能卓越的12位250-KSPS采樣CMOS模數轉換器。

文件下載:ads8504.pdf

一、產品概述

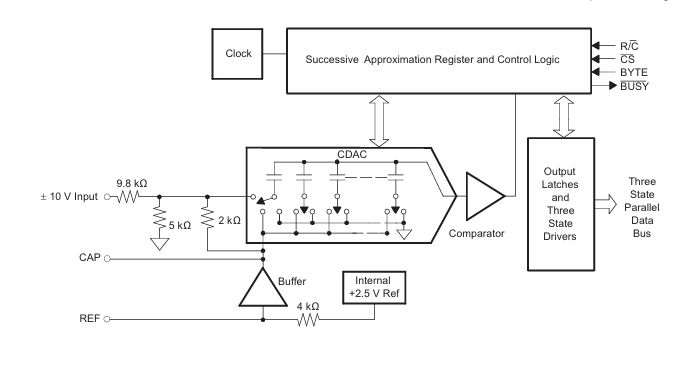

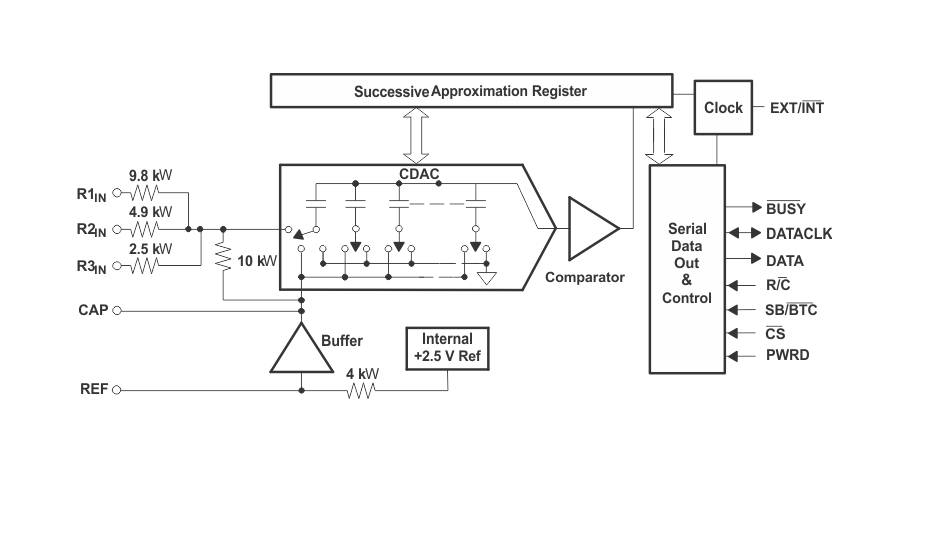

ADS8504采用了先進的CMOS結構,集完整的12位、基于電容的逐次逼近寄存器(SAR)ADC、采樣保持(S/H)電路、參考源、時鐘、微處理器接口以及三態輸出驅動器于一體。它在全溫度范圍內的采樣速率可達250-kHz,標準輸入范圍為±10-V,以其高精度和低功耗的特點,在工業過程控制、數據采集系統、數字信號處理以及醫療設備儀器等領域得到了廣泛應用。

二、關鍵特性亮點

(一)高精度性能

- 線性誤差小:最大積分非線性(INL)和最大微分非線性(DNL)均為±0.45 LSB,確保了轉換結果的高精度。

- 無失碼設計:12位無失碼特性,保證了數據轉換的完整性和準確性。

- 低誤差漂移:雙極性零誤差為±1 LSB,雙極性零誤差漂移僅為±0.4 PPM/°C,在不同溫度環境下仍能保持穩定的性能。

(二)高采樣速率

具備250-kHz的采樣速率,能夠快速準確地采集模擬信號,滿足高速數據采集的需求。

(三)寬輸入范圍

標準的±10-V輸入范圍,可適應多種不同幅度的模擬信號輸入。

(四)低功耗設計

單5-V電源供電,在250 KSPS采樣速率下典型功耗僅為70-mW,有效降低了系統的功耗。

(五)靈活的參考源選擇

可使用內部或外部參考源,為不同的應用場景提供了更多的靈活性。

(六)并行數據輸出

全并行數據輸出方式,方便與微處理器等數字設備進行接口連接,提高數據傳輸效率。

(七)封裝形式

采用28引腳的小外形集成電路(SOIC)封裝,便于在電路板上進行布局和焊接。

三、電氣特性詳解

(一)模擬輸入特性

- 輸入范圍:標準的±10-V輸入范圍,能夠滿足大多數工業和醫療應用的需求。

- 輸入阻抗:輸入阻抗為11.5 kΩ,可有效減少信號源的負載效應。

- 輸入電容:輸入電容為50 pF,對輸入信號的影響較小。

(二)吞吐量速度

- 轉換周期:采集和轉換周期為4 μs,確保了快速的數據轉換。

- 吞吐量速率:吞吐量速率可達250 kHz,能夠滿足高速數據采集的要求。

(三)直流精度

- INL和DNL:最大INL和DNL均為±0.45 LSB,保證了轉換結果的線性度。

- 無失碼:12位無失碼設計,確保了數據的準確性。

- 過渡噪聲:過渡噪聲典型值為0.1 LSB,進一步提高了轉換的精度。

(四)交流精度

- 無雜散動態范圍(SFDR):在45-kHz輸入時,SFDR可達86 dB(典型值為94 dB),有效抑制了雜散信號的干擾。

- 總諧波失真(THD):在45-kHz輸入時,THD為-95 dB,保證了信號的純凈度。

- 信噪失真比(SINAD):在45-kHz輸入時,SINAD為73 dB,提供了良好的信號質量。

- 全功率帶寬:全功率帶寬為500 kHz,可處理較寬頻率范圍的信號。

(五)采樣動態特性

- 孔徑延遲:孔徑延遲為5 ns,減少了采樣時刻的誤差。

- 瞬態響應:滿量程階躍響應時間為2 μs,能夠快速響應輸入信號的變化。

- 過壓恢復:過壓恢復時間為150 ns,在輸入信號過壓后能夠迅速恢復正常工作。

(六)參考源特性

- 內部參考電壓:內部參考電壓為2.5 V,典型漂移為8 ppm/°C。

- 外部參考電壓范圍:外部參考電壓范圍為2.3 V至2.7 V,可根據實際需求進行調整。

(七)數字輸入輸出特性

- 邏輯電平:數字輸入低電平(VIL)為-0.3 V至0.8 V,高電平(VIH)為2.0 V至VDIG +0.3 V,確保了與不同數字設備的兼容性。

- 數據格式:數據以二進制補碼形式輸出,采用全并行12位格式。

- 輸出電壓:低電平輸出電壓(VOL)最大為0.4 V,高電平輸出電壓(VOH)最小為4 V。

四、基本操作與使用方法

(一)啟動轉換

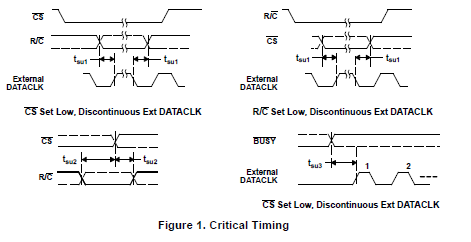

通過將CS(片選)和R/C(讀/轉換)引腳拉低至少40 ns,可立即將ADS8504的采樣保持電路置于保持狀態并啟動轉換。轉換過程中,BUSY引腳會拉低,直到轉換完成且內部輸出寄存器更新后才會拉高。在BUSY為低電平時,任何新的轉換命令都會中止當前正在進行的轉換并重置ADC。

(二)讀取數據

ADS8504以二進制補碼形式輸出全并行或字節并行數據。當R/C引腳為高電平且CS引腳為低電平時,并行輸出有效。可通過BYTE引腳選擇讀取高8位或低8位數據。轉換完成后,BUSY引腳拉高,此時可在D11 - D0引腳讀取有效數據。在轉換過程中,也可讀取上一次轉換的有效數據,但需注意在轉換開始后的2.2 μs(典型值)內不要讀取數據,以免讀取到無效數據。

五、輸入范圍與保護

ADS8504提供標準的±10-V輸入范圍。其輸入阻抗為11.5 kΩ,由內部電阻網絡和外部電阻共同構成。輸入電阻分壓器網絡提供了至少±25 V的過壓保護,有效保護了芯片免受過高電壓的損害。同時,輸入信號應參考AGND1,以減少模擬設計中常見的地環路問題,且模擬輸入應由低阻抗源驅動。

六、校準方法

(一)硬件校準

通過安裝如圖24(a)所示的適當電阻和電位器,可對ADS8504的失調和增益進行校準。校準過程中,應先調整失調,再調整增益,因為失調會直接影響增益的校準結果。為達到最佳性能,可能需要進行多次迭代調整。

(二)軟件校準

在軟件校準方式下,無需外部電阻。通過軟件算法對失調和增益誤差進行補償,可實現對ADS8504的校準。具體可參考無校準部分中關于外部電阻影響的詳細說明以及表4中有無外部電阻時失調和增益誤差的范圍。

(三)無校準情況

在某些應用中,圖24(b)所示的外部電阻可能并非必需。這些電阻用于補償內部失調和增益的調整,以實現單電源校準。表4給出了有無外部電阻時典型的失調(雙極性零誤差,BPZ)和增益誤差范圍。

七、參考源使用

ADS8504可使用內部2.5-V參考源或外部參考源。通過將外部參考源施加到REF引腳,可繞過內部參考源。REF引腳是外部參考源的輸入或內部2.5-V參考源的輸出,應盡可能靠近該引腳連接一個2.2-μF的電容,以減少參考源上的噪聲。CAP引腳是內部參考緩沖器的輸出,同樣需靠近該引腳放置一個2.2-μF的電容,以提供轉換周期內CDAC所需的最佳開關電流,并補償內部緩沖器的輸出。

八、布局注意事項

(一)電源布局

為獲得最佳性能,應將模擬和數字電源引腳連接到同一個+5-V電源,并將模擬和數字地連接在一起。由于ADS8504約90%的功率用于模擬電路,因此應將其視為模擬組件。A/D的+5-V電源應與系統數字邏輯的+5 V電源分開,以避免數字邏輯的開關噪聲影響轉換器的性能。若必須使用數字電源為轉換器供電,需對電源進行適當濾波。

(二)接地布局

ADS8504有三個接地引腳:DGND為數字電源地,AGND2為模擬電源地,AGND1為A/D內部所有模擬信號的參考地。AGND1對電流引起的電壓降更為敏感,因此其返回電源的路徑應具有最小電阻。為實現最佳性能,A/D的所有接地引腳應連接到模擬地平面,并與系統的數字邏輯地分開。模擬和數字地平面應盡可能靠近電源連接到系統地,以防止動態數字地電流通過公共阻抗調制模擬地。

(三)信號調理布局

ADS8504的采樣保持電路采用的FET開關釋放的電荷注入量僅為其他CMOS A/D轉換器的5% - 10%,且有電阻前端可衰減釋放的電荷,因此對前端抗混疊濾波器的要求較低。任何適用于應用信號的運算放大器都足以驅動ADS8504。此外,電阻前端還提供了±25 V的過壓保護,在大多數情況下可無需外部輸入保護電路。

(四)中間鎖存器布局

雖然ADS8504的并行端口具有三態輸出,但在轉換過程中若總線需要保持活躍,建議使用中間鎖存器。即使A/D處于三態,并行端口上快速開關信號產生的瞬態也可能通過襯底耦合到模擬電路,導致轉換器性能下降。中間鎖存器對于任何單片A/D轉換器都有益處。

九、總結

ADS8504作為一款高性能的12位250-KSPS采樣CMOS模數轉換器,憑借其高精度、高采樣速率、低功耗、寬輸入范圍以及靈活的參考源選擇等優點,在眾多領域展現出了卓越的性能。在實際應用中,通過合理的校準方法、正確的參考源使用以及精心的布局設計,能夠充分發揮其優勢,為電子工程師提供可靠的模擬信號數字化解決方案。

作為電子工程師,我們在設計過程中應充分考慮ADS8504的各項特性和要求,結合具體應用場景進行優化設計。大家在使用ADS8504的過程中遇到過哪些問題呢?又是如何解決的呢?歡迎在評論區分享交流。

-

CMOS

+關注

關注

58文章

6224瀏覽量

243249 -

模數轉換器

+關注

關注

26文章

4095瀏覽量

130225 -

KSPS

+關注

關注

0文章

6瀏覽量

8602 -

逐次逼近寄存器

+關注

關注

0文章

38瀏覽量

8270

發布評論請先 登錄

ADS8504一種12位250kSPS采樣CMOS模數轉換器的詳細資料概述

12位250kSPS采樣CMOS模數轉換器ADS8504的詳細資料概述

ADS7825 4通道、16位采樣CMOS模數轉換器數據表

ADS7824 4通道、12位采樣CMOS模數轉換器數據表

德州儀器ADS8505:16位250-KSPS采樣CMOS模數轉換器的全方位解析

深入解析ADS5413:12位、65-MSPS IF采樣模數轉換器

深入解析ADS8504:12位250-KSPS采樣CMOS模數轉換器

深入解析ADS8504:12位250-KSPS采樣CMOS模數轉換器

評論