在當今數(shù)字化的時代,圖像信號處理技術(shù)在眾多領(lǐng)域發(fā)揮著至關(guān)重要的作用,無論是數(shù)字彩色復(fù)印機、掃描儀,還是其他圖像處理應(yīng)用,都對圖像信號處理器提出了更高的要求。今天,我們就來深入探討一款備受矚目的產(chǎn)品——LM98620 10 - Bit 70 MSPS 6 通道成像信號處理器。

文件下載:lm98620.pdf

一、LM98620 概述

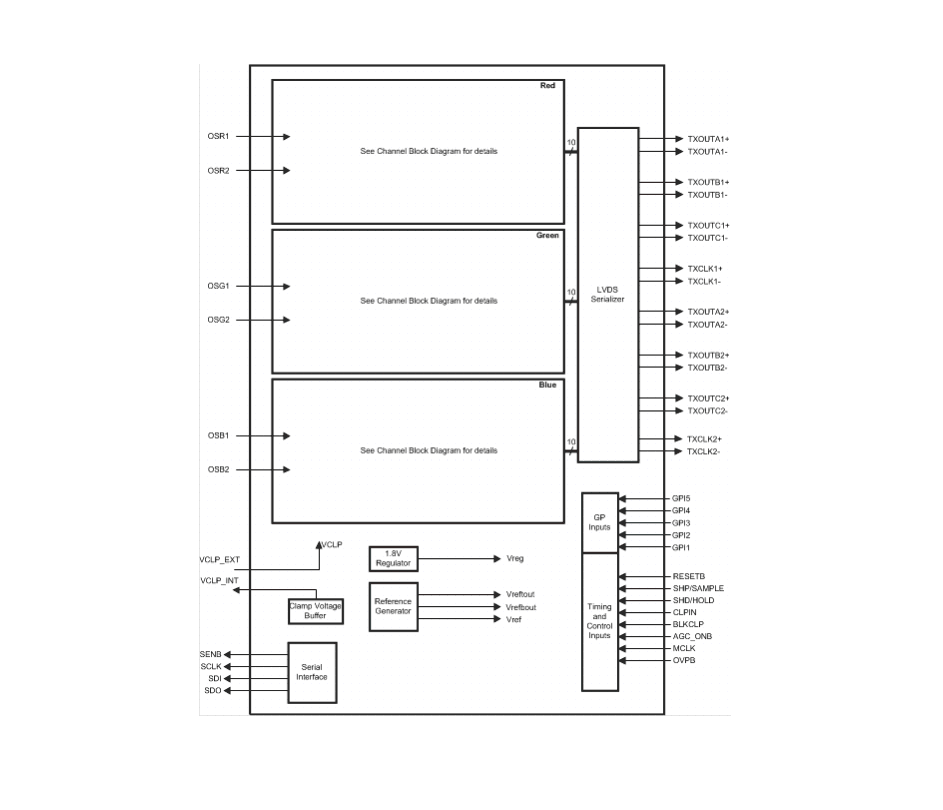

LM98620 是一款專為高性能數(shù)字彩色復(fù)印機、掃描儀及其他圖像處理應(yīng)用而設(shè)計的全集成式解決方案。它采用 10 - Bit 分辨率和 70 MSPS 的信號處理速度,憑借創(chuàng)新的六通道架構(gòu),結(jié)合相關(guān)雙采樣(CDS)或采樣保持(SH)類型的采樣技術(shù),實現(xiàn)了高速信號處理。

1.1 關(guān)鍵特性

- 單電源供電:支持 3.3 V 單電源運行,簡化了電源設(shè)計。

- 高通道速率:每個通道的速率可達 35 MHz,確保了高速的數(shù)據(jù)處理能力。

- ESD 保護增強:在時序、控制和 LVDS 引腳處采用了增強的 ESD 保護,提高了設(shè)備的可靠性。

- 低功耗設(shè)計:采用低功耗 CMOS 設(shè)計,降低了系統(tǒng)的功耗。

- 獨立增益和偏移校正:每個通道都有獨立的 1x 到 10x(8 位)可編程增益放大器(PGA)和 ±4 位粗調(diào)和 ±10 位細調(diào)的模擬偏移校正 DAC,可實現(xiàn)精確的增益和偏移調(diào)整。

- 數(shù)字校準功能:具備數(shù)字白電平自動校準和數(shù)字黑電平自動校準功能,可自動設(shè)置 PGA 值和偏移校正值,以達到選定的目標電平。

- LVDS 輸出:提供 12 至 16 端子(可選)的 LVDS 串行數(shù)據(jù)輸出,支持 4 線串行接口。

1.2 應(yīng)用領(lǐng)域

- 數(shù)字彩色復(fù)印機和掃描儀:為這些設(shè)備提供高質(zhì)量的圖像信號處理,確保清晰、準確的圖像復(fù)制和掃描。

- 其他圖像處理應(yīng)用:如工業(yè)檢測、醫(yī)療成像等領(lǐng)域,也能發(fā)揮其高性能的優(yōu)勢。

二、詳細技術(shù)分析

2.1 輸入處理

許多傳感器輸入信號的共模電壓與 LM98620 輸入電路的共模電壓不同,因此在應(yīng)用中常采用交流耦合來阻斷源與 AFE 輸入之間的直流電壓差。輸入鉗位電路用于將 AFE 輸入設(shè)置在合適的共模電壓上。

- 初始粗調(diào)鉗位:可使用 PIB(無源輸入偏置)和/或 AIB(有源輸入偏置)電路進行初始粗調(diào)鉗位。設(shè)置 PIB 使能位可將 1 kΩ 上拉和下拉電阻連接到輸入,使其快速充電至 $V_{DDA} / 2$;設(shè)置 AIB 位可通過低阻抗開關(guān)將 VCLPEXT 參考電壓連接到輸入。但在正常操作期間,必須禁用 AIB 和 PIB。

- 圖像捕獲期間的黑電平鉗位:在圖像捕獲期間,通過低阻抗開關(guān)將輸入引腳連接到內(nèi)部參考電壓進行黑電平鉗位。鉗位會定期開啟,以校正直流輸入電壓的任何下降,并最小化轉(zhuǎn)換誤差。鉗位開關(guān)會在輸入信號的“黑”部分開啟,此時輸入處于已知電壓電平。鉗位將輸入連接到約 1.65 V 的參考電平,也可在 VCLPEXT 引腳施加客戶提供的參考電壓。

2.2 增益和偏移控制

- 增益控制:PGA 提供 1x 到 10x 的增益范圍,分辨率為 8 位,增益曲線為 $Gain = 283 / (283 - M)$,其中 M 是 8 位增益設(shè)置值(0 到 255)。此外,CDS/SH 階段提供 1x 或 2x 的增益,使整體通道增益達到 1x 到 20x(0 dB 到 26 dB)。

- 偏移控制:在 ADC 之前提供模擬偏移校正,使用兩個偏移 DAC 提供粗調(diào)(CDAC)和細調(diào)(FDAC)偏移。偏移 CDAC 提供 ±280 mV 的范圍,分辨率為 ±4 位;偏移 FDAC 提供 ±110 mV(大 FDAC 范圍)或 ±59.5 mV(小 FDAC 范圍)的范圍,分辨率為 ±10 位。

- 黑電平校準:可通過手動或自動兩種方法進行黑電平校正。手動方法適用于處理系統(tǒng)中所需的黑電平校正環(huán)在 LM98620 外部的情況,由外部處理器控制黑電平偏移寄存器;自動方法則通過啟用黑電平偏移自動校準位,使用 CDAC 和 FDAC 來使輸出收斂到所需的黑電平目標。

- 白電平校準:白校準環(huán)允許 LM98620 自動設(shè)置增益,以達到所需的最大 ADC 輸出。通過數(shù)字輸入引腳或配置寄存器位啟動循環(huán),處理定義的白像素范圍內(nèi)的輸出數(shù)據(jù)。在處理過程中,執(zhí)行移動窗口平均,并將窗口平均值與先前的峰值白值進行比較,更新峰值白值。如果 AGC_ONB 輸入被脈沖觸發(fā),白校準環(huán)將在掃描開始時運行固定數(shù)量的行。

2.3 功能模式

LM98620 有多種功能模式,不同模式下的輸入信號組合和處理方式有所不同。

- AFEPHASEn 與輸入信號的組合:在 SHP/SHD 輸入模式下,SHP 和 SHD 輸入分別與選定的 AFEPHASEn 信號進行與運算,生成內(nèi)部 CLAMP 和 SAMPLE 信號;在 SAMPLE 和 HOLD 輸入模式下,SAMPLE 和 HOLD 輸入生成的采樣控制脈沖由 AFEPHASEn 信號的低電平周期進行門控,生成內(nèi)部使用的 SAMPLE 信號。

- 6 通道和 3 通道模式:在 6 通道模式下,每個傳感器像素周期有兩個完整的 ADCCLK 周期,允許兩個 AFE 通道復(fù)用至單個 ADC,有 4 種可能的 AFEPHASEn 時序;在 3 通道模式下,每個像素周期只有一個 MCLK 和 ADCCLK 周期,因此只有 2 種 AFEPHASEn 選擇。

- 同步模式:LM98620 有三種主要的操作模式,在 6 通道模式使用 ADC 速率 MCLK 時,需要 CLPIN 輸入信號與 MCLK 結(jié)合,以確保內(nèi)部采樣相位與像素速率輸入信號同步。

2.4 編程與寄存器配置

編程對于 LM98620 的正常運行至關(guān)重要,需要對多個寄存器進行初始化和配置。

- 使用黑像素平均值:在大多數(shù)應(yīng)用中,應(yīng)設(shè)置黑像素平均值位。在白環(huán)操作期間,從 ADC_MAX 中減去黑像素平均值,得到當前的白值,用于與目標白像素值進行比較。在啟動白環(huán)之前,需要初始化多個寄存器,如 PK_DET_ST、PKDET_WID、AGCDuration、AGCTarget 等。

- 采樣時序控制:采樣時序通過內(nèi)部 AFEPHASEn 信號和編程的內(nèi)部采樣時序信號進行控制,也可使用外部采樣時序信號。不同的輸入時序模式由寄存器 0x00、0x02、0x04 和 0x05 中的位進行選擇。

- DLL 基于的采樣時序設(shè)置:內(nèi)部 DLL 設(shè)置確定內(nèi)部生成的采樣脈沖的位置,僅適用于 SH2b 時序模式。通過設(shè)置寄存器位選擇采樣模式,AFEPHASE 寄存器設(shè)置粗采樣時序框架,Sample Trailing Edge Position 寄存器設(shè)置采樣脈沖的結(jié)束位置。

- 外部采樣時序輸入:不同模式下,內(nèi)部采樣或鉗位和采樣時序信號的生成方式不同。在 SH1a 和 CDSa 模式下,由選定的 AFEPHASEn 信號生成;在 SH1b 和 CDSb 模式下,輸入信號由內(nèi)部 AFEPHASEn 信號進行門控;在 SH2 模式下,SAMPLE 和 HOLD 時序信號直接輸入到 AFE 的采樣階段;在 SH3 模式下,SAMPLE 和 HOLD 時序信號不僅直接輸入到 AFE 的采樣階段,還用于設(shè)置后續(xù)階段的內(nèi)部 AFEPHASE 時序。

- LVDS 數(shù)據(jù)輸出:AFE 數(shù)據(jù)通過串行化的 LVDS 接口輸出,有多種串行化模式可供選擇,如 6 對模式可使用標準的 DS90CR218A 或 DS90CR364 解串器 IC,5 對模式可使用單個 5 通道解串器,可通過斷開未使用的數(shù)據(jù)對和 TXCLK 對來降低功耗和成本。

- 輸出數(shù)據(jù)測試模式:可生成四種基本類型的測試模式,包括固定模式、水平漸變模式、垂直漸變模式和晶格模式。通過設(shè)置多個寄存器,如 PK_DET_ST、PK_DET_WID、PATSW、PATMODE 等,可控制測試模式的輸出。

- 串行接口:串行控制接口基于常見的 Microwire 接口,有特定的時序細節(jié)。在設(shè)備上電并施加穩(wěn)定的 MCLK 后,必須將串行接口模式(寄存器 0x01,位 3)設(shè)置為 1 以進行正常操作。串行寫和讀操作有各自的命令格式和時序要求。

三、應(yīng)用與實現(xiàn)

3.1 應(yīng)用信息

白環(huán)提供二進制搜索和增量搜索兩種收斂到目標值的技術(shù)。二進制搜索算法旨在快速收斂到目標值,在初始操作期間允許通道增益有較大變化,后期切換到增量搜索模式以實現(xiàn)低誤差;增量或線性搜索算法旨在提供低誤差,但收斂速度較慢,通道增益的變化始終以 1 lsb 為增量,以實現(xiàn)低過沖和高收斂精度。

3.2 典型應(yīng)用設(shè)計

- 設(shè)計要求:所有電源供應(yīng)電壓應(yīng)來自干凈的線性穩(wěn)壓器輸出,避免使用開關(guān)電源。在 RxIN+/- 引腳附近放置 100 Ω 終端電阻。

-

詳細設(shè)計步驟

- 電源供應(yīng):為模擬、數(shù)字和 LVDS 電源提供 3.3 V 電源,建議使用通用的 LDO 穩(wěn)壓器,并使用 EMI 濾波設(shè)備和專用去耦電容來隔離總線之間的噪聲。

- 輸入時序信號:提供多種輸入時序信號,如 MCLK、CLPIN、BLKCLP、AGC_ONB、SHP/SAMPLE 和 SHD/HOLD 等,用于控制輸入鉗位、指示黑像素開始、啟動白校準等操作。

- 通用邏輯輸入:可選的通用邏輯輸入可用于從成像板向數(shù)據(jù)處理模塊傳輸?shù)退贁?shù)字狀態(tài)信息。

- CCD 信號:CCD 信號通過 0.1 uF 電容交流耦合到 AFE 輸入。

- 串行控制接口:數(shù)據(jù)處理模塊通過串行控制接口與 LM98620 通信,包括 SENB、SCLK、SDI 和 SDO 等信號。

- LVDS 數(shù)據(jù)連接:串行化的 LVDS 數(shù)據(jù)對連接到 FPGA 或 LVDS 解串器芯片。

- 寄存器配置:根據(jù)需要調(diào)整和重新配置配置寄存器設(shè)置。

四、電源供應(yīng)與布局建議

4.1 電源供應(yīng)建議

OS 輸入在芯片未供電或剛上電時,通過 PMOS 器件鉗位到 VBSSAB,以防止傳感器電路的瞬態(tài)損壞。通過將高電平施加到 OVPB 輸入引腳并將 OVP 使能位設(shè)置為默認狀態(tài) 0,可禁用保護鉗位電路。

4.2 布局指南

- 使用推薦的電源配置圖為設(shè)備供電。

- 在每個電源引腳旁邊放置去耦電容,并靠近接地平面。

- 使用多層電路板,以方便布線并提供低電感接地平面。

- 注意過孔電感,必要時增加過孔數(shù)量和/或直徑以降低電感。

- 在敏感節(jié)點下方使用接地平面“禁止區(qū)域”,以最小化寄生電容。

五、總結(jié)

LM98620 作為一款高性能的圖像信號處理器,憑借其豐富的功能、卓越的性能和靈活的配置選項,為數(shù)字彩色復(fù)印機、掃描儀及其他圖像處理應(yīng)用提供了強大的支持。在實際應(yīng)用中,我們需要根據(jù)具體需求合理選擇功能模式、進行寄存器配置,并遵循電源供應(yīng)和布局建議,以確保設(shè)備的穩(wěn)定運行和最佳性能。希望本文能為電子工程師們在設(shè)計和應(yīng)用 LM98620 時提供有價值的參考。你在使用 LM98620 過程中遇到過哪些問題呢?歡迎在評論區(qū)分享你的經(jīng)驗和見解。

-

接口

+關(guān)注

關(guān)注

33文章

9550瀏覽量

157291 -

pga

+關(guān)注

關(guān)注

1文章

113瀏覽量

42419 -

信號處理器

+關(guān)注

關(guān)注

1文章

263瀏覽量

26246 -

串行數(shù)據(jù)

+關(guān)注

關(guān)注

0文章

69瀏覽量

16977 -

圖像信號處理

+關(guān)注

關(guān)注

0文章

20瀏覽量

7674

發(fā)布評論請先 登錄

lm98620在正常工作模式下,出現(xiàn)讀出數(shù)據(jù)全都是0的情況,為什么?

LM98620的offset寄存器值什么情況下起作用?

LM98620把寄存器設(shè)置好之后,AFE沒有輸出是怎么回事?

LM98620,pdf datasheet (10-bit

信號處理器(DSP),信號處理器(DSP)是什么意思

數(shù)字信號處理器性價比

基于LM98503的攝像機信號處理器

AD9826原文資料數(shù)據(jù)手冊PDF免費下載(成像信號處理器)

LM98620 具有 LVDS 輸出的 10 位 70 MSPS 6 通道成像信號處理器

AD9923A: CCD 信號處理器,內(nèi)置垂直驅(qū)動器和Precision Timing發(fā)生器 數(shù)據(jù)手冊

LM98620具有LVDS輸出的10位70 MSPS 6通道圖像信號處理器數(shù)據(jù)表

LM98519 10位65 MSPS 6通道成像信號處理器數(shù)據(jù)表

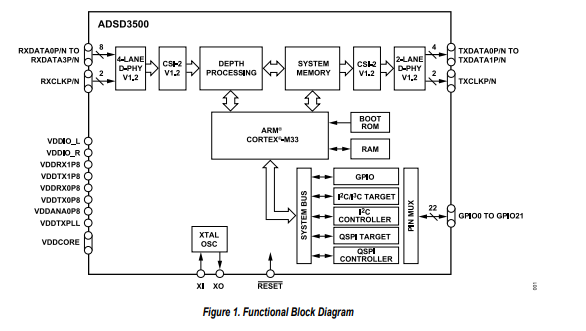

ADSD3500飛行時間深度成像信號處理器技術(shù)手冊

LM98620成像信號處理器數(shù)據(jù)手冊

LM98620成像信號處理器數(shù)據(jù)手冊

評論