引言

半導(dǎo)體器件及電路的性能會因為工藝本身固有的基本統(tǒng)計性變異 (statistical variation)而發(fā)生波動。

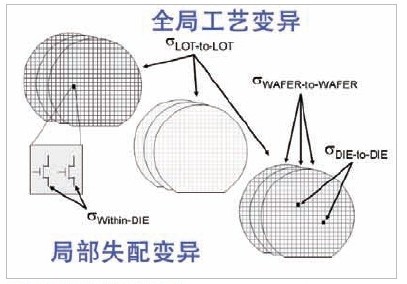

如圖1所示,所有的變異形式可劃分為好幾大類,相應(yīng)反映出工藝加工期間材料的物理分離。

批次變異是最常見的變異,因為它反映出了其它成因里所沒有的重要變異源,包括某個工藝步驟中因采用不同工具而可能帶來的差異;原始材料在批次之間的差異;以及與工具老化、定期維修、升級和調(diào)試有關(guān)的基于時間的趨勢及周期性差異。

晶圓間變異可能源于個別晶圓處理步驟中晶圓之間出現(xiàn)的輕微差異,也可能是跨越整批晶圓、由工藝因素 (比如爐管內(nèi)部的溫度和氣流梯度) 造成的梯度差異。裸片間變異則可能是由步進***的曝光差異、晶圓均質(zhì)性的梯度或晶圓局部擾動的結(jié)果。批次、晶圓和裸片間變異常常統(tǒng)稱為全局變異,因為任何一塊裸片上的所有器件都會同時地、機會相等地以同一種方式受其影響。換言之,在該裸片上,這是一個全局性的效應(yīng)。

裸片內(nèi) (器件之間) 的變異可能包括了晶圓均質(zhì)性問題引起的更局部化的裸片間變異,以及裸片薄膜厚度和邊緣清晰度、摻雜分布、結(jié)深度、表面粗糙度等方面的輕微非均質(zhì)性對個別器件清晰度構(gòu)成影響。裸片內(nèi)變異一般被稱為局部變異,因為給定裸片上每一個單獨器件的性能所受的影響各有不同。

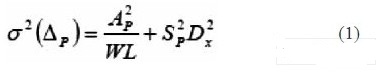

根據(jù)傅立葉變換,Pelgrometal推導(dǎo)出了_P變異的通式,兩個矩形器件之間參數(shù) P 的觀察差異表示如下:

這里,W和L分別是每個矩形的長度和寬度,Dx為矩形之間的間距,Ap和Sd則是面積和間距系數(shù)。

根據(jù) Pelgrom 模型,_P變異會隨器件尺寸的減小、并隨器件之間間距的加大而增加。局部變異還會受到一些未包含在 Pelgrom 模型中的其它布局相關(guān)因素所影響,比如鄰近器件和拓撲的存在及其距離遠近[注2及3]等。不過,一個能夠考慮到了復(fù)雜布局相關(guān)性的詳盡的失配模型其實不容易整合在一個典型的 CAD 系統(tǒng)內(nèi),所以要運用這樣的一個系統(tǒng)模型,便需要非常精密的版圖分析儀,而這就需要大量的開發(fā)工作和成本。

此外,從實際層面來看,鑒于這些器件的匹配對電路性能至為關(guān)鍵,故應(yīng)該以最優(yōu)化的方式來進行布局 (例如是并排、同向、最小間距、可比擬的鄰近拓撲等),以減少在仿真過程中要整合這些影響的需求。設(shè)計人員面臨的最大問題是確保所有關(guān)鍵匹配器件都已被識別,并確保它們的設(shè)計和布局正確,以保證匹配是在合理范圍之內(nèi),且不會因匹配精度而造成裸片尺寸不必要的增大。

MOS電流鏡的統(tǒng)計特性:

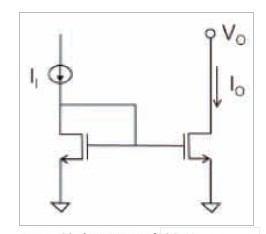

MOS 電流鏡是模擬電路最基本的組件。在圖 2 所示的基本配置中,輸入電流 Ii 被‘映射’,成為比例相同的輸出電流 Io,并相對獨立于 Vo 電壓和全局工藝變異。

在飽和狀態(tài)下,MOS器件的電流近似表示為:

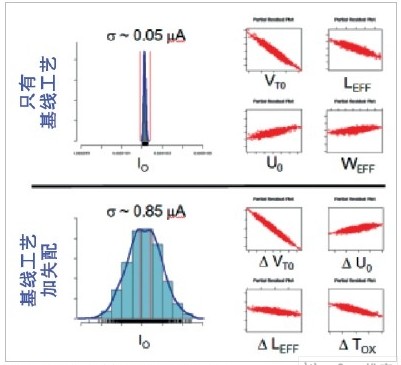

只要 MOS 器件之間的 U0、Tox、Weff、Leff 和 Vt0 的值彼此同步變化,Io 的值就能維持相當?shù)姆€(wěn)定。然而,如果局部工藝變異使到匹配器件之間出現(xiàn)輕微差異,Io上的總體變異便可能會大幅度擴大。圖 3 顯示了一個額定 Io 瞄準100μA 的簡單MOS 電流鏡的統(tǒng)計仿真結(jié)果。在這里,一個只運用了全局工藝變異的蒙特卡羅仿真使到 Io 產(chǎn)生了~0.05μA 的標準偏差,而這種變異主要是通過 Vt0 引起的;另外,Lint、Wint和 U0 對之也有一定的影響。當在蒙特卡羅仿真中加入失配變異時,Io 標準偏差便增加約 17 倍,達到~0.85μA。失配靈敏度 (mismatch sensitivity)主要是由MOS 器件之間的 delta Vt 差異來決定,而 U0、Leff 和 Tox 的失配也造成一些殘余影響。

由失配造成的 Io 變異的幅度,將取決于匹配 MOS 器件的架構(gòu)和布局。

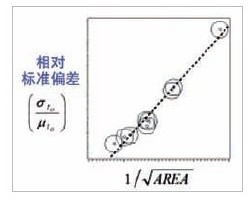

圖4所示為多個長度和寬度組合不同的NMOS 電流鏡測得的相對標準偏差 (按照?/μ計算) 綜覽。正如 Pelgrom 模型的預(yù)測所料,相對變異的幅度與面積平方根倒數(shù)成比例。

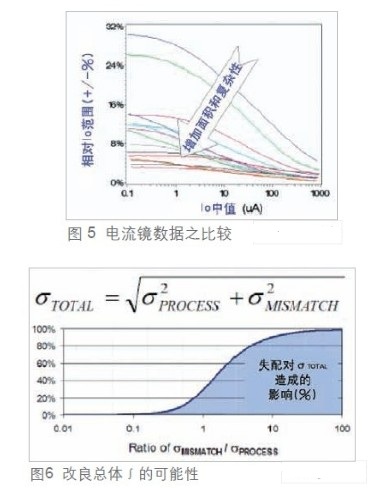

Io 變異的相對幅度還取決于電流鏡的設(shè)計工作點。圖5顯示了由多個不同配置和尺寸的電流鏡在不同測試條件下所測得、關(guān)于 Io 中值的總觀察范圍 (表示為 +/- %) 的結(jié)果。在測試中,專為極低電流下工作而設(shè)計的電流鏡相應(yīng)展示出更好的失配靈敏度。要減低這種變異,便需要更大的器件和/或更復(fù)雜的電流鏡配置,這兩種情況都會造成裸片面積更大,從而增加制造成本。

一個實際的模擬電路可能包含了多個電流鏡,再加上分對、帶隙參考電路及其它模擬構(gòu)建模塊,這些器件都可能出現(xiàn)非線性行為,須依賴匹配器件的性能以維持穩(wěn)定工作。由于在某個電路應(yīng)用中,很難明顯判斷出哪些特定器件是最關(guān)鍵的,所以經(jīng)由統(tǒng)計仿真對模擬電路進行特征化,可以大大增加產(chǎn)品成功的幾率。

統(tǒng)計CAD設(shè)計分析方法

飛兆半導(dǎo)體公司經(jīng)已開發(fā)出協(xié)助模擬電路模塊的特征化及分析的統(tǒng)計模型和工具。這種最簡單又最普通的方法是采用一系列蒙特卡羅仿真方法來檢測和隔離電路中潛在的故障點,適用于直流、瞬態(tài)或任何其它仿真設(shè)置條件。我們首先只執(zhí)行一個只有基線工藝 (baseline process-only) 的蒙特卡羅(Monte Carlo) 仿真,然后再進行一個加入失配的蒙特卡羅仿真。如果加入失配的蒙特卡羅產(chǎn)生的變異等于或大于只有工藝的蒙特卡羅所產(chǎn)生的結(jié)果,則有可能通過隔離和調(diào)低失配靈敏度來提高電路性能。

我們的統(tǒng)計 CAD 實現(xiàn)方案中已經(jīng)構(gòu)建好分區(qū) (binning) 轉(zhuǎn)換和腳本,讓設(shè)計人員可以根據(jù)器件類型和/或電路模塊對失配應(yīng)用進行劃分,以快速確定出需要進一步優(yōu)化的區(qū)域,并因此能夠?qū)@些區(qū)域里的個體實例予以標注,隔離出那些對某個特定工藝和/或失配模型參數(shù)變異敏感的器件。

這樣,設(shè)計人員便可以把精力集中在這些器件的優(yōu)化工作上,微調(diào)電路以提高可制造性和良率。

帶隙電路的分析演示

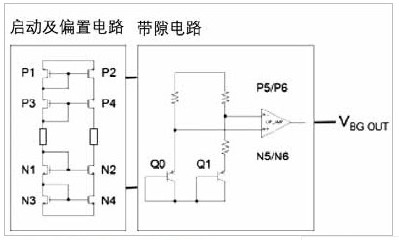

在本節(jié)里,我們將演示如何運用我們的統(tǒng)計 CAD 工具及方法,來對一個包含了 MOS 偏置發(fā)生器、PNP 帶隙參考電路和 MOS 運放的 Bi-CMOS 帶隙電路(如圖7所示)進行特征化。該電路最初的設(shè)計和仿真目的是要在工藝角模型 (corner model) 上產(chǎn)生約1.18+/- 20 mV的穩(wěn)定的參考電壓,即VBG OUT。

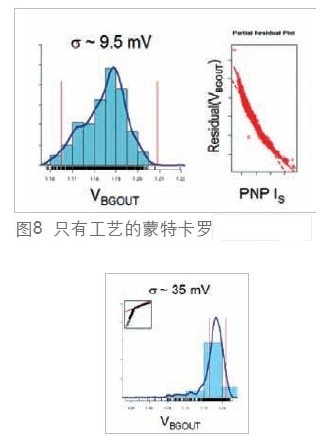

基線工藝蒙特卡羅設(shè)定VBG OUT ∫ 為 9.5mV,實際上都源于 PNP Is 變異。

基線工藝蒙特卡羅和失配蒙特卡羅相結(jié)合產(chǎn)生的變異便要大得多,而且低端尾部明顯不對稱。

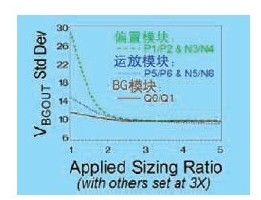

分區(qū)失配蒙特卡羅快速而準確地判斷出啟動和偏置模塊內(nèi)MOS失配靈敏度上這個尾部的:

在偏置模塊中的探測結(jié)果顯示出在器件P1和P2之間和N3 和 N4 之間(P1、P2等代號是指圖7中標注的器件) 存在“潛伏的峭壁”形狀的 _Vt 靈敏度:

除去尾部的離群值之后,剩余的失配靈敏度就可以追溯到運放中的差分對 (P5/P6) 和電流鏡 (N5/N6) ,以及帶隙中的PNP 對 (Q0/Q1)。

從35mV 到~10mV,在基線工藝和失配蒙特卡羅仿真相結(jié)合的情況下,把這些已確定的關(guān)鍵器件的尺寸增大至原尺寸的2到3倍,則可減低VBG OUT標準偏差。這時,PNP Is工藝靈敏度便成為總體VBG OUT變異的主要原因,而任何額外的失配減少措施都不能帶來更大的效益。

圖10 分區(qū)失配蒙特卡羅仿真結(jié)果

-

模擬電路

+關(guān)注

關(guān)注

126文章

1609瀏覽量

105721 -

半導(dǎo)體

+關(guān)注

關(guān)注

339文章

31154瀏覽量

266067 -

晶圓

+關(guān)注

關(guān)注

53文章

5442瀏覽量

132676

發(fā)布評論請先 登錄

分形特征的模擬電路故障診斷方法

關(guān)于謝中華編的《matlab統(tǒng)計分析與應(yīng)用:40個案例分析》

請問ThreadX原裝任務(wù)統(tǒng)計分析功能怎么實現(xiàn)?

話務(wù)統(tǒng)計分析

一種采用統(tǒng)計分析的入侵檢測原型系統(tǒng)

Excel進行電路統(tǒng)計分析

實驗結(jié)果統(tǒng)計分析與實驗論文寫作

基于Pspice的電路參數(shù)容差統(tǒng)計分析

模擬電路的統(tǒng)計特征化與CAD設(shè)計分析方法

模擬電路的統(tǒng)計特征化與CAD設(shè)計分析方法

評論