無論是4腳還是6腳,有源晶振的核心都是一個集成了振蕩電路與石英晶體的完整振蕩器,即只需提供合適電源,便能自行在輸出腳產生穩定精確的方波時鐘信號,無需外部電路。

引腳定義與區別

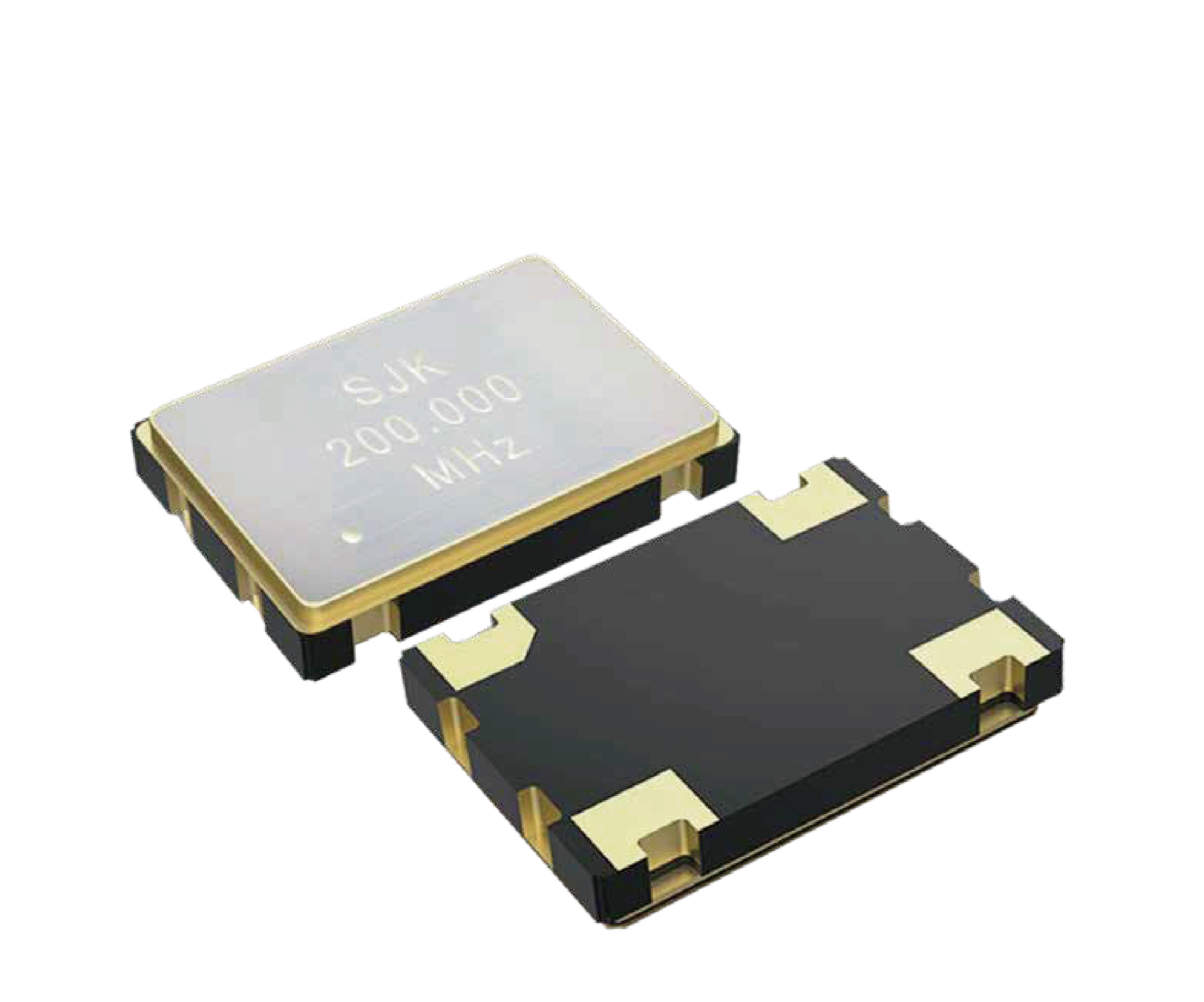

4腳有源晶振

這是最常見、最基礎的有源晶振。

引腳定義:

NC/OE: 懸空/不連接或者OE使能腳。

GND: 電源接地。

OUT: 時鐘信號輸出。

VCC: 電源正極。

特點:1腳如果是OE腳,則是一個數字控制引腳

當OE為高電平(或低電平,取決于型號)時,晶振正常輸出時鐘。

當OE為低電平(或高電平)時,晶振輸出被關閉,輸出引腳進入高阻態。這個功能非常有用,可以用于省電、熱插拔或在多個時鐘源之間進行切換。

1腳如果是NC腳:就是普通的有源晶振

如果客戶在購買有源晶振產品沒有特殊說明,通常1腳為空腳,內部不連接任何電路,PCB布線時可以懸空或接地(取決于具體型號的數據手冊,但通常建議懸空)

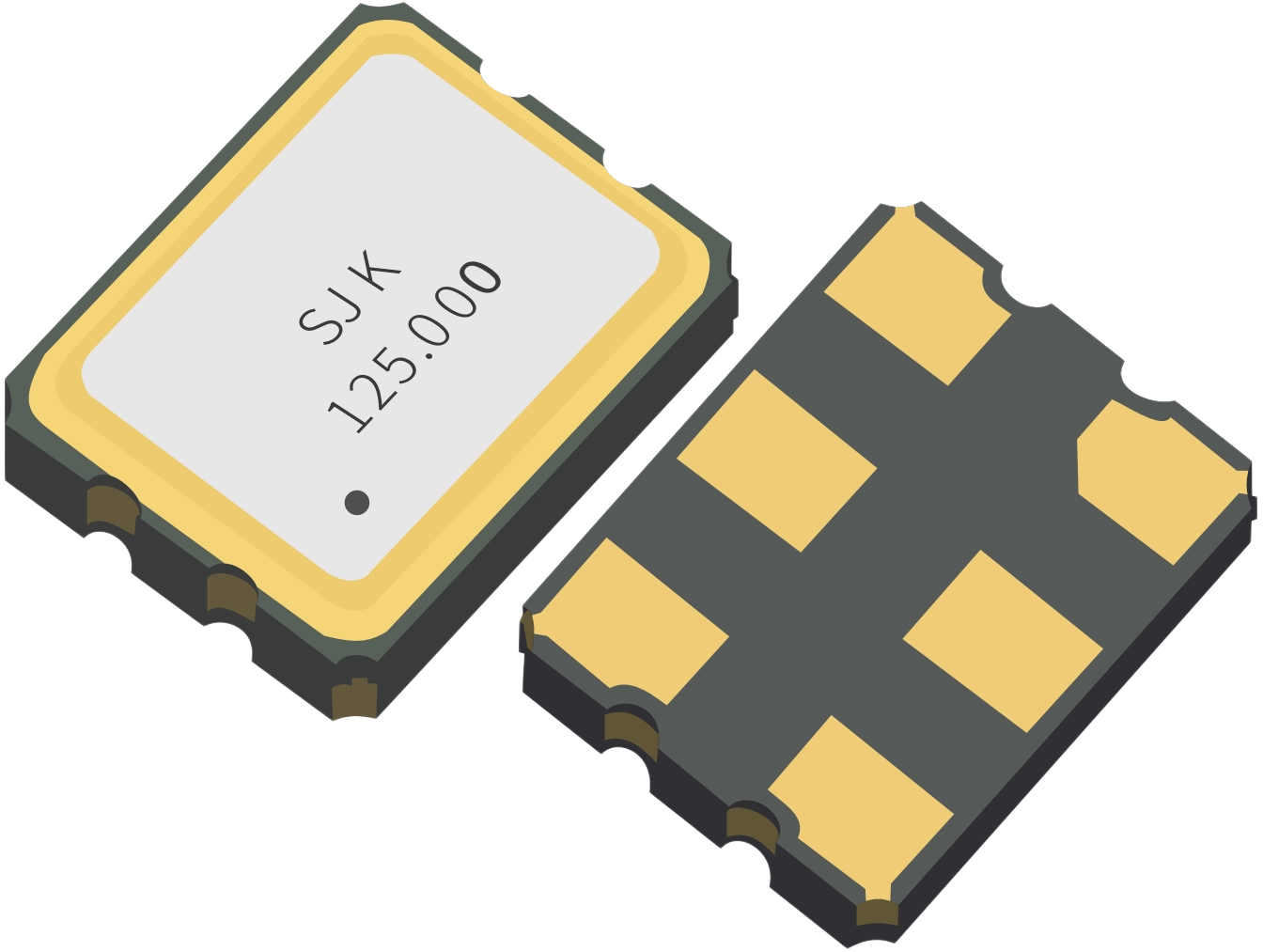

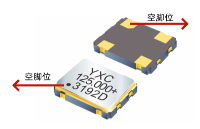

PS:通常判定1腳的位置是看產品表面絲印,如我司SJK的有源晶振產品會在1腳的正面有一個圓點標志指示為1腳,或通過引腳的形狀進行區分。

2腳為GND腳,即電源接地腳。

6腳有源晶振

6腳封裝提供了更多的功能引腳,主要有兩種類型:

類型A:增加“輸出使能”功能

引腳定義:

OE: 輸出使能。

NC: 懸空/不連接。

GND: 電源接地。

OUT: 時鐘信號輸出。

NC: 懸空/不連接。

VCC: 電源正極。

特點:

增加了OE引腳: 這是一個數字控制引腳。

當OE為高電平(或低電平,取決于型號)時,晶振正常輸出時鐘。

當OE為低電平(或高電平)時,晶振輸出被關閉,輸出引腳進入高阻態。這個功能非常有用,可以用于省電、熱插拔或在多個時鐘源之間進行切換。

類型B: 差分信號輸出

引腳定義:

OE: 輸出使能。

NC: 懸空/不連接。

GND: 電源接地。

OUT: 時鐘信號輸出。

OUT(——:差分信號互補輸出。

VCC: 電源正極。

特點:增加了OUT(——引腳:差分晶振產品LVPECL、LVDS、HCSL、CML等差分信號輸出時,會多一個差分信息互補輸出。

其中4腳和5腳都是輸出腳,只是差分信號傳輸時在這兩個腳上都傳輸信號,這兩個信號的振幅相同,相位相反。

差分晶振的作用:具有卓越的抗干擾能力、更低的電磁輻射、更低的時鐘抖動、適合長距離傳輸。

類型C: 增加“電壓控制”功能

引腳定義:

VC: 電壓控制引腳。

OE: 輸出使能。

GND: 電源接地。

OUT: 頻率輸出腳。

OUT(——)/ NC: 差分信號互補輸出腳,CMOS輸出為NC懸空-不連接。

VCC: 電源正極。

特點:

增加了VC引腳: 這實際上是一個壓控晶體振蕩器。

通過給VC引腳施加一個變化的電壓(通常在0V到VCC之間),可以在一個小范圍內微調輸出時鐘的頻率。

這個功能常用于鎖相環、頻率同步或時鐘恢復等需要動態調整頻率的電路中。

一個OE引腳: 相對于普通有源晶振,2腳為OE引腳,通過高低電平來決定晶振是否啟動,達到降低功耗等功能。

不能直接替換:4腳和6腳晶振的引腳定義部分是不兼容,絕對不能直接互相替換! 必須根據你的電路設計和芯片需求來選擇正確的型號;或者直接與我司銷售工程師進行溝通是否能直接替換。

務必查閱數據手冊:在選用任何晶振之前,一定要仔細閱讀其數據手冊。確認:

電源電壓:是3.3V,5V還是1.8V?

輸出電平:是CMOS,LVDS還是其他?

引腳定義:特別是對于6腳晶振,要確認第1腳是OE還是VC,以及其有效的電平是什么。

NC腳處理: 按照數據手冊建議處理NC腳,通常是懸空,不要連接。

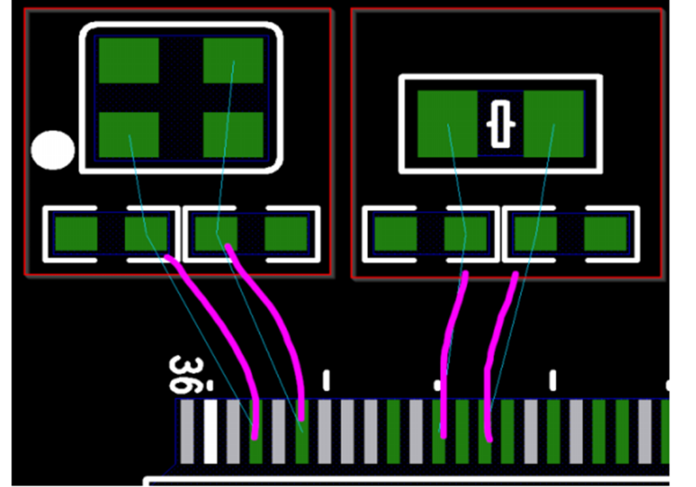

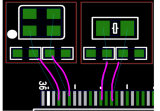

PCB布局:

晶振應盡可能靠近所用芯片的時鐘輸入引腳。

VCC引腳需要就近連接去耦電容,以濾除電源噪聲。

對于6腳有源晶振,如果OE或VC功能不需要使用,應根據數據手冊將其連接到固定的上拉或下拉電平,使其處于默認工作狀態,而不是懸空。

因此,在選擇時,你需要根據系統的具體功能需求來決定使用哪一種,并在設計和焊接時嚴格區分它們的引腳定義。

-

有源晶振

+關注

關注

1文章

994瀏覽量

22807 -

晶振

+關注

關注

35文章

3564瀏覽量

73452 -

引腳

+關注

關注

16文章

2111瀏覽量

55695

發布評論請先 登錄

有源晶振產品4個引腳和6個引腳使用上的定義

有源晶振產品4個引腳和6個引腳使用上的定義

評論