ADS424x 和 ADS422x 系列設(shè)備是 ADS42xx 超低功耗雙通道、14 位或 12 位模數(shù)轉(zhuǎn)換器(ADC)的低速變體。采用創(chuàng)新設(shè)計(jì)技術(shù)實(shí)現(xiàn)高動(dòng)態(tài)性能,同時(shí)在1.8伏供電下功耗極低。這種拓?fù)浣Y(jié)構(gòu)使ADS424x/422x非常適合多載波寬帶寬通信應(yīng)用。

*附件:ads4222.pdf

特性

- 超低功率,單一1.8伏電源,CMOS輸出:

- 183毫瓦,總功率65 MSPS

- 277毫瓦,總功率125 MSPS

- 332毫瓦總功率,160 MSPS

- 高性能性能:

- 88 dBc SFDR 頻率,頻率為 170 MHz

- 170 MHz 時(shí)的 71.4 dBFS 信噪比

- 串?dāng)_:> 90 dB,頻率為185 MHz

- 可編程增益最高可達(dá)6 dB,用于信噪比/SFDR 權(quán)衡

- 直流偏移校正

- 輸出接口選項(xiàng):

- 1.8伏并行CMOS接口

- 雙倍數(shù)據(jù)率(DDR)帶可編程擺動(dòng)的LVDS:

- 標(biāo)準(zhǔn)擺動(dòng):350 mV

- 低擺幅:200 mV

- 支持低輸入時(shí)鐘幅度至200 mV

PP - 包裝:VQFN-64(9.00毫米×9.00毫米)

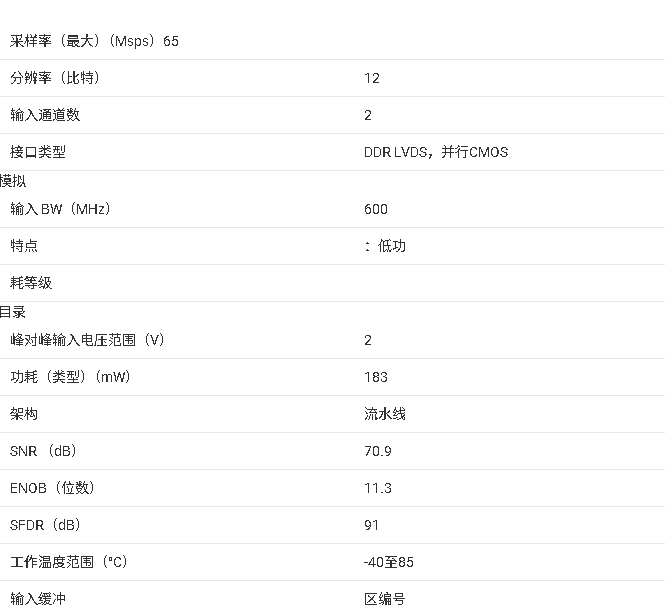

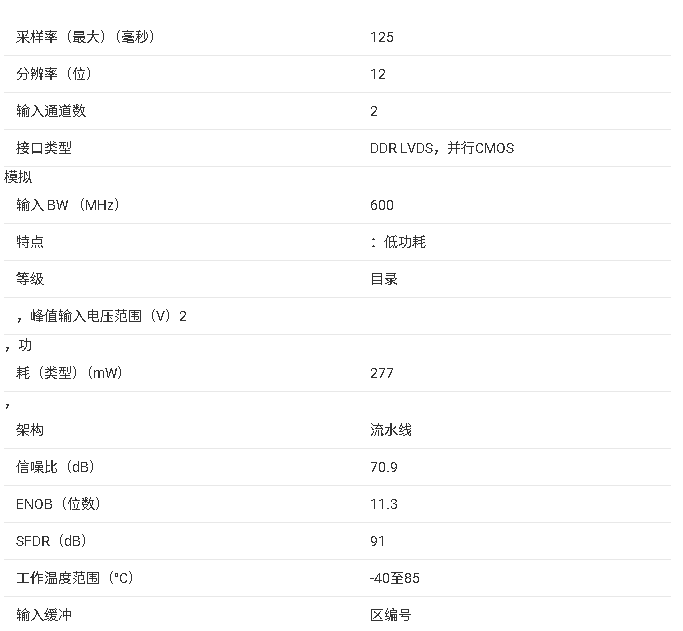

參數(shù)

方框圖

ADS42xx 系列是德州儀器(TI)推出的高動(dòng)態(tài)性能雙通道 ADC 家族,包含 12 位(ADS4222/25/26)與 14 位(ADS4242/45/46)兩個(gè)子系列,采樣率覆蓋 65MSPS-160MSPS,采用 1.8V 單電源供電,支持 DDR LVDS 與并行 CMOS 雙輸出接口,適用于無線通信基礎(chǔ)設(shè)施、軟件無線電、功率放大器線性化等對(duì)功耗和動(dòng)態(tài)性能均有嚴(yán)苛要求的寬帶信號(hào)采集場(chǎng)景。

一、芯片基礎(chǔ)信息與核心特性

1. 基礎(chǔ)規(guī)格

- 型號(hào)與文檔信息 :文檔編號(hào) SBAS533E,2011 年 3 月發(fā)布、2023 年 2 月修訂;全系列采用 64 引腳 9mm×9mm VQFN 封裝(帶裸露熱焊盤),無鉛環(huán)保設(shè)計(jì),MSL 等級(jí) 3,峰值回流焊溫度 260°C,ESD 防護(hù)等級(jí) HBM±2000V、CDM±500V,符合 RoHS 標(biāo)準(zhǔn)。

- 供電與溫度 :模擬電源(AVDD)與數(shù)字電源(DRVDD)均為 1.7V-1.9V(標(biāo)稱 1.8V),絕對(duì)最大電壓 2.1V;工作溫度 - 40°C 至 85°C,結(jié)溫最高 125°C;結(jié)到環(huán)境熱阻 23.9°C/W,熱焊盤需接地以優(yōu)化散熱。

- 引腳配置 :核心引腳包括雙通道差分模擬輸入(INP_A/INM_A、INP_B/INM_B)、差分時(shí)鐘輸入(CLKP/CLKM)、SPI 配置引腳(SEN/SCLK/SDATA/RESET)、輸出接口引腳(LVDS/CMOS 數(shù)據(jù)與時(shí)鐘)、供電(AVDD/DRVDD)及地(AGND/DRGND);VCM 引腳輸出 0.95V 共模電壓,用于模擬輸入偏置。

2. 核心性能指標(biāo)

- 分辨率與采樣率 :12 位系列(ADS422x)無失碼,14 位系列(ADS424x)支持完整 14 位分辨率;采樣率分檔:ADS4222/42 為 65MSPS,ADS4225/45 為 125MSPS,ADS4226/46 為 160MSPS,支持低速模式適配低采樣率場(chǎng)景。

- 動(dòng)態(tài)性能 :170MHz 輸入時(shí),典型 SFDR 達(dá) 88dBc,SNR 達(dá) 71.4dBFS;通道隔離度 > 90dB(185MHz),總諧波失真(THD)典型值 - 87dBc;支持 0dB-6dB 可編程增益,可權(quán)衡 SFDR 與 SNR 性能。

- 功耗與輸入特性 :160MSPS 時(shí)總功耗僅 332mW,65MSPS 時(shí)低至 183mW;模擬輸入帶寬 550MHz,支持 2VPP 差分輸入(0dB 增益),輸入共模電壓固定為 0.95V;時(shí)鐘輸入支持正弦波、LVPECL、LVDS、LVCMOS 等多種驅(qū)動(dòng)方式,最小輸入幅度 200mVPP。

二、關(guān)鍵功能與工作原理

1. 核心功能

- 雙通道同步采集 :

- 兩通道獨(dú)立采樣與轉(zhuǎn)換,支持同步工作,通道間孔徑延遲匹配誤差 ±70ps,確保多通道信號(hào)相位一致性。

- 模擬輸入采用開關(guān)電容采樣架構(gòu),內(nèi)置 RC 濾波吸收采樣毛刺,支持高阻抗信號(hào)源驅(qū)動(dòng),建議外部串聯(lián) 5Ω-15Ω 電阻抑制寄生振蕩。

- 靈活輸出與配置 :

- 輸出接口二選一:DDR LVDS(標(biāo)準(zhǔn)擺幅 350mV、低擺幅 200mV,支持 100Ω 差分端接)或并行 CMOS(1.8V 邏輯電平);數(shù)據(jù)格式支持二進(jìn)制補(bǔ)碼與偏移二進(jìn)制,可通過引腳或寄存器配置。

- 支持 SPI 串行與并行引腳兩種配置方式:SPI 可細(xì)調(diào)增益、偏移、輸出擺幅等參數(shù),并行引腳可快速切換工作模式與輸出接口類型。

- 低功耗與可靠性設(shè)計(jì) :

- 提供全局掉電與通道待機(jī)兩種低功耗模式,全局掉電功耗僅 3mW,通道待機(jī)喚醒時(shí)間 50μs,時(shí)鐘頻率低于 1MSPS 時(shí)自動(dòng)進(jìn)入低功耗狀態(tài)。

- 內(nèi)置 DC 偏移校正功能,可校正 ±10mV 偏移誤差,校正時(shí)間常數(shù)通過寄存器可編程;支持測(cè)試模式(全 0 / 全 1 / 交替碼 / 斜坡碼 / 自定義碼),便于系統(tǒng)調(diào)試。

2. 工作原理

- 外部時(shí)鐘經(jīng) CLKP/CLKM 輸入后,驅(qū)動(dòng)內(nèi)部采樣電路對(duì)雙通道模擬信號(hào)同步采樣,采樣信號(hào)經(jīng)流水線型 ADC 核心轉(zhuǎn)換為數(shù)字碼,再經(jīng)數(shù)字增益調(diào)整、偏移校正后,通過輸出接口模塊轉(zhuǎn)換為 LVDS 或 CMOS 信號(hào)輸出。

- 采樣率由輸入時(shí)鐘頻率直接決定,默認(rèn) latency 為 16 個(gè)時(shí)鐘周期,啟用數(shù)字功能后 latency 增至 24 個(gè)時(shí)鐘周期;LVDS 接口采用 DDR 模式,單差分對(duì)傳輸兩位數(shù)據(jù),有效降低引腳數(shù)量與傳輸功耗。

三、應(yīng)用場(chǎng)景與設(shè)計(jì)建議

1. 典型應(yīng)用

- 無線通信 :基站收發(fā)機(jī)、軟件無線電(SDR)的寬帶信號(hào)采集,160MSPS 采樣率可覆蓋多載波信號(hào)帶寬需求。

- 功率放大器線性化 :通過雙通道同步采集輸入 / 輸出信號(hào),實(shí)現(xiàn)預(yù)失真校正,高動(dòng)態(tài)范圍(SFDR>88dBc)確保校正精度。

- 測(cè)試測(cè)量設(shè)備 :便攜式儀器的高速數(shù)據(jù)采集模塊,低功耗特性延長(zhǎng)電池續(xù)航,寬輸入帶寬適配多種傳感器信號(hào)。

2. 設(shè)計(jì)注意事項(xiàng)

- 電源與去耦 :

- AVDD 與 DRVDD 需獨(dú)立供電,建議使用低噪聲 LDO,避免開關(guān)電源噪聲耦合;每個(gè)電源引腳就近并聯(lián) 0.1μF 陶瓷去耦電容,熱焊盤與地平面可靠連接。

- 模擬地與數(shù)字地單點(diǎn)連接,電源路徑采用 PI 濾波結(jié)構(gòu)隔離,減少數(shù)字電路對(duì)模擬電路的干擾。

- 輸入與時(shí)鐘設(shè)計(jì) :

- 模擬輸入需偏置在 0.95V 共模電壓,差分輸入阻抗隨頻率變化,高頻信號(hào)(>150MHz)建議采用變壓器耦合驅(qū)動(dòng),低頻信號(hào)可使用差分運(yùn)放驅(qū)動(dòng)。

- 時(shí)鐘源需低抖動(dòng)(推薦外部時(shí)鐘抖動(dòng) < 100fs),支持差分或單端輸入,時(shí)鐘占空比 35%-65% 均可穩(wěn)定工作,高頻場(chǎng)景建議使用 LVPECL 時(shí)鐘驅(qū)動(dòng)以優(yōu)化抖動(dòng)性能。

- 布局與接口 :

- 差分模擬輸入對(duì)與時(shí)鐘信號(hào)垂直布線,減少串?dāng)_;模擬區(qū)域與數(shù)字區(qū)域嚴(yán)格分區(qū),裸露熱焊盤通過過孔陣列連接至地平面。

- LVDS 輸出走線需阻抗匹配(100Ω),長(zhǎng)度匹配誤差控制在 5ps 內(nèi);CMOS 輸出建議串聯(lián) 50Ω 電阻,降低負(fù)載電容影響,傳輸距離不超過數(shù)英寸。

四、關(guān)鍵配置要點(diǎn)

- 增益與偏移校正 :通過寄存器配置 0dB-6dB 增益(0.5dB 步進(jìn)),高輸入頻率場(chǎng)景(>200MHz)啟用高增益可提升 SFDR;偏移校正需先使能 EN DIGITAL 位,再開啟 OFFSET CORR 位,校正時(shí)間常數(shù)根據(jù)采樣率選擇。

- 輸出接口配置 :并行引腳 SEN 可快速切換輸出接口類型,SPI 配置可細(xì)調(diào) LVDS 輸出擺幅(125mV-570mV);多設(shè)備同步時(shí),可通過調(diào)整 CLKOUT 相位(±450ps)優(yōu)化數(shù)據(jù)對(duì)齊。

- 低功耗優(yōu)化 :無需雙通道時(shí)可將閑置通道置于待機(jī)模式,采樣率低于 80MSPS 時(shí)可啟用低速模式,進(jìn)一步降低功耗;CMOS 輸出模式下,通過減少輸出引腳切換頻率降低動(dòng)態(tài)功耗。

-

adc

+關(guān)注

關(guān)注

100文章

7511瀏覽量

555974 -

可編程

+關(guān)注

關(guān)注

2文章

1325瀏覽量

41488 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

4013瀏覽量

130105 -

寬帶寬

+關(guān)注

關(guān)注

0文章

46瀏覽量

1356

發(fā)布評(píng)論請(qǐng)先 登錄

AD9268: 16位、80 MSPS/105 MSPS/125 MSPS、1.8 V雙通道模數(shù)轉(zhuǎn)換器(ADC)

AD10265:帶模擬輸入信號(hào)調(diào)理數(shù)據(jù)表的雙通道、12位、65 MSPS A/D轉(zhuǎn)換器

AD644:14位,40 MSPS/65 MSPS模擬到數(shù)字轉(zhuǎn)換器數(shù)據(jù)Sheet

AD10265:雙通道、12位、65 MSPS A/D轉(zhuǎn)換器,具有模擬輸入信號(hào)調(diào)理功能,數(shù)據(jù)表陳舊

ADC12xJ800四通道/雙通道/單通道800MSPS 12位模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADS42xx雙通道、14位/12位、160MSPS/125MSPS/65MSPS、超低功耗ADC數(shù)據(jù)表

ADS5553高性能、雙通道、14位、65 MSPS模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADS8363雙通道、16位、1 MSPS模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

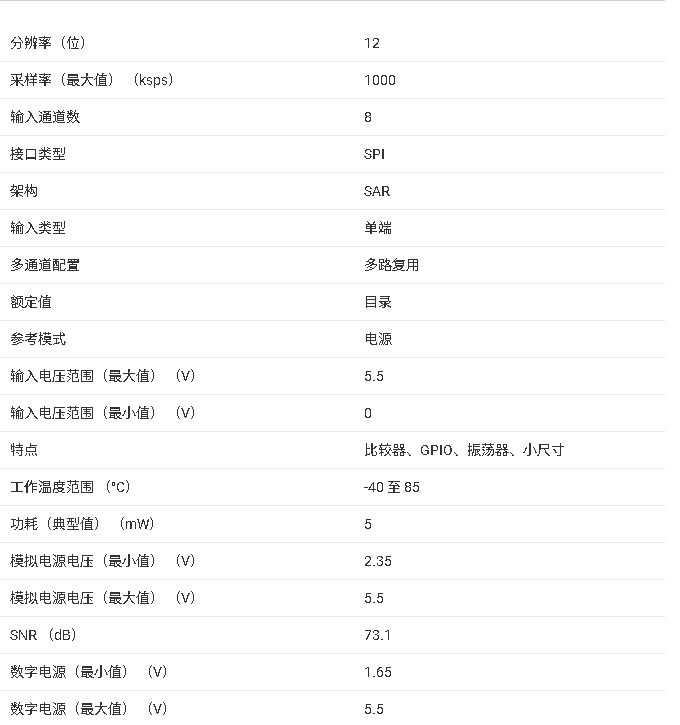

ADS7028 小型 8 通道 12 位模數(shù)轉(zhuǎn)換器技術(shù)手冊(cè)

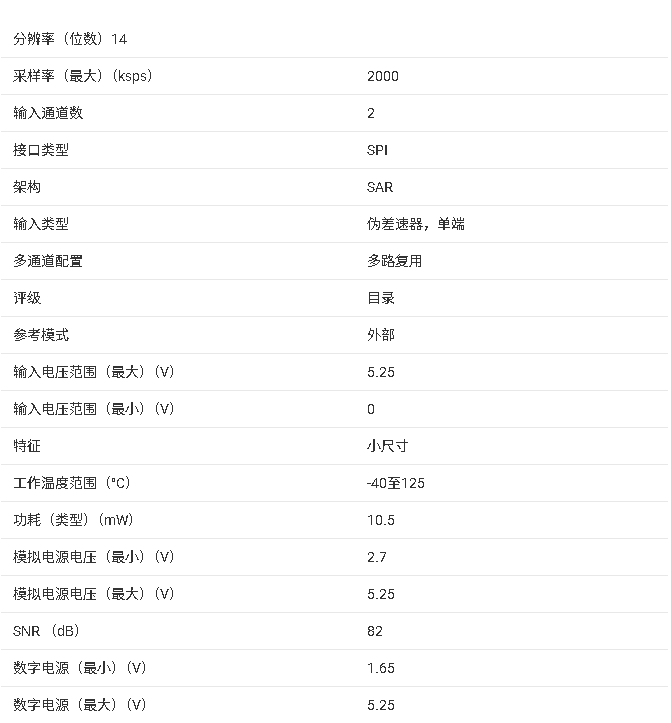

ADS7946 雙通道 14 位 2 MSPS 超低功耗 ADC 技術(shù)文檔總結(jié)

ADS4225 雙通道、12位、125 MSPS的模擬轉(zhuǎn)數(shù)字轉(zhuǎn)換器(ADC)技術(shù)手冊(cè)

ADS4242 雙通道,14位,65 MSPS 的模擬轉(zhuǎn)數(shù)字轉(zhuǎn)換器(ADC)技術(shù)手冊(cè)

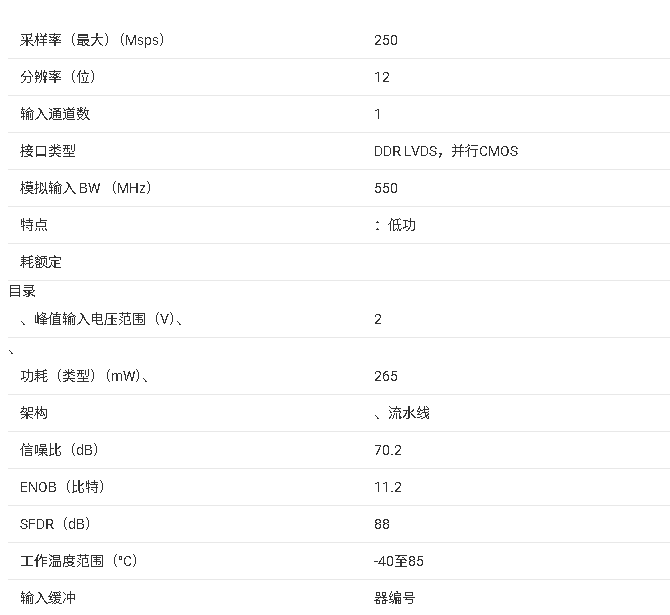

ADS4129 12位,250 MSPS 模擬轉(zhuǎn)數(shù)字轉(zhuǎn)換器(ADC)技術(shù)手冊(cè)

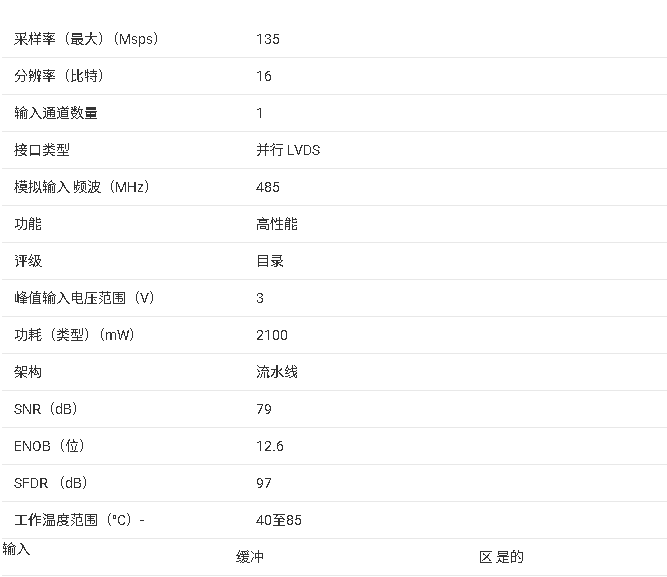

ADS5483 16位,135 MSPS 模擬轉(zhuǎn)數(shù)字轉(zhuǎn)換器(ADC)技術(shù)手冊(cè)

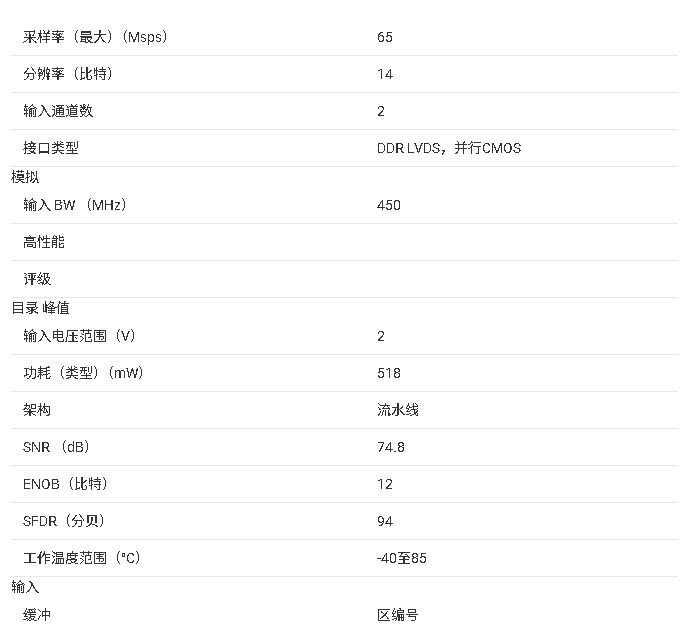

ADS62P42 雙通道,14位,65 MSPS 的模擬轉(zhuǎn)數(shù)字轉(zhuǎn)換器(ADC)技術(shù)手冊(cè)

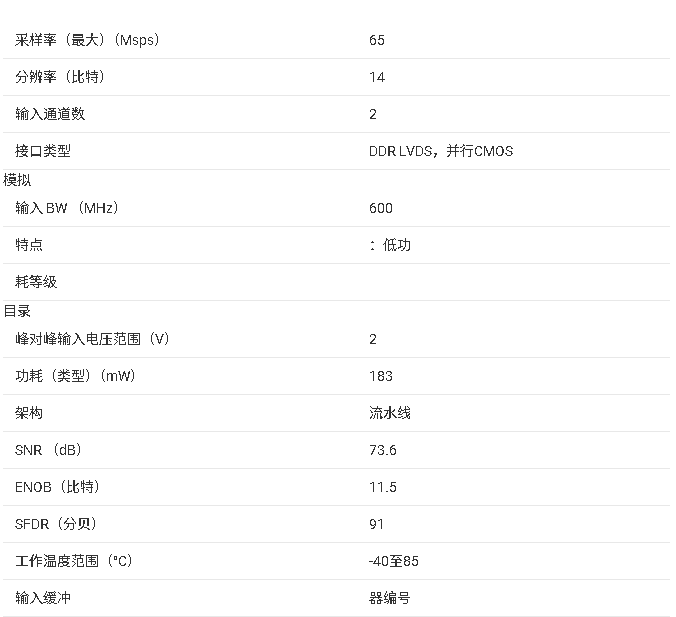

ADS4222 雙通道、12位、65 MSPS 的模擬轉(zhuǎn)數(shù)字轉(zhuǎn)換器(ADC)技術(shù)手冊(cè)

ADS4222 雙通道、12位、65 MSPS 的模擬轉(zhuǎn)數(shù)字轉(zhuǎn)換器(ADC)技術(shù)手冊(cè)

評(píng)論