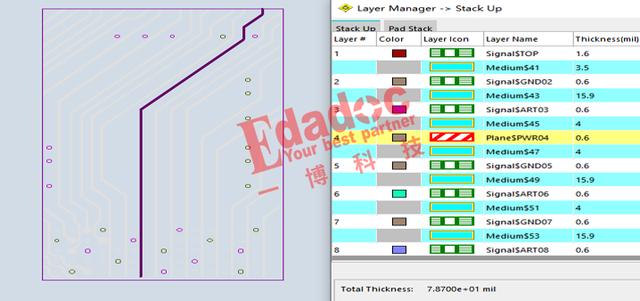

怎樣把TOP面的器件、shape、via、走線一起mirror到BTO層?

解答:用16.3以上版本可以輕松做到將需要mirror的部分建成一個模塊復用文件,然后再復用它,復用時可以在放置過程中右鍵選擇整體mirror。

以一個中心點MIRROR器件并移到旁邊(用IX多少),然后以那個中心點復制孔-右鍵-MIRROR GEOMRTRY再移到IX多少和器件一個距離就好了

用placement edit的模式, 然后再框選要mirror的器件之后,再點擊右鍵選擇 place replicate create 創建一個MDD文件就可以復用了

奈因科技--專注于高速高密度PCB板設計

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

BTO

+關注

關注

0文章

7瀏覽量

8935 -

Mirror

+關注

關注

0文章

5瀏覽量

9487 -

TOP

+關注

關注

0文章

37瀏覽量

33238

原文標題:怎樣把TOP面的器件、shape、via、走線一起mirror到BTO層?

文章出處:【微信號:Line_pcblayout,微信公眾號:Line_pcblayout】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

PCB板雙面布局的DDR表底走線居然不一樣

的想法,所以前面的一些走線長度和阻抗的優化調整意見給到他們的時候,他們也能夠接受,并且表示贊同。當我們提出最后一項優化方案后,他們就表示出了深深的不太理解了。

這

發表于 12-11 10:43

EXCUSE ME,表層的AC耦合電容和PCB內層的高速線會有串擾?

線在L3層,中間L2層是地平面的這種情況。那就回到了題目和摘要說的問題了,根據電磁場理論,電容在表層,走

發表于 12-10 10:00

聊聊怎么把 SAW 濾波器量“準”:VNA、S 參數和群時延那些坑

太低,容差過大

PCB 走線長、轉折多,耦合嚴重

測試環境周邊有較強干擾源

5.3 和數據手冊完全對不上

可以把以下資料打包發給原廠或代理技術支持一起看:

VNA 型號、校準方式、掃頻參數

測試板照片

發表于 11-19 17:38

到底DDR走線能不能參考電源層啊?

。就像下面這個3D仿真模型展示的一樣。

要不。。。我們還是首先來看看如果是L3層的這根地址信號上下都是地平面的常規情況的結果吧,也就是把上面的

發表于 11-11 17:46

sc-1和sc-2可以一起用嗎

SC-1和SC-2可以一起使用,但需遵循特定的順序和工藝條件。以下是其協同應用的具體說明:分步實施的邏輯基礎SC-1的核心作用:由氨水(NH?OH)、過氧化氫(H?O?)和水組成,主要去除硅片表面的

光纖能與電線一起走嗎

光纖與電線在特定條件下可以一起布線,但需嚴格遵守安全規范和物理隔離要求,以下是詳細分析: 一、光纖與電線的物理特性差異 光纖 傳輸介質:以光信號傳輸數據,不導電,因此不受電磁干擾(EMI

PCB Layout中的三種走線策略

布線(Layout)是PCB設計工程師最基本的工作技能之一。走線的好壞將直接影響到整個系統的性能,大多數高速的設計理論也要最終經過Layout得以實現并驗證,由此可見,布線在高速PCB

發表于 03-13 11:35

【PCB】四層電路板的PCB設計

手工方式將元器件安排在恰當的位置上;在布線過程中,再根據實際需要進行調整,以進一步提高布通率。

2 布線

布線是在布局之后,通過設汁銅箔的走線圖,按照原理圖連通所有的走

發表于 03-12 13:31

屏蔽網線可以和電線一起嗎

屏蔽網線與電線不建議一起走線,原因主要有以下幾點: 電磁干擾:電源線在傳輸電能時會產生電磁場,而屏蔽網線中的導線可能會受到這個電磁場的干擾。這種干擾可能導致屏蔽網線的信號質量下降、速度

怎樣把TOP面的器件、shape、via、走線一起mirror到BTO層

怎樣把TOP面的器件、shape、via、走線一起mirror到BTO層

評論