該ADS62P19是采樣率高達250 MSPS的雙通道、11位模數轉換器(ADC)系列的一部分。該器件在緊湊的QFN-64封裝中結合了高動態性能和低功耗。此功能使該器件非常適合多載波、寬帶寬通信應用。

該ADS62P19具有增益選項,可用于在較低滿量程輸入范圍內提高無雜散動態范圍(SFDR)性能。該器件包括一個直流失調校正環路,可用于消除ADC失調。提供雙倍數據速率 (DDR)、低壓差分信號 (LVDS) 和并行互補金屬氧化物半導體 (CMOS) 數字輸出接口。

*附件:ads62p19.pdf

盡管該器件包含內部基準電壓源,但取消了傳統的基準引腳和相關的去耦電容器。然而,該器件也可以通過外部基準電壓源驅動。該器件的額定工作范圍為工業溫度范圍(–40°C 至 +85°C)。

特性

- 最大采樣率:250 MSPS

- 11 位分辨率

- 總功率:250 MSPS 時為 1.25 W

- 輸出選項:

- DDR LVDS和并行CMOS

- 可編程增益:

- SNR和SFDR權衡高達6 dB

- 直流偏移校正

- 串擾:90 dB

- 支持低至 400 mV 的輸入時鐘幅度

聚丙烯微分 - 內部和外部基準支持

- 封裝:9 毫米× 9 毫米 QFN-64

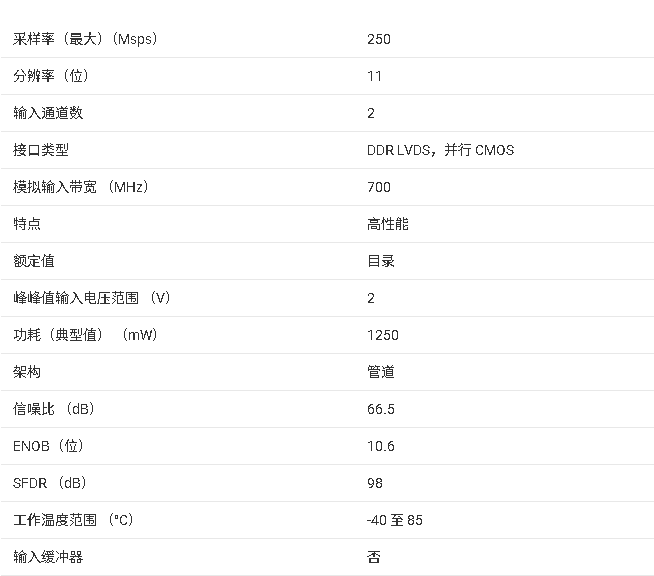

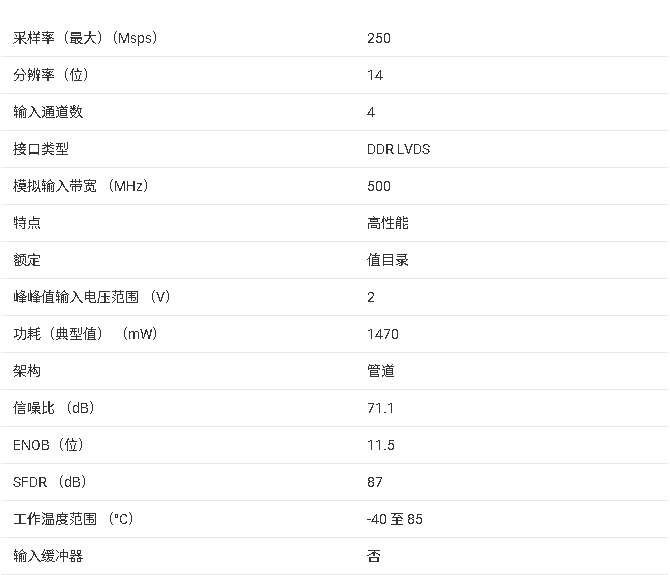

參數

方框圖

ADS62P19 是一款雙通道 11 位 250 MSPS 模數轉換器(ADC),支持 DDR LVDS 與并行 CMOS 雙輸出接口,具備可編程增益、直流偏移校正及低串擾特性,以高動態性能和緊湊封裝適用于多載波寬帶通信、測試測量等高速信號采集場景。

核心參數與性能

- 分辨率與線性度 :11 位分辨率,微分非線性(DNL)±0.1 LSB,積分非線性(INL)±2.5 LSB,無丟失碼。

- 采樣率與輸入特性 :最高采樣率 250 MSPS(LVDS 接口)、210 MSPS(CMOS 接口);模擬輸入帶寬 700 MHz,差分輸入范圍 2 VPP,共模電壓 1.5 V。

- 動態性能 :170 MHz 輸入時,信噪比(SNR)64 dBFS,無雜散動態范圍(SFDR)75 dBc(0 dB 增益)、82 dBc(6 dB 增益);串擾抑制 90 dB,三階互調失真(IMD3)86.4 dBc。

- 功耗與工作條件 :總功耗 1.25 W(250 MSPS);模擬電源 3.3 V,數字電源 1.8 V;工作溫度 -40°C 至 85°C。

封裝與引腳

- 采用 9 mm×9 mm 64 引腳 QFN(RGC)封裝,底部帶熱焊盤用于散熱,引腳包含模擬 / 數字電源、差分模擬輸入(INP_A/INM_A、INP_B/INM_B)、差分時鐘輸入(CLKP/CLKM)、雙路輸出接口及配置控制引腳。

- 關鍵引腳功能:VCM 提供 1.5 V 共模電壓,RESET 用于寄存器復位,SEN/SCLK/SDATA 構成串行配置接口,CTRL1-CTRL3 控制掉電模式。

核心功能與特性

- 靈活輸出接口 :支持 DDR LVDS(100 Ω 差分終端)與并行 CMOS 輸出,數據格式可選二進制補碼或偏移二進制,LVDS 模式下單差分對復用兩位數據,提升傳輸效率。

- 增益與偏移校正 :增益 0-6 dB 可編程(0.5 dB 步進),可權衡 SFDR 與 SNR;內置直流偏移校正環路,支持 ±10 mV 偏移補償,校正時間常數可編程。

- 低功耗與掉電模式 :支持全局掉電(功耗 45 mW)、單通道待機(喚醒時間 1 μs)及低速率自動低功耗模式,適配不同功耗需求場景。

- 配置方式 :支持并行引腳直接配置(接口類型、參考源等)與串行 SPI 配置(增益、偏移、測試模式等),寄存器支持讀回驗證。

典型應用場景

- 多載波寬帶通信系統、軟件無線電(SDR)、雷達信號采集、測試測量儀器、有線頭端設備。

設計要點

- 電源與去耦 :模擬電源(AVDD)與數字電源(DRVDD)需獨立供電,就近配置 0.1 μF 陶瓷去耦電容,敏感電源路徑遠離數字噪聲源。

- 輸入與時鐘設計 :模擬輸入建議串聯 5-15 Ω 電阻抑制寄生振蕩,采用差分驅動提升抗干擾性;時鐘輸入支持 LVPECL/LVDS/CMOS 電平,需選用低抖動時鐘源(如 CDCE62005),推薦差分驅動。

- 布局規范 :PCB 劃分模擬區、數字區與時鐘區,單點接地;LVDS 信號線按 100 Ω 阻抗控制、等長差分布線;熱焊盤通過過孔充分接地,減少散熱瓶頸。

- 配置要點 :上電后需通過 RESET 引腳復位初始化寄存器;串行接口最高 20 MHz 時鐘,可配置增益、偏移校正時間常數及輸出測試模式(全 0 / 全 1/.toggle 等)。

產品型號與供貨

- 在售型號為 ADS62P19IRGCR(2000 片 / 大卷帶)與 ADS62P19IRGCT(250 片 / 小卷帶),均符合 RoHS 標準,MSL 等級 3(260°C 回流焊,168 小時濕度敏感)。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

封裝

+關注

關注

128文章

9249瀏覽量

148615 -

adc

+關注

關注

100文章

7511瀏覽量

555946 -

模數轉換器

+關注

關注

26文章

4013瀏覽量

130102 -

數字輸出

+關注

關注

0文章

56瀏覽量

9195

發布評論請先 登錄

相關推薦

熱點推薦

ADS62P19輸出LVDS數據的疑問求解

ADS62P19的datasheet第54頁關于LVDS的數據輸出有如下表述:

偶數標號的數據在CLKOUTP的上升沿采樣,奇數編號的數據在CLKOUTP的下降沿采樣。但是下面圖中顯然和該說

發表于 01-08 06:19

關于ADS62P19模擬輸入驅動電路的疑問求解

您好。關于ADS62P19模擬輸入驅動電路我有些疑問,還請指教。

在我的系統中輸入ADC的信號頻率范圍從1MHz-100MHz,從Figure 45和Figure 46中可以看出在頻率小于

發表于 01-08 06:48

更改ads62p49的采樣率設置,是只改AD9516給ads62p49的輸出時鐘就行還是ads62p49的設置也要同步改變?

想麻煩請教下TI工程師,我現在用ads62p49芯片實現8路AD同步輸入,采樣時鐘用AD9516芯片提供LVDS類型時鐘,整個AD采集卡通過FMC接口與FPGA相連。拿到的demo程序是250M

發表于 01-10 07:32

ADS62P49 / ADS62P29/ADS62P48 /

The ADS62Px9/x8 is a family of dual channel 14-bit and 12-bit A/D converters with sampling rates up

發表于 06-04 09:46

?38次下載

ADS62P45/ADS62P44/A62P43/ADS62

ADS62P4X is a dual channel 14-bit A/D converter family with maximum sample rates up to 125 MSPS.

發表于 06-04 09:55

?33次下載

ADS62P42/ADS62P43/ADS62P44/ADS

general description of the features and functions to be considered while using this module. This manual is applicable to the ADS62P

發表于 06-04 10:01

?19次下載

ADS62P45/ ADS62P44/ADS62P43/AD

ADS62P4X is a dual channel 14-bit A/D converter family with maximum sample rates up to 125 MSPS.

發表于 06-04 10:05

?26次下載

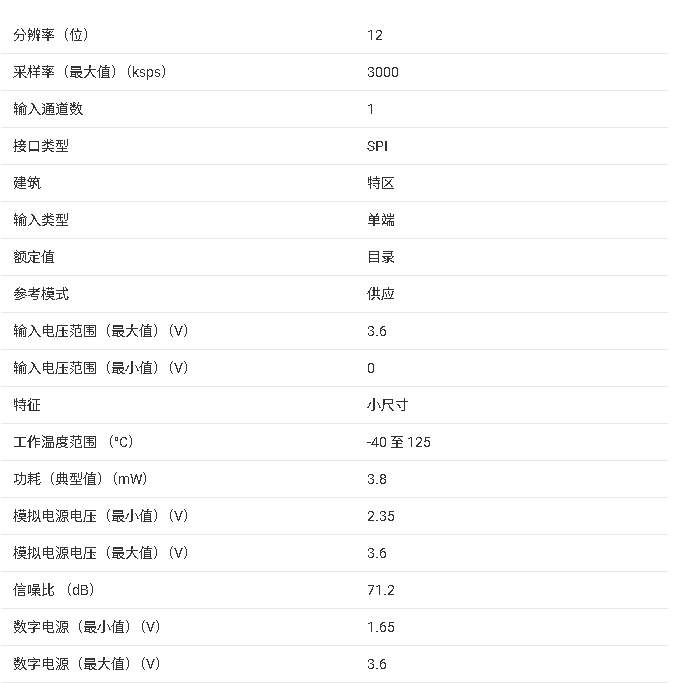

ADS7046 產品核心信息總結

該ADS7046器件屬于引腳對引腳兼容、高速、低功耗、單通道逐次逼近寄存器 (SAR) 型模數轉換器 (ADC) 系列。該器件系列包括多種分辨率、吞吐量和模擬輸入變體(器件列表見表 1)。

該

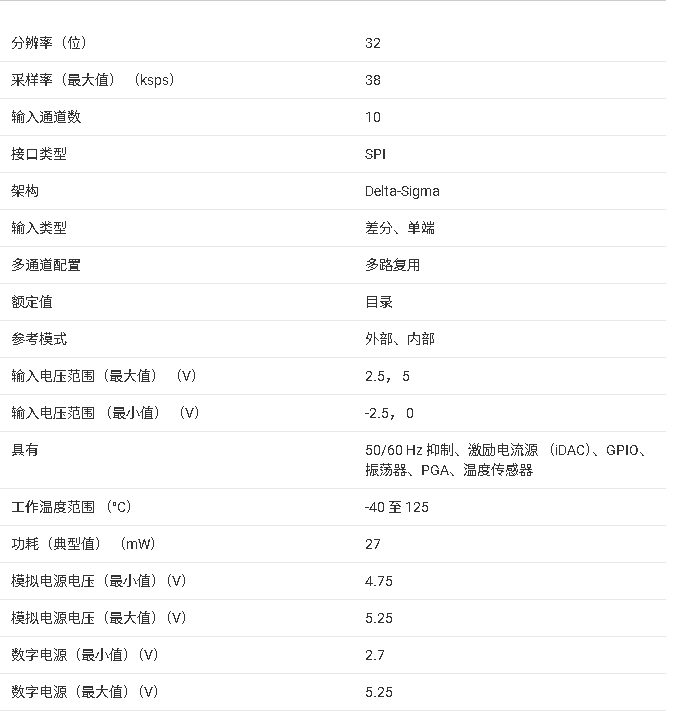

ADS1262/ADS1263 產品核心信息總結

ADS1262和ADS1263 (ADS126x)是低噪聲、低漂移、38.4kSPS、三角積分 (ΔΣ) ADC,集成了PGA、基準電壓源和內部故障監控器。該ADS1263集成了一個用

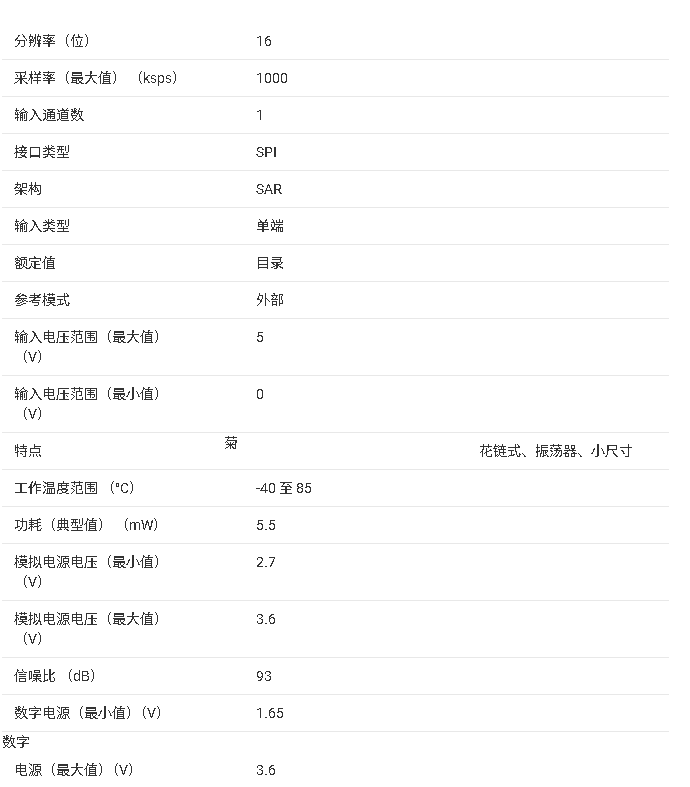

ADS8860 產品核心信息總結

該ADS8860是一款 16 位、1 MSPS、單端輸入、模數轉換器 (ADC)。該器件采用2.5V至5V外部基準電壓源工作,提供廣泛的信號范圍選擇,無需額外的輸入信號縮放。基準電壓設置獨立于模擬電源電壓 (AVDD),并且可能超過模擬電源電壓 (AVDD)。

ADS4449 產品核心信息總結

該ADS4449是一款高線性度、四通道、14位、250MSPS、模數轉換器(ADC)。該器件專為低功耗和高無雜散動態范圍 (SFDR) 而設計,在較大的輸入頻率范圍內具有低噪聲性能和出色的 SFDR。

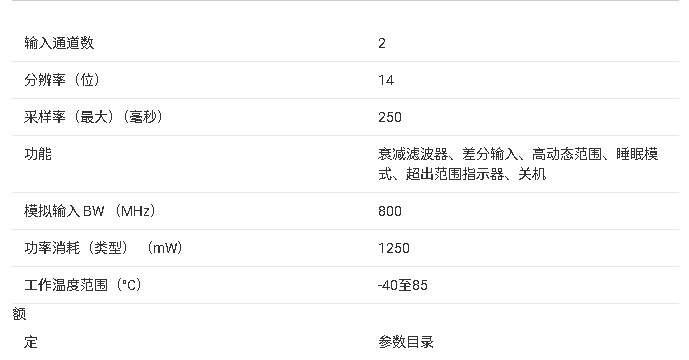

ADS62PF49 雙通道反饋接收器產品總結

該ADS62PF49為雙通道反饋接收IC,采樣率最高可達250 MSPS。它允許在有限時間內輸出高分辨率的14位,隨后是最低8倍時間的低分辨率模式。它與ADS62P49和ADS62C17雙數轉換器

ADS62P19 產品核心信息總結

ADS62P19 產品核心信息總結

評論