該ADS54J69是一款低功耗、寬帶寬、16位、500MSPS、雙通道模數(shù)轉(zhuǎn)換器(ADC)。該器件專為高信噪比 (SNR) 而設(shè)計(jì),可提供 –159 dBFS/Hz 的本底噪聲,適用于在寬瞬時帶寬上實(shí)現(xiàn)最高動態(tài)范圍的應(yīng)用。該器件支持?jǐn)?shù)據(jù)速率高達(dá) 10.0 Gbps 的JESD204B串行接口,每個 ADC 支持一個或兩個通道。緩沖模擬輸入在寬頻率范圍內(nèi)提供均勻的輸入阻抗,并最大限度地減少采樣保持毛刺能量。每個ADC通道直接連接到寬帶數(shù)字下變頻器(DDC)模塊。該ADS54J69在較大的輸入頻率范圍內(nèi)以極低的功耗提供出色的無雜散動態(tài)范圍 (SFDR)。

JESD204B接口減少了接口線的數(shù)量,從而實(shí)現(xiàn)了高系統(tǒng)集成密度。內(nèi)部鎖相環(huán)(PLL)將ADC采樣時鐘相乘,以得出用于序列化每個通道的16位數(shù)據(jù)的位時鐘。

*附件:ads54j69.pdf

特性

- 16位分辨率、雙通道、500MSPS ADC

- 空閑通道本底噪聲:–159 dBFS/Hz

- 光譜性能 (f

在= 170 MHz,–1 dBFS):- 信噪比:73 dBFS

- NSD:–157 dBFS/Hz

- SFDR:93 dBc

- SFDR:94 dBc(HD2、HD3 和交錯音除外)

- 光譜性能 (f

在= 310 MHz,–1 dBFS):- 信噪比:71.7 dBFS

- NSD:–155.7 dBFS/Hz

- SFDR:81 dBc

- SFDR:94 dBc(HD2、HD3 和交錯音除外)

- 信道隔離:100 dBc(f

在= 170兆赫 - 輸入滿量程:1.9 V

聚丙烯 - 輸入帶寬 (3 dB):1.2 GHz

- 片上抖動

- 集成 Decimate-by-2 濾波器

- JESD204B 支持子類 1 的接口:

- 每個ADC1通道,速率為10.0 Gbps

- 每個ADC2通道,頻率為5.0 Gbps

- 支持多芯片同步

- 功耗:1.35 W/ch(500 MSPS 時)

- 72引腳VQFNP封裝(10 mm×10 mm)

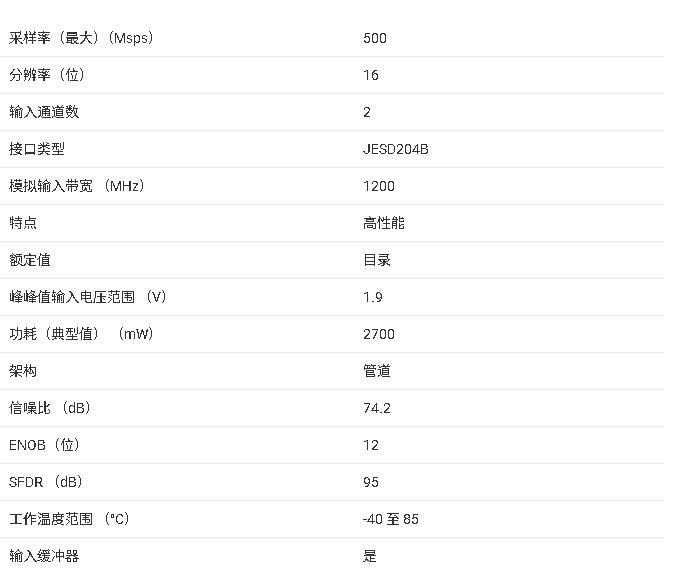

參數(shù)

方框圖

ADS54J69 是德州儀器(Texas Instruments)推出的一款低功耗、寬帶寬雙通道模數(shù)轉(zhuǎn)換器,核心優(yōu)勢是高分辨率與優(yōu)異動態(tài)性能兼具,集成 2 倍抽取濾波器和高速 JESD204B 接口,適用于雷達(dá)、寬帶無線通信、醫(yī)療影像等對高頻信號采樣精度有嚴(yán)苛要求的場景。

一、核心性能與定位

- 分辨率與采樣速率 :16 位分辨率,單通道最高 500 MSPS 采樣率,采用四片交錯 ADC 架構(gòu),通道隔離度達(dá) 100 dBc(170 MHz 輸入)。

- 動態(tài)性能 :170 MHz 輸入、-1 dBFS 條件下,SNR 達(dá) 73 dBFS,SFDR 為 93 dBc(排除 HD2、HD3 及交錯雜波后達(dá) 94 dBc),噪聲譜密度(NSD)低至 - 157 dBFS/Hz;3 dB 輸入帶寬達(dá) 1.2 GHz,支持高頻信號直接采樣。

- 功耗與溫度適應(yīng)性 :單通道典型功耗 1.35 W(500 MSPS),全局掉電模式功耗低至 204 mW;工作溫度范圍 - 40℃~85℃,結(jié)溫最高 125℃。

二、關(guān)鍵功能與硬件特性

1. 信號處理與校正

- 集成寬頻數(shù)字下變頻器(DDC),內(nèi)置 2 倍抽取半帶 FIR 濾波器,支持低通 / 高通模式,阻帶衰減約 90 dB,通帶平坦度 ±0.05 dB;

- 內(nèi)置抖動(Dither)功能和交錯校正算法,降低雜波干擾,提升頻譜純凈度;

- 支持可編程快速過范圍(FOVR)檢測,閾值可配置,響應(yīng)延遲為 18 個時鐘周期 + 4 ns。

2. 接口與封裝

- 數(shù)字輸出:JESD204B 子類 1 接口,支持單 ADC 1 路(10 Gbps)或 2 路(5 Gbps)通道配置,支持多芯片同步;

- 配置接口:24 位 SPI 接口(支持 1.2V~1.9V 邏輯),支持分頁訪問寄存器,可配置濾波、增益、功耗等參數(shù);

- 封裝規(guī)格:72 引腳 VQFNP 封裝(10mm×10mm),底部裸露熱焊盤,優(yōu)化散熱性能。

3. 電源與輸入特性

- 電源配置:模擬電源 AVDD(1.9V)、AVDD3V(3.0V),數(shù)字電源 DVDD(1.9V)、IOVDD(1.15V),需先啟動 IOVDD 再啟動 DVDD 以確保寄存器加載正常;

- 模擬輸入:差分輸入滿量程 1.9 Vpp,共模電壓 2.1 V,內(nèi)置 600Ω 偏置電阻,支持 AC/DC 耦合,輸入阻抗在 170 MHz 時為 0.6 kΩ(差分)、4.7 pF(差分)。

三、工作模式與配置

- 抽取濾波模式 :DDC 模塊支持 2 倍抽取(低通 / 高通濾波),抽取后采樣率可降至 250 MSPS,SNR 提升約 3 dB;

- 電源模式 :支持全局掉電、單通道 ADC / 緩沖器掉電等多種功耗控制模式,掉電喚醒時間約 150 μs;

- 測試模式 :JESD204B 接口支持 PRBS(21?-1)、K28.5 等測試圖案,便于系統(tǒng)調(diào)試。

四、典型應(yīng)用場景

- 雷達(dá)與天線陣列、寬帶無線通信系統(tǒng)、有線電視 CMTS/DOCSIS 3.1 接收機(jī);

- 通信測試儀器、微波接收機(jī)、軟件無線電(SDR)、數(shù)字化儀、醫(yī)療影像診斷設(shè)備。

五、設(shè)計(jì)關(guān)鍵要點(diǎn)

- 電源與去耦 :各電源引腳需就近配置 0.1 μF 陶瓷電容,AVDD3V 引腳額外并聯(lián) 10 μF 電容,降低電源噪聲干擾;

- 信號接口:模擬輸入推薦串聯(lián) 5Ω

10Ω 電阻抑制寄生振蕩,差分傳輸線特性阻抗控制為 50Ω200Ω;JESD204B 輸出需 AC 耦合至接收端,傳輸線特性阻抗 100Ω; - 時鐘設(shè)計(jì):CLKIN 差分時鐘輸入支持 0.7Vpp

1.6Vpp 幅度,建議邊沿斜率≥1 V/ns 以降低孔徑抖動;SYSREF 信號需為 LMFC 時鐘的子諧波(1 MHz5 MHz),確保多芯片同步精度; - 校準(zhǔn)與初始化:上電后需先啟動 IOVDD 再啟動其他電源,執(zhí)行硬件復(fù)位和 PLL 校準(zhǔn),更改抽取率后需重新校準(zhǔn) ADC 核心。

-

變頻器

+關(guān)注

關(guān)注

256文章

7428瀏覽量

155852 -

adc

+關(guān)注

關(guān)注

100文章

7935瀏覽量

556771 -

串行接口

+關(guān)注

關(guān)注

3文章

521瀏覽量

45317 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

4096瀏覽量

130232

發(fā)布評論請先 登錄

ADS54J60IRMPT模數(shù)轉(zhuǎn)換器

MAX815TESA+ 原廠現(xiàn)貨***

LTC2380IDE-24#PBF 現(xiàn)貨

IPP-7026 訂貨***

ADS5485 采樣率200MSPS 16位單通道模數(shù)轉(zhuǎn)換器

AD9268: 16位、80 MSPS/105 MSPS/125 MSPS、1.8 V雙通道模數(shù)轉(zhuǎn)換器(ADC)

ADS5407雙通道12位500Msps模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

ADS5463/ADS54RF63一款12位、500/550 MSPS模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADS5553高性能、雙通道、14位、65 MSPS模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

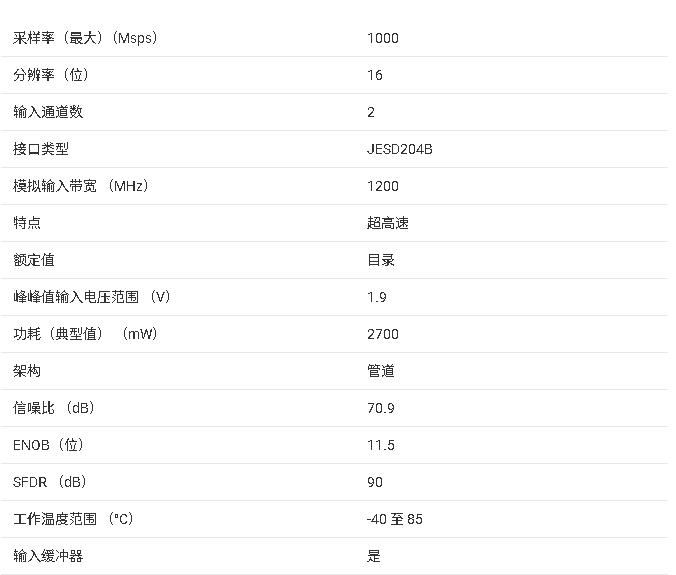

ADS54J60雙通道16位1.0GSPS模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

ADS54J69雙通道、16位、500MSPS模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

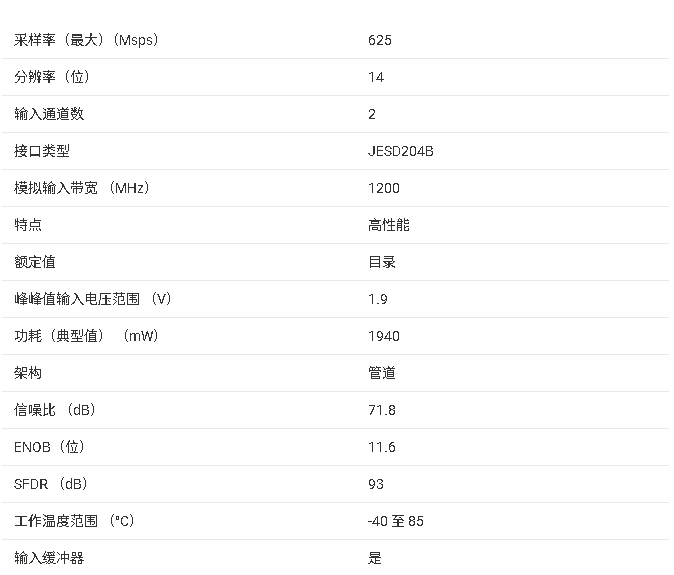

ADS54J42雙通道、14位、625MSPS模數(shù)轉(zhuǎn)換器數(shù)據(jù)表

ADS8363雙通道、16位、1 MSPS模數(shù)轉(zhuǎn)換器(ADC)數(shù)據(jù)表

ADS54J42 14 位 625 MSPS 雙通道模數(shù)轉(zhuǎn)換器(ADC)技術(shù)文檔總結(jié)

ADS54J60 雙通道 16 位 1.0-GSPS 模數(shù)轉(zhuǎn)換器技術(shù)文檔總結(jié)

ADS54J69 16 位 500 MSPS 雙通道模數(shù)轉(zhuǎn)換器(ADC)技術(shù)文檔總結(jié)

ADS54J69 16 位 500 MSPS 雙通道模數(shù)轉(zhuǎn)換器(ADC)技術(shù)文檔總結(jié)

評論